# 3-Phase MOSFET Driver

#### **Features and Benefits**

- 5 to 50 V supply voltage

- Latched TSD with fault output

- Drives six N-channel high current MOSFETs

- Internally controlled synchronous rectification

- Speed voltage input enables internal PWM duty cycle control of full bridge

- Center aligned PWM

- Internal UVLO and crossover current protection

- · Hall switch inputs

- Adjustable dead time protection

- Low power sleep mode for battery-powered applications

## **Description**

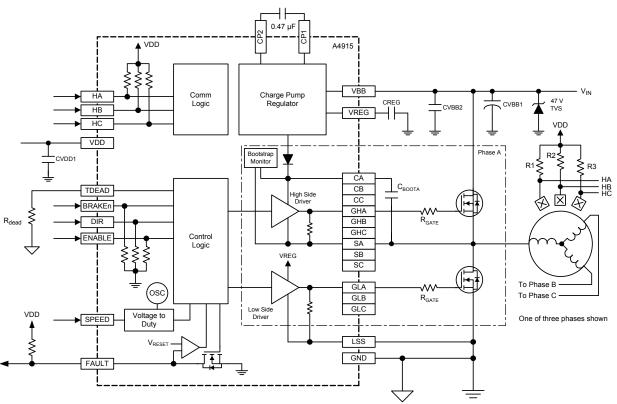

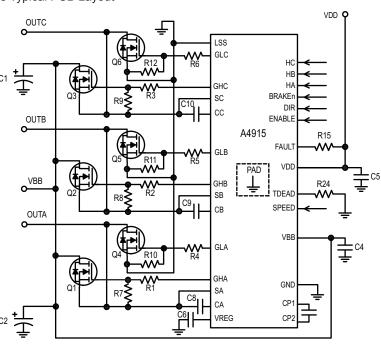

The A4915 is designed for pulse width modulated (PWM) current control of 3-phase brushless DC motors. The A4915 is capable of high current gate drive for 6 all N-channel power MOSFETs. An internal charge pump ensures gate drive down to 7 V supply and provides limited gate drive down to 5 V. A bootstrap capacitor is used to generate a supply voltage greater than the source voltage of the high side MOSFET, required for N-channel MOSFETs.

Internal synchronous rectification control circuitry is provided to improve power dissipation in the external MOSFETs during PWM operation. Internal circuit protection includes latched thermal shutdown, dead time protection, and undervoltage lockout. Special power up sequencing is not required.

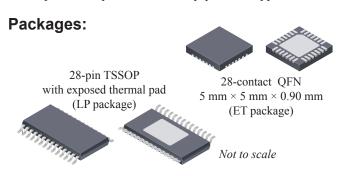

The A4915 is supplied in a 28-pin TSSOP with an exposed thermal pad (suffix LP) and a 28-contact 5 × 5 mm QFN with an exposed thermal pad (suffix ET). These packages are lead (Pd) free, with 100% matte-tin leadframe plating.

## **Functional Block Diagram**

## **Selection Guide**

| Part Number  | Package                                 | Packing*                       |

|--------------|-----------------------------------------|--------------------------------|

| A4915METTR-T | 28-contact QFN with exposed thermal pad | 1500 pieces<br>per 7-in. reel  |

| A4915MLPTR-T | 28-pin TSSOP with exposed thermal pad   | 4000 pieces<br>per 13-in. reel |

#### **Absolute Maximum Ratings**

| Characteristic                             | Symbol               | Notes Rating                                        | Unit |

|--------------------------------------------|----------------------|-----------------------------------------------------|------|

| Load Supply Voltage                        | V <sub>BB</sub>      | -0.3 to 50                                          | V    |

| Logic Supply Voltage                       | V <sub>DD</sub>      | -0.3 to 6                                           | V    |

| VREG Pin                                   | V <sub>REG</sub>     | -0.3 to 16                                          | V    |

| CP1 Pin                                    | V <sub>CP1</sub>     | -0.3 to 16                                          | V    |

| CP2 Pin                                    | V <sub>CP2</sub>     | V <sub>CP1</sub> – 0.3 to<br>V <sub>REG</sub> + 0.3 | V    |

| Logic Inputs                               | V <sub>I</sub>       | -0.3 to 6                                           | V    |

| Hall Inputs                                | V <sub>Hx</sub>      | -0.3 to 6                                           | V    |

| Logic Outputs                              | Vo                   | -0.3 to 6                                           | V    |

| SPEED Input                                | V <sub>SPEED</sub>   | -0.3 to 6                                           | V    |

| CA, CB, and CC Pins                        | V <sub>Cx</sub>      | -0.3 to<br>V <sub>REG</sub> + 50                    | V    |

| GHA, GHB, and GHC Pins                     | V <sub>GHx</sub>     | V <sub>Cx</sub> – 16 to<br>V <sub>CX</sub> + 0.3    | V    |

| SA, SB, and SC Pins                        | V <sub>Sx</sub>      | $V_{Cx}$ – 16 to $V_{Cx}$ + 0.3                     | V    |

| GLA, GLB, GLC Pins                         | $V_{GLx}$            | V <sub>REG</sub> – 16 to 18                         | V    |

| LSS Pin                                    | V <sub>LSS</sub>     | V <sub>REG</sub> – 16 to 18                         | V    |

| Maximum Continuous Junction<br>Temperature | T <sub>J</sub> (max) | 150                                                 | °C   |

| Storage Temperature Range                  | T <sub>stg</sub>     | -55 to 150                                          | °C   |

| Operating Ambient Temperature Range        | T <sub>A</sub>       | -20 to 105                                          | °C   |

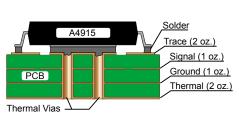

## Thermal Characteristics may require derating at maximum conditions, see application information

| Characteristic             | Symbol         | Test Conditions*                                   | Value | Unit |

|----------------------------|----------------|----------------------------------------------------|-------|------|

| Package Thermal Resistance |                | Package ET, on 4-layer PCB based on JEDEC standard | 32    | °C/W |

|                            | $R_{	heta JA}$ | Package LP, on 4-layer PCB based on JEDEC standard | 28    | °C/W |

<sup>\*</sup>Additional thermal information available on the Allegro website.

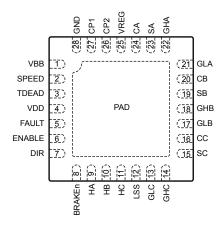

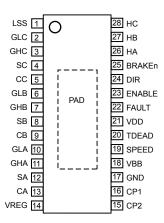

# **Pin-out Diagrams**

ET Package

LP Package

#### **Terminal List Table**

| Name   | Function                              | Number |    | Name | Function                                     |    | nber |

|--------|---------------------------------------|--------|----|------|----------------------------------------------|----|------|

| Name   | Function                              | ET     | LP | Name | Function                                     |    | LP   |

| VBB    | Supply voltage                        | 1      | 18 | SC   | High-side source connection                  | 15 | 4    |

| SPEED  | Reference voltage input               | 2      | 19 | CC   | Bootstrap output phase C                     | 16 | 5    |

| TDEAD  | Terminal for dead time setting        | 3      | 20 | GLB  | Low-side gate drive                          | 17 | 6    |

| VDD    | Logic supply input                    | 4      | 21 | GHB  | High-side gate drive                         | 18 | 7    |

| FAULT  | Fault output                          | 5      | 22 | SB   | High-side source connection                  | 19 | 8    |

| ENABLE | Logic input, PWM control              | 6      | 23 | СВ   | Bootstrap output phase B                     | 20 | 9    |

| DIR    | Logic input, motor direction          | 7      | 24 | GLA  | Low-side gate drive                          | 21 | 10   |

| BRAKEn | Logic input, motor brake (active low) | 8      | 25 | GHA  | High-side gate drive                         | 22 | 11   |

| HA     | Hall input phase A                    | 9      | 26 | SA   | High-side source connection                  | 23 | 12   |

| НВ     | Hall input phase B                    | 10     | 27 | CA   | Bootstrap output phase a                     | 24 | 13   |

| HC     | Hall input phase C                    | 11     | 28 | VREG | Gate drive supply output                     | 25 | 14   |

| LSS    | Sense input                           | 12     | 1  | CP2  | Charge pump capacitor terminal               | 26 | 15   |

| GLC    | Low-side gate drive                   | 13     | 2  | CP1  | Charge pump capacitor terminal               | 27 | 16   |

| GHC    | High-side gate drive                  | 14     | 3  | GND  | Ground                                       | 28 | 17   |

|        |                                       |        |    | PAD  | Exposed pad for enhanced thermal dissipation | _  | _    |

# **ELECTRICAL CHARACTERISTICS** Valid at $T_A = 25$ °C, $V_{BB} = 24$ V; unless otherwise specified

| Characteristic                  | Symbol                   | Test Conditions                                                      | Min.                           | Тур. | Max.     | Unit |

|---------------------------------|--------------------------|----------------------------------------------------------------------|--------------------------------|------|----------|------|

| Supply and Reference            |                          |                                                                      |                                |      | ,        |      |

| Operating Voltage Range         | V <sub>BB</sub>          | Operating, outputs active                                            | 5.0                            | _    | 50       | V    |

|                                 |                          | f <sub>ENB</sub> = 30 kHz, C <sub>LOAD</sub> = 10 nF                 | _                              | 10   | 20       | mA   |

| Materia Occupato Occupant       |                          | $f_{PWM} \approx 20 \text{ kHz, } C_{LOAD} = 10 \text{ nF}$          | _                              | 12   | 24       | mA   |

| Motor Supply Current            | I <sub>BB</sub>          | V <sub>REG</sub> = 13 V, outputs disabled                            | _                              | 3    | 3.5      | mA   |

|                                 |                          | Sleep mode                                                           | _                              | _    | 1        | μΑ   |

| Destatues Diede Ferrend Veltere |                          | I <sub>D</sub> = 10 mA                                               | 0.4                            | 0.7  | 1.0      | V    |

| Bootstrap Diode Forward Voltage | V <sub>fBOOT</sub>       | I <sub>D</sub> = 100 mA                                              | 1.5                            | 2.2  | 2.8      | V    |

| Bootstrap Diode Current Limit   | V <sub>DBOOT</sub>       |                                                                      | 250                            | 500  | 750      | mA   |

| VDD Input Voltage               | V <sub>DD</sub>          |                                                                      | 3                              | _    | 5.5      | V    |

| V/DD 1 10 1                     | I <sub>DDQ</sub>         | ENABLE = high, outputs disabled                                      | _                              | 6    | 10       | mA   |

| VDD Input Current               | I <sub>DDS</sub>         | Sleep mode                                                           | _                              | _    | 10       | μΑ   |

| ENABLE Input Current Sleep Mode | I <sub>ENB(SLP)</sub>    | ENABLE = low for longer than t <sub>SLEEP</sub> ,<br>SPEED = high    | _                              | -    | 1        | μΑ   |

| SPEED Input Current Sleep Mode  | I <sub>SPEED(SLP)</sub>  | ENABLE = high, SPEED = low for longer than t <sub>SLEEP</sub>        | _                              | -    | 1        | μΑ   |

| BRAKEn Input Current Sleep Mode | I <sub>BRAKE(SLP)</sub>  | ENABLE = low for longer than t <sub>SLEEP</sub>                      | _                              | _    | 1        | μA   |

| DIR Input Current Sleep Mode    | I <sub>DIR(SLP)</sub>    | ENABLE = low for longer than t <sub>SLEEP</sub>                      | _                              | _    | 1        | μA   |

| ENABLE Input Frequency Range    | f <sub>ENB</sub>         | V <sub>SPEED</sub> = V <sub>DD</sub>                                 | 1                              | _    | 100      | kHz  |

| Internal PWM Frequency          | f <sub>PWM</sub>         | $V_{\text{ENABLE}} = V_{\text{DD}}$                                  | 14                             | 20   | 26       | kHz  |

| SPEED Input Voltage Range       | V <sub>SPEED</sub>       |                                                                      | 0                              | _    | $V_{DD}$ | V    |

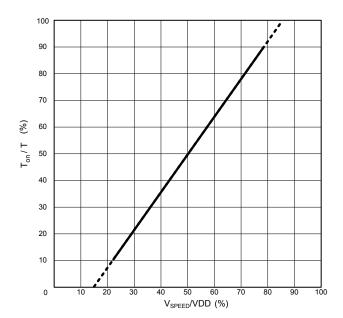

| SPEED Disable Voltage           | V <sub>SPEED(D)</sub>    | Measured as V <sub>SPEED</sub> / V <sub>DD</sub> , duty cycle = 0%   | 10                             | 15   | 20       | %    |

| SPEED Enable Voltage*           | V <sub>SPEED(E)</sub>    | Measured as V <sub>SPEED</sub> / V <sub>DD</sub> , duty cycle = 100% | 79                             | 82   | 86       | %    |

| SPEED Bias Current              | I <sub>SPEED(bias)</sub> | V <sub>SPEED</sub> = V <sub>DD</sub> = 5 V                           | -25                            | 0    | 25       | μΑ   |

|                                 |                          | V <sub>BB</sub> = 9 V                                                | 11.8                           | 13   | 13.75    | V    |

|                                 |                          | V <sub>BB</sub> = 7.5 V                                              | 11.5                           | 13   | 13.75    | V    |

| VREG Output Voltage             | $V_{REG}$                | V <sub>BB</sub> = 6 V                                                | 2 × V <sub>BB</sub><br>- 3.5 V | -    | -        | V    |

|                                 |                          | V <sub>BB</sub> = 5.5 V                                              | 8.0                            | 9.5  | _        | V    |

| Protection                      |                          |                                                                      |                                |      |          |      |

| Thermal Shutdown Temperature    | T <sub>TSD</sub>         | FAULT rising                                                         | 155                            | 170  | 185      | °C   |

| VDEC Undervolter                | V <sub>REGON</sub>       | V <sub>REG</sub> rising                                              | 7.0                            | 7.8  | 8.6      | V    |

| VREG Undervoltage               | V <sub>REGOFF</sub>      | V <sub>REG</sub> falling                                             | 6.39                           | 7.1  | 7.81     | V    |

| VREG Undervoltage Hysteresis    | V <sub>REGhys</sub>      |                                                                      | _                              | 700  | _        | mV   |

Continued on the next page...

**ELECTRICAL CHARACTERISTICS** (continued) Valid at T<sub>A</sub> = 25°C, V<sub>BB</sub> = 24 V; unless otherwise specified

| Characteristic                    | Symbol                 | Test Co                                          | Min.                         | Тур.                   | Max. | Unit                  |    |

|-----------------------------------|------------------------|--------------------------------------------------|------------------------------|------------------------|------|-----------------------|----|

| Protection (continued)            |                        |                                                  |                              |                        |      |                       |    |

| Bootstrap Undervoltage            | V <sub>BOOTUV</sub>    | Measured as a percenta                           | 55                           | _                      | 65   | %                     |    |

| Bootstrap Undervoltage Hysteresis | V <sub>BOOTUVhys</sub> | Measured as a percenta                           | age of V <sub>REG</sub>      | _                      | 20   | _                     | %  |

| VDD 11 1 11                       |                        | V <sub>DD</sub> rising                           |                              | _                      | 2.75 | 2.95                  | V  |

| VDD Undervoltage                  | V <sub>DDUV</sub>      | V <sub>DD</sub> falling                          |                              | 2.45                   | 2.6  | _                     | V  |

| VDD Undervoltage Hysteresis       | V <sub>DDUVhys</sub>   |                                                  |                              | 50                     | 100  | 150                   | mV |

| Sleep Wake-up Delay               | t <sub>WAKE</sub>      |                                                  |                              | _                      | _    | 3                     | ms |

| Gate Drive                        |                        |                                                  |                              |                        |      |                       |    |

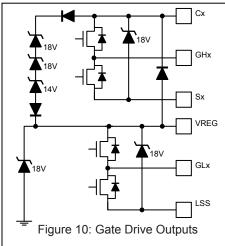

| High Cide Cete Drive Codenit      |                        | C <sub>BOOTx</sub> fully charged, C              | <sub>LOAD</sub> = 10 nF      | V <sub>Cx</sub> - 0.2  | _    | _                     | V  |

| High-Side Gate Drive Output       | V <sub>GHx</sub>       | I <sub>GHx</sub> < 10 μA                         |                              | _                      | _    | V <sub>Sx</sub> + 0.3 | V  |

| Laur Cida Cata Driva Outrut       |                        | V <sub>REG</sub> = 13 V, C <sub>LOAD</sub> = 1   | 0 nF                         | V <sub>REG</sub> - 0.2 | _    | _                     | V  |

| Low-Side Gate Drive Output        | $V_{GLx}$              | I <sub>GLx</sub> < 10 μA                         |                              | _                      | _    | 0.3                   | V  |

| Onto Delivo Della La Desistano    |                        | T <sub>J</sub> = 25°C, I <sub>GHx</sub> = -150 i | 6                            | 9                      | 12   | Ω                     |    |

| Gate Drive Pull-Up Resistance     | R <sub>GHx(ON)UP</sub> | T <sub>J</sub> = 125°C, I <sub>GHx</sub> = -150  | mA                           | _                      | 17   | _                     | Ω  |

| Cata Driva Dull Davin Daviatana   |                        | $T_J = 25^{\circ}C$ , $I_{GLx} = -150$ r         | 2.4                          | 3.5                    | 4.6  | Ω                     |    |

| Gate Drive Pull-Down Resistance   | $R_{GLx(ON)DN}$        | T <sub>J</sub> = 125°C, I <sub>GLx</sub> = -150  | _                            | 5                      | _    | Ω                     |    |

| GHx Passive Pull-Down             | R <sub>GHx(PPD)</sub>  | $V_{GHx} - V_{Sx} < 0.3 V$                       |                              | _                      | 5000 | _                     | Ω  |

| GLx Passive Pull-Down             | R <sub>GLx(PPD)</sub>  | $V_{GLx} - V_{LSS} < 0.3 V$                      |                              | _                      | 5000 | _                     | Ω  |

| Outrout Coultabine Times          | t <sub>rGx</sub>       | 20% to 80%, C <sub>LOAD</sub> = 1                | 0 nF                         | _                      | 200  | _                     | ns |

| Output Switching Time             | t <sub>fGx</sub>       | 80% to 20%, C <sub>LOAD</sub> = 1                | 0 nF                         | _                      | 150  | _                     | ns |

|                                   |                        |                                                  | TDEAD tied to GND            | 10                     | _    | _                     | ns |

| Dood Time                         |                        | Time delay measured                              | R <sub>TDEAD</sub> = 12 kΩ   | _                      | 150  | _                     | ns |

| Dead Time                         | t <sub>DEAD</sub>      | from turn-off to turn-on                         | R <sub>TDEAD</sub> = 64 kΩ   | 800                    | 925  | 1050                  | ns |

|                                   |                        |                                                  | $R_{TDEAD}$ = 220 k $\Omega$ | _                      | 2.9  | -                     | μs |

| Logic I/O                         |                        |                                                  |                              |                        |      |                       |    |

| Logic Input Voltage               | $V_{IN(H)}$            | BRAKEn, DIR, ENABLE                              | E UA UD and UC nine          | 0.7 × V <sub>DD</sub>  | -    | _                     | V  |

| Logic iriput voltage              | V <sub>IN(L)</sub>     | DRAKEII, DIK, ENABLE                             | E, HA, HB, allu HC pills     | -                      | _    | 0.3 × V <sub>DD</sub> | V  |

| Logic Input Current               | I <sub>IN(H)</sub>     | V <sub>IN</sub> = high                           | -                            | 10                     | -    | μA                    |    |

| Logic Input Current               | I <sub>IN(L)</sub>     | V <sub>IN</sub> = Iow, ENABLE = Io               | -1                           | 0                      | 1    | μΑ                    |    |

| FAULT Output Voltage              | V <sub>FAUIT</sub>     | No fault present, I <sub>SINK</sub> =            | 1mA                          | -                      | -    | 0.2                   | V  |

| ENABLE and SPEED Sleep Timer      | +                      | ENABLE = low, SPEED                              | = high                       | 1                      | 2    | 3                     | ms |

| LIANDLE and SPLED Sleep Hiller    | t <sub>SLEEP</sub>     | ENABLE = high, SPEE                              | O = low                      | 1                      | 2    | 3                     | ms |

Continued on the next page...

5

## **ELECTRICAL CHARACTERISTICS** (continued) Valid at T<sub>A</sub> = 25°C, V<sub>BB</sub> = 24 V; unless otherwise specified

| Characteristic                 | Symbol                  | Test Conditions                                                   | Min. | Тур. | Max. | Unit |

|--------------------------------|-------------------------|-------------------------------------------------------------------|------|------|------|------|

| Logic I/O (continued)          |                         |                                                                   |      |      |      |      |

| SPEED Sleep Threshold          | V <sub>SPEEDSLPth</sub> | SPEED = low for longer than t <sub>SLEEP</sub>                    | _    | _    | 295  | mV   |

| Fault Latch Reset Voltage      | V <sub>RESET</sub>      | Fault is present, outputs latched                                 | _    | _    | 0.8  | V    |

| Fault Latch Reset Pulse Time   | t <sub>FAULT</sub>      | Fault is present, outputs latched                                 | 12   | _    | -    | μs   |

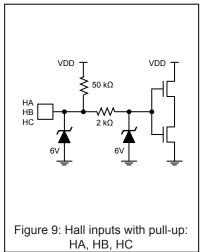

| Hall Input Pull-Up Resistor    | R <sub>Hx(PU)</sub>     | Hx pins, V <sub>IN</sub> = 0 V                                    | _    | 100  | _    | kΩ   |

| Hall Input Current             | I <sub>HALL</sub>       | Hx pins, V <sub>IN</sub> = 5 V                                    | _    | 0    | 1    | μΑ   |

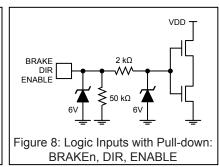

| Logic Input Pull-Down Resistor | R <sub>IN(PD)</sub>     | ENABLE, DIR, BRAKEn, V <sub>IN</sub> = 5 V                        | _    | 50   | -    | kΩ   |

| Login Input Current Sleep Mode | I <sub>IN(SLP)</sub>    | ENABLE, DIR, BRAKEn                                               | _    | _    | 1    | μΑ   |

|                                | t <sub>pd(on)</sub>     | DIR or BRAKEn input to output change,<br>C <sub>LOAD</sub> = 0 nF | _    | -    | 1200 | ns   |

| Propagation Delay              | μ-(σ)                   | ENABLE input to output change, C <sub>LOAD</sub> = 0 nF           | _    | -    | 900  | ns   |

| Propagation Delay              | t <sub>pd(off)</sub>    | DIR or BRAKEn input to output change, C <sub>LOAD</sub> = 0 nF    | _    | _    | 1200 | ns   |

|                                | F 4 (0.1.)              | ENABLE input to output change, C <sub>LOAD</sub> = 0 nF           | _    | _    | 900  | ns   |

| Input Din Clitch Doingt        | +                       | ENABLE                                                            | _    | _    | 900  | ns   |

| Input Pin Glitch Reject        | tglitch                 | DIR, BRAKEn                                                       | _    | _    | 1000 | ns   |

<sup>\*</sup>Output duty cycle limited by  $t_{\mbox{\scriptsize DEAD}}.$

## **Functional Description**

## **Basic Operation**

The A4915 is a 3-phase MOSFET driver intended to drive high current MOSFETs. It is designed for use in battery operated equipment where low-voltage operation is critical. The A4915 also features a low current sleep mode which disables the device and draws minimum supply current. The A4915 is capable of driving 6 N-channel MOSFETs. Commutation logic includes Enable, Direction, and Brake modes for external PWM control.

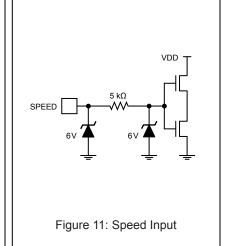

A Speed input is provided which allows an external source to PWM the bridge at 30 kHz typical. The PWM duty cycle is controlled by applying an analog voltage to the SPEED pin from 0 V to  $V_{DD}$ .

#### **Pin Descriptions**

**DIR** The Direction pin is used to change the commutation direction of the 3 bridges. Refer to Table 1 for phase commutation information.

**ENABLE** The ENABLE input terminal allows external PWM control. Setting ENABLE high turns on the selected sink-source pair, and setting it low switches off the appropriate drivers and the load current decays. If external PWM is used, the SPEED pin must be tied to VDD.

When the ENABLE input is held low for longer than  $t_{\rm SLEEP}$  the A4915 turns off all internal circuitry and draws minimum current

from the supply. When coming out of sleep allow 3 ms for the charge pump regulator to stabilize.

**SPEED** The duty cycle of the internally generated carrier frequency is controlled by applying a DC voltage on the SPEED input. A plot showing the relationship of Speed to duty cycle is shown in Figure 1. When SPEED is pulled directly to VDD the internal carrier is disabled and the Enable input can be used to PWM the bridge. When  $V_{SPEED} < V_{SPEED(D)}$  the output is guaranteed to be 0%. When  $V_{SPEED} > V_{SPEED(E)}$  the output is guaranteed to be 100%.

**BRAKEn** Brake mode turns all three sink drivers on and effectively shorts out the motor generated BEMF. The BRAKEn input overrides the ENABLE and SPEED inputs except when in Sleep mode. Refer to Table 2 for the logic truth table. In order to comply with Failure Mode Effects and Analysis (FMEA), the brake function is normally active (logic low). If the BRAKEn pin on the device is open due to some failure of solder joint or microprocessor failure, the device will automatically implement Brake mode, preventing the motor from turning or pumping up the supply. Applying logic high to the BRAKEn terminal deactivates Brake mode and allows normal operation.

Care must be taken when applying the Brake command because large currents can be generated. The user must ensure that the maximum ratings of the MOSFETs are not exceeded under worst

**Table 1: Commutation Table**

|            | НА | НВ | нс | DIR | GLA | GLB | GLC | GHA | GHB | GHC | SA   | SB   | sc   |

|------------|----|----|----|-----|-----|-----|-----|-----|-----|-----|------|------|------|

| 1          | 1  | 0  | 1  | 1   | 0   | 0   | 1   | 1   | 0   | 0   | High | _    | Low  |

| 2          | 1  | 0  | 0  | 1   | 0   | 0   | 1   | 0   | 1   | 0   | _    | High | Low  |

| 3          | 1  | 1  | 0  | 1   | 1   | 0   | 0   | 0   | 1   | 0   | Low  | High | _    |

| 4          | 0  | 1  | 0  | 1   | 1   | 0   | 0   | 0   | 0   | 1   | Low  | _    | High |

| 5          | 0  | 1  | 1  | 1   | 0   | 1   | 0   | 0   | 0   | 1   | _    | Low  | High |

| 6          | 0  | 0  | 1  | 1   | 0   | 1   | 0   | 1   | 0   | 0   | High | Low  | _    |

| 1          | 1  | 0  | 1  | 0   | 1   | 0   | 0   | 0   | 0   | 1   | Low  | _    | High |

| 2          | 1  | 0  | 0  | 0   | 0   | 1   | 0   | 0   | 0   | 1   | -    | Low  | High |

| 3          | 1  | 1  | 0  | 0   | 0   | 1   | 0   | 1   | 0   | 0   | High | Low  | -    |

| 4          | 0  | 1  | 0  | 0   | 0   | 0   | 1   | 1   | 0   | 0   | High | _    | Low  |

| 5          | 0  | 1  | 1  | 0   | 0   | 0   | 1   | 0   | 1   | 0   | _    | High | Low  |

| 6          | 0  | 0  | 1  | 0   | 1   | 0   | 0   | 0   | 1   | 0   | Low  | High | _    |

| Hall Fault | 1  | 1  | 1  | Х   | 0   | 0   | 0   | 0   | 0   | 0   | _    | _    | _    |

| Hall Fault | 0  | 0  | 0  | Х   | 0   | 0   | 0   | 0   | 0   | 0   | -    | _    | -    |

1.508.853.5000: www.allegromicro.com

case braking conditions. Maximum motor current during Brake mode can be approximated by:

$$I_{\text{BRAKEn}} = V_{\text{BEMF}} / R_{\text{L}}$$

where  $V_{BEMF}$  is the voltage generated by the motor and  $R_{L}$  is the resistance of the phase winding.

**VREG** A regulated voltage output that is used to supply the low-side gate drivers and to charge the bootstrap capacitors.

**FAULT** The Fault output is active high. Under normal operation the open drain output pulls the Fault output to ground. When a fault occurs the open drain output is released, and the Fault output is then pulled to a logic high through a connected external passive pullup resistor. Fault conditions are shown in Table 3.

The presence of an invalid Hall combination is referred to as a *Hall Fault*. Invalid Hall combinations are documented in Table 1. When a Hall Fault is present, the outputs are disabled. Invalid Hall Faults are not latched, and do not affect the state of the FAULT pin. Latched faults that result in disabled outputs can be reset in a number of ways:

- A UVLO on VDD will serve as a reset

- If the device is put into sleep mode the latch is reset

- A microprocessor can create a reset on the FAULT pin directly by forcing  $V_{RESET}$  on the FAULT pin when a fault is active for longer than  $t_{FAULT}$  (that is, when the outputs are latched)

**LSS** The LSS terminal is the low-side drain connection for the MOSFET. If an external PWM current control loop is used, a low

Figure 1: Speed in Relation to Duty Cycle

**Table 3: Fault Conditions**

|    | Event        | Fault Pin | Outputs  | Latched |

|----|--------------|-----------|----------|---------|

|    | TSD          | High      | Disabled | Yes     |

|    | SLEEP        | High      | Disabled | No      |

| U١ | VLO VREG/VDD | High      | Disabled | No      |

|    | Invalid Hall | Low       | Disabled | No      |

**Table 2: Input Logic Truth Table**

|                                    | Inputs                                                       |        | Mada of Occupation                                                          |

|------------------------------------|--------------------------------------------------------------|--------|-----------------------------------------------------------------------------|

| ENABLE                             | SPEED                                                        | BRAKEn | Mode of Operation                                                           |

| Low                                | High                                                         | High   | PWM chop slow decay synchronous rectification (center aligned)              |

| Low                                | High                                                         | Low    | Brake mode – All low-side gates on                                          |

| High                               | High                                                         | High   | Selected drivers on <sup>b</sup>                                            |

| High                               | High                                                         | Low    | Brake mode – All low-side gates on                                          |

| High                               | $V_{DD} \times V_{SPEED(E)}$ to $V_{DD} \times V_{SPEED(D)}$ | High   | PWM chop slow decay synchronous rectification (center aligned) <sup>c</sup> |

| High                               | > V <sub>DD</sub> × V <sub>SPEED(E)</sub>                    | High   | Selected drivers on <sup>b</sup>                                            |

| High                               | < V <sub>DD</sub> × V <sub>SPEED(D)</sub>                    | High   | PWM chop slow decay synchronous rectification (center aligned)              |

| Low longer than t <sub>SLEEP</sub> | High                                                         | Χa     | Sleep mode – coast                                                          |

| High                               | Low longer than t <sub>SLEEP</sub>                           | Χa     | Sleep mode – coast                                                          |

aX = don't care.

1.508.853.5000; www.allegromicro.com

bMaximum and minium duty cycle limited by boot capacitor charge management.

cInternal PWM active.

value sense resistor can be placed from LSS to ground for current sensing purposes. The resistor should be chosen so that the DC voltage across the sense resistor is between 200 mV and 500 mV. If a sense resistor is not used then LSS should be connected directly to power ground.

**CA, CB, CC** High-side connections for the bootstrap capacitors (CBOOTx) and positive supply for high-side gate drive.

**GHA, GHB, GHC** High-side gate drive outputs for N-channel MOSFETs.

**SA**, **SB**, **SC** Motor phase connections, serve as the negative supplies for the high-side gate drive.

**GLA, GLB, GLC** Low-side gate drive outputs for N-channel MOSFETs.

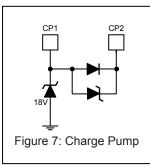

**CP1**, **CP2** Connections for the charge pump switching capacitor. Typical capacitance should be  $0.47 \mu F$ .

**HA**, **HB**, **HC** Hall input connections from Hall switches at the motor.

#### **Thermal Shutdown**

If the die temperature exceeds  $T_{TSD}$ , the FAULT output is turned off and the outputs are disabled. Thermal shutdown is a latched fault.

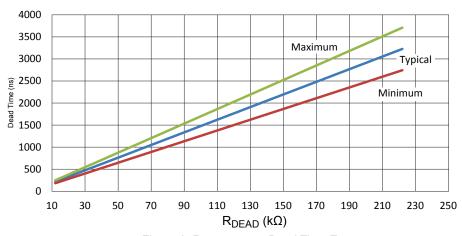

#### **Dead Time**

To prevent cross-conduction (shoot through) in any phase of the bridge, it is necessary to have a dead time,  $t_{\rm DEAD}$ , between a high- or low-side turn-off and the next complementary turn-on event. The dead time for all three phases is set by a single dead

time resistor (R<sub>DEAD</sub>) between the TDEAD pin and ground.

For  $R_{DEAD}$  values between 12 and 220 k $\Omega$ , at 25°C the nominal value of  $t_{DEAD}$  in ns can be approximated by:

$$t_{\rm DEAD} = 40 + (1.28^{-2} \times R_{\rm DEAD})$$

Current,  $I_{DEAD}$ , can be calculated by:

$$I_{\text{DEAD}} = 1.2 / R_{\text{DEAD}}$$

As values for R increase, current offsets and resistor mismatch cause the error terms to increase. Figure 2 shows the typical expected error for a given  $R_{\rm DEAD}$  value.

#### Sleep Mode

The A4915 has a low-current Sleep mode to limit current draw on the battery. When in low-current Sleep mode (when ENABLE = low for longer than  $t_{\rm SLEEP}$  and SPEED = high), current into VBB and VDD is less than 1  $\mu$ A.

When ENABLE is held low for longer than  $t_{\rm SLEEP}$  and the SPEED input is held high, the pull-up resistors on the Hall inputs and the pull-down resistor on the BRAKEn pin are open-circuited to minimize current draw into logic input terminals. Only the condition where SPEED = high and ENABLE = low for longer than  $t_{\rm SLEEP}$  results in low current on logic input terminals.

#### Center Aligned PWM

The A4915 features center aligned PWM, which improves power dissipation and helps reduce EMI. During an off-time triggered by either an internal PWM or by an external Enable chop command, current recirculation will be in either the high-side FETs or the low-side FETs, depending on the state of an internal latch. On each bridge Enable command, the latch is reset

Figure 2: R<sub>DEAD</sub> versus Dead Time Error

1.508.853.5000; www.allegromicro.com

and the current recirculation shifts from high-side recirculation to low-side recirculation.

This method of recirculation shifts 50% of the power to the high-side drivers during the off-time, reducing the power dissipation in the sink drivers. Reducing the overall temperature of the output drivers by sharing power between the 6 FETs improves system efficiency and battery life.

#### Internal/External PWM

The A4915 can be pulse width modulated (PWM) to control current. There are two methods by which PWM can be applied to the device.

- External PWM. This method requires a PWM signal be applied to the ENABLE pin. When the SPEED pin is tied directly to VDD, the ENABLE pin can be chopped from 0 to 100%. If the ENABLE input is held low for more than sleep timer, t<sub>SLEEP</sub>, the device enters low current sleep mode.

- Internal PWM. This method uses the internally generated PWM, which is controlled by applying a DC voltage to the SPEED pin.

When the ENABLE pin is tied directly to VDD, the speed can be controlled from 0 to 100%. See the SPEED pin description for further information.

For complete description of all operating conditions, see Table 2.

#### Synchronous Rectification

When a PWM off-time cycle is triggered by an ENABLE chop command or by an internal PWM off-time, load current recirculates. The A4915 synchronous rectification feature will turn on the appropriate MOSFETs during the off-time and effectively short out the body diodes with the low  $R_{SD(on)}$  driver. This will lower power dissipation significantly and eliminates the need for external Schottky diodes.

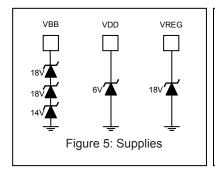

#### **Charge Pump Regulator**

The gate drives for the low-side MOSFETs and the bootstrap charge for the high-side drivers is accomplished by the charge pump regulator. For  $V_{BB}$  above 16 V, the regulator acts as a linear regulator. Below 16 V, the regulated supply is maintained by a charge pump boost converter that requires a pump capacitor between CP1 and CP2.

The regulated voltage VREG is decoupled on the VREG terminal. The decoupling capacitance is based on the bootstrap capacitor which is dependent on the MOSFET selection. Refer to the Application Information section for details on correct sizing of VREG and bootstrap capacitors.

#### **Gate Drive and RGATE**

The gate drive for the external MOSFETs is capable of providing the large current transients needed to quickly charge and discharge the gate capacitance to maintain fast switching speeds and minimal power dissipation. The low-side driver current is sourced by the capacitor on the VREG terminal. The high-side gate drive current is supplied by the respective bootstrap capacitance connected between the Cx and Sx terminals. The charge and discharge of the gate can be controlled by using an external resistor  $(R_{\rm GATE})$  in series with the gate.

## **Bootstrap Charge Management**

In order to protect the external MOSFETs from insufficient gate drive, it is important that the bootstrap capacitor voltage be monitored. Before a high-side switch is allowed to turn on, it must have sufficient charge on the bootstrap capacitor. If the voltage on the bootstrap capacitor is below the turn-on voltage limit, the A4915 will attempt to charge the bootstrap capacitor by turning on the associated low-side driver. The bootstrap monitor stays active during the duration of the switch on-time. If the voltage falls out of compliance at any time when the high-side driver is enabled, the driver is disabled and the low-side switch is activated to charge the bootstrap capacitor.

During normal operation and in conditions where the PWM duty cycle creates short off-times, the low-side switch may be activated more often to keep sufficient charge on the bootstrap capacitor. Proper sizing of the bootstrap and VREG capacitors is critical to being able to maintain effective gate drive. Refer to the Application Information section for details on correct sizing of VREG and bootstrap capacitors.

## **Application Information**

#### **Bootstrap Capacitor Selection**

In order to properly size the capacitor CBOOT, the total gate charge must be known. Too large a bootstrap capacitor and the charge time will be long, resulting in maximum duty cycle limitation. Too small a capacitor and the voltage ripple will be large when charging the gate.

Size the CBOOT capacitor such that the charge,  $Q_{BOOT}$ , is 20 times larger than the required charge for the gate of the MOSFET,  $Q_{GATE}$ :

$$C_{\mathrm{BOOT}} = (Q_{\mathrm{GATE}} \times 20) / V_{\mathrm{BOOT}}$$

where  $V_{BOOT}$  is the voltage across the bootstrap capacitor. The voltage drop across the bootstrap capacitor as the MOSFET gate is being charged,  $\Delta V$ , can be approximated by:

$$\Delta V = Q_{\text{GATE}} / C_{\text{BOOT}}$$

For the bootstrap capacitor, a ceramic type rated at 16 V or larger should be used.

#### **VREG Capacitor Selection**

VREG is responsible for providing all the gate charge for the low side MOSFETs and for providing all the charge current for the three bootstrap capacitors. For these purposes, the VREG capacitor,  $C_{REG}$ , should be 20 times the value of  $C_{BOOT}$ :

$$C_{\text{REG}} = 20 \times C_{\text{BOOT}}$$

#### **Layout Recommendations**

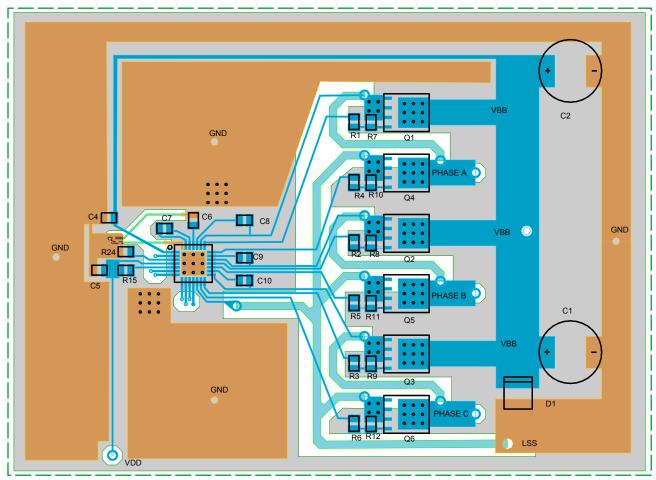

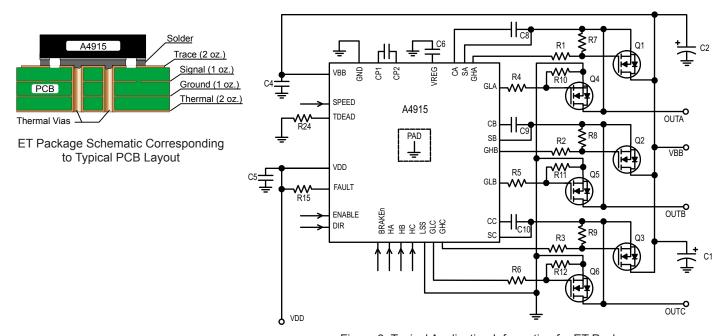

Careful consideration must be given to PCB layout when designing high frequency, fast-switching, high-current circuits (refer to Figures 3 and 4):

• The A4915 ground, GND, and the high-current return of the external MOSFETs should return separately to the negative side of

the motor supply filtering capacitor. This minimizes the effect of switching noise on the A4915.

- The exposed thermal pad should be connected to GND.

- Minimize stray inductance by using short, wide copper traces at the drain and source terminals of all power MOSFETs. This includes motor lead connections, the input power bus, and the common source of the low-side power MOSFETs. This minimizes voltages induced by fast switching of large load currents.

- Consider the use of small (100 nF) ceramic decoupling capacitors across the source and drain of the power MOSFETs, to limit fast transient voltage spikes caused by inductance in the traces.

- Keep the gate discharge return connections Sx and LSS as short as possible. Any inductance on these traces causes negative transitions on the corresponding A4915 terminals, which may exceed the Absolute Maximum Ratings. If this is likely, consider the use of clamping diodes to limit the negative excursion on these terminals with respect to GND.

- Supply decoupling for VBB, VREG, and VDD should be connected independently, close to the GND terminal. The decoupling capacitors should also be connected as close as possible to the relevant supply terminal.

- Gate charge drive paths and gate discharge return paths may carry large transient current pulses. Therefore the traces from GHx, GLx, Sx (x = A, B, or C) and LSS should be as short as possible to reduce the inductance of the trace.

- Provide an independent connection from LSS to the common point of the power bridge. This can be the negative side of the motor supply filtering capacitor or one end of a sense resistor. It is not recommended to connect LSS directly to the GND terminal, as this may increase the noise at the digital inputs.

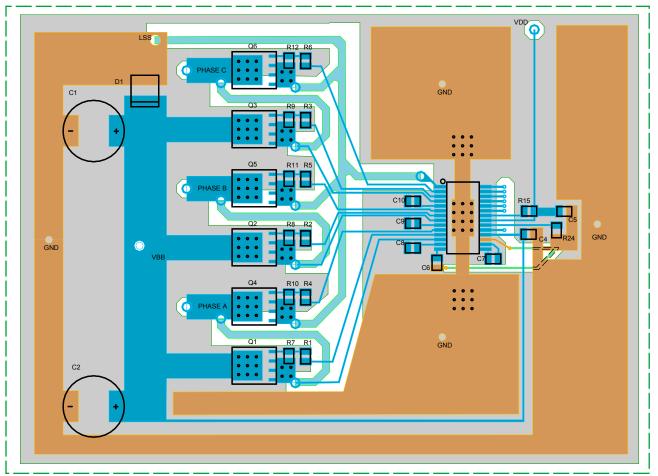

ET Package Typical PCB Layout

Figure 3: Typical Application Information for ET Package

# 3-Phase MOSFET Driver

LP Package Typical PCB Layout

LP Package Schematic Corresponding to Typical PCB Layout

Figure 4: Typical application information for LP package

# **Input / Output Structures**

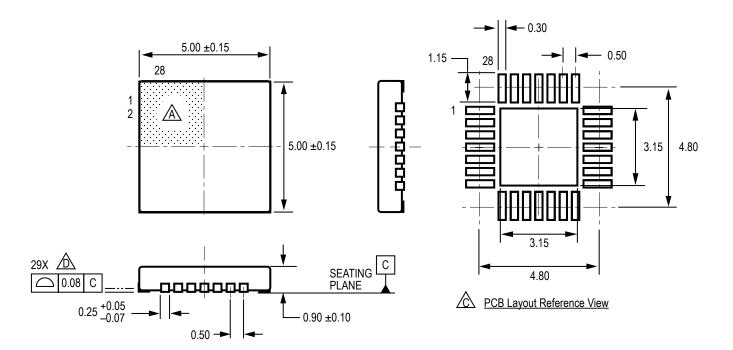

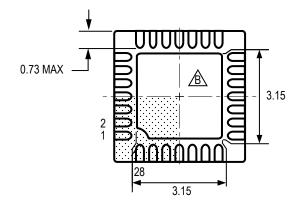

## Package ET, 28-Pin QFN with Exposed Thermal Pad

For Reference Only; not for tooling use (reference JEDEC MO-220VHHD-1)

Dimensions in millimeters

Exact case and lead configuration at supplier discretion within limits shown

A Terminal #1 mark area

Exposed thermal pad (reference only, terminal #1 identifier appearance at supplier discretion)

Reference land pattern layout (reference IPC7351 QFN50P500X500X100-29V1M);

All pads a minimum of 0.20 mm from all adjacent pads; adjust as necessary to meet application process requirements and PCB layout tolerances; when mounting on a multilayer PCB, thermal vias at the exposed thermal pad land can improve thermal dissipation (reference EIA/JEDEC Standard JESD51-5)

Coplanarity includes exposed thermal pad and terminals

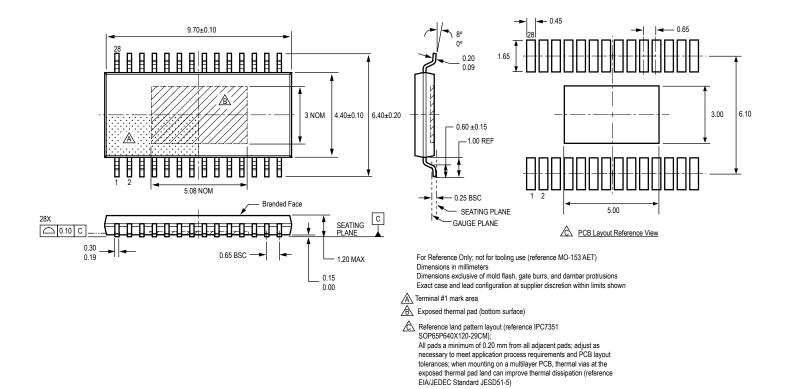

# Package LP, 28-Pin TSSOP with Exposed Thermal Pad

A4915

# 3-Phase MOSFET Driver

#### **Revision History**

| Revision | Current<br>Revision Date | Description of Revision                                     |

|----------|--------------------------|-------------------------------------------------------------|

| 1        | April 1, 2013            | Update EC table parameters                                  |

| 2        | March 6, 2014            | Update Absolute Maximum Ratings table and content on page 9 |

| 3        | April 25, 2014           | Revised Schematics on pp. 12 and 13                         |

Copyright ©2012-2014, Allegro MicroSystems, LLC

Allegro MicroSystems, LLC reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, LLC assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

www.allegromicro.com