## 3.3V $2M \times 8/1M \times 16$ CMOS synchronous DRAM

### **Features**

- Organization

- 1,048,576 words  $\times$  8 bits  $\times$  2 banks (2M  $\times$  8) 11 row, 9 column address

- 524,288 words  $\times$  16 bits  $\times$  2 banks (1M  $\times$  16) 11 row, 8 column address

- All signals referenced to positive edge of clock, fully synchronous

- Dual internal banks controlled by A11 (bank select)

- High speed

- 143/125/100 MHz

- 7/8/10 ns clock access time

- Low power consumption

- Active: 576 mW max

- Standby: 7.2 mW max, CMOS I/O

- 2048 refresh cycles, 32 ms refresh interval

- 4096 refresh cycles, 64 ms refresh interval

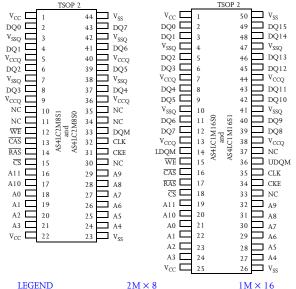

### Pin arrangement

| LEGEND         | 21VL × 8                     | 11VI X 16                       |

|----------------|------------------------------|---------------------------------|

| Configuration  | $1M \times 8 \times 2$ banks | $512K \times 16 \times 2$ banks |

| Refresh Count  | 2K/4K                        | 2K/4K                           |

| Row Address    | (A0 - A10)                   | (A0 - A10)                      |

| Bank Address   | 2 (BA)                       | 2 (BA)                          |

| Column Address | 512 (A0 – A8)                | 256 (A0 – A7)                   |

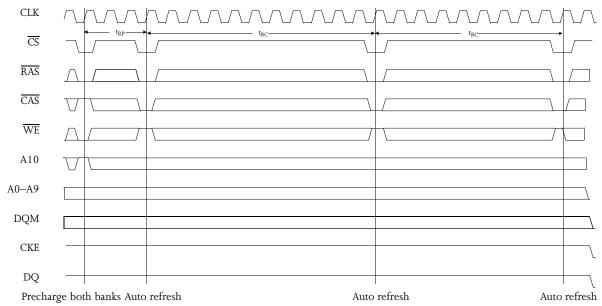

- Auto refresh and self refresh

- PC100 functionality

- Automatic and direct precharge including concurrent autoprecharge

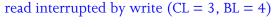

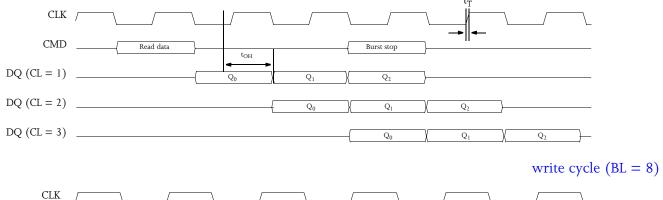

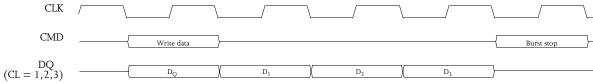

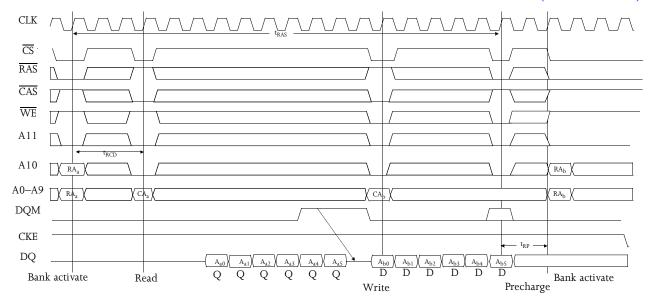

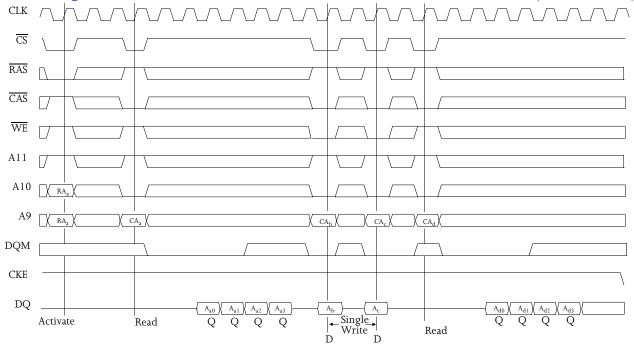

- Burst read, write/Single write

- Random column address assertion in every cycle, pipelined operation

- LVTTL compatible I/O

- 3.3V power supply

- JEDEC standard package, pinout and function

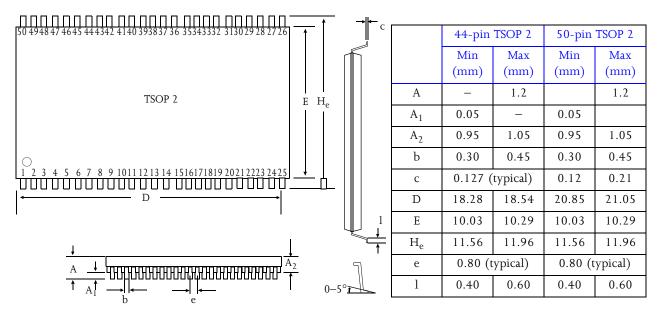

- 400 mil, 44-pin TSOP 2 (2 $M \times 8$ )

- 400 mil, 50-pin TSOP 2 ( $1M \times 16$ )

- Read/write data masking

- Programmable burst length (1/2/4/8/ full page)

- Programmable burst sequence (sequential/interleaved)

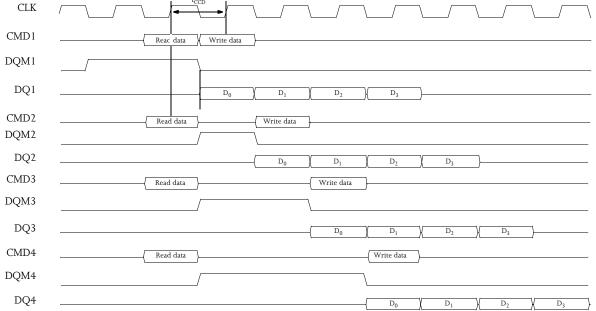

- Programmable  $\overline{CAS}$  latency (1/2/3)

### Pin designation

| Pin(s)                                            | Description                                                                                           |  |  |  |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|

| DQM $(2M \times 8)$<br>UDQM/LDQM $(1M \times 16)$ | Output disable/write mask                                                                             |  |  |  |

| A0 to A10                                         | $ \begin{array}{c} RA0-10 \\ Address inputs & CA0-7 \ (\times 16) \\ CA0-8 \ (\times 8) \end{array} $ |  |  |  |

| A11                                               | Bank address (BA)                                                                                     |  |  |  |

| DQ0 to DQ7 (2M × 8)<br>DQ0 to DQ15 (1M × 16)      | Input/output                                                                                          |  |  |  |

| RAS                                               | Row address strobe                                                                                    |  |  |  |

| CAS                                               | Column address strobe                                                                                 |  |  |  |

| WE                                                | Write enable                                                                                          |  |  |  |

| CS                                                | Chip select                                                                                           |  |  |  |

| V <sub>CC</sub> , V <sub>CCQ</sub>                | Power $(3.3V \pm 0.3V)$                                                                               |  |  |  |

| V <sub>SS</sub> , V <sub>SSQ</sub>                | Ground                                                                                                |  |  |  |

| CLK                                               | Clock input                                                                                           |  |  |  |

| CKE                                               | Clock enable                                                                                          |  |  |  |

### Selection guide

|                                                                      | Symbol           | -7  | -8  | -10 | Unit |

|----------------------------------------------------------------------|------------------|-----|-----|-----|------|

| Bus frequency (CL = 3)                                               | $f_{ m Max}$     | 143 | 125 | 100 | MHz  |

| Maximum clock access time (CL = 3)                                   | t <sub>AC</sub>  | 5.5 | 6   | 6   | ns   |

| Minimum input setup time                                             | $t_{S}$          | 2   | 2   | 2   | ns   |

| Minimum input hold time                                              | t <sub>H</sub>   | 1.0 | 1.0 | 1.0 | ns   |

| Row cycle time ( $CL = 3$ , $BL = 1$ )                               | t <sub>RC</sub>  | 70  | 80  | 80  | ns   |

| Maximum operating current ([ $\times$ 16], RD or WR, CL = 3), BL = 2 | I <sub>CC1</sub> | 130 | 100 | 100 | mA   |

| Maximum CMOS standby current, self refresh                           | I <sub>CC6</sub> | 1   | 1   | 1   | mA   |

### Functional description

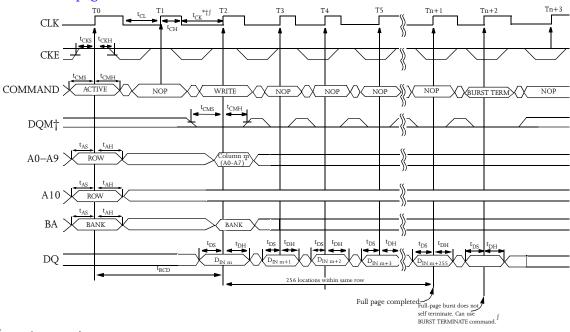

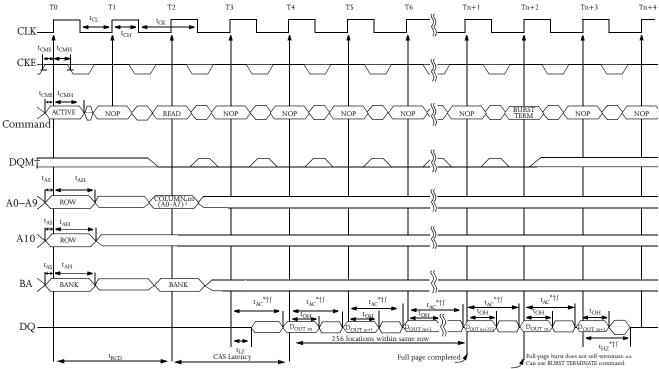

The AS4LC2M8S1, AS4LC2M8S0, and AS4LC1M16S1, AS4LC1M16S0 are high-performance 16-megabit CMOS Synchronous Dynamic Random Access Memory (SDRAM) devices organized as 1,048,576 words × 8 bits × 2 banks (2048 rows × 512 columns) and 524,288 words × 16 bits × 2 banks (2048 rows × 256 columns), respectively. Very high bandwidth is achieved using a pipelined architecture where all inputs and outputs are referenced to the rising edge of a common clock. Programmable burst mode can be used to read up to a full page of data (512 bytes for  $2M \times 8$  and 256 bytes for  $1M \times 16$ ) without selecting a new column address.

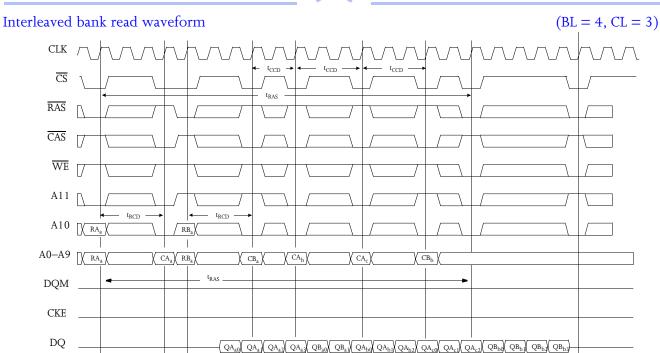

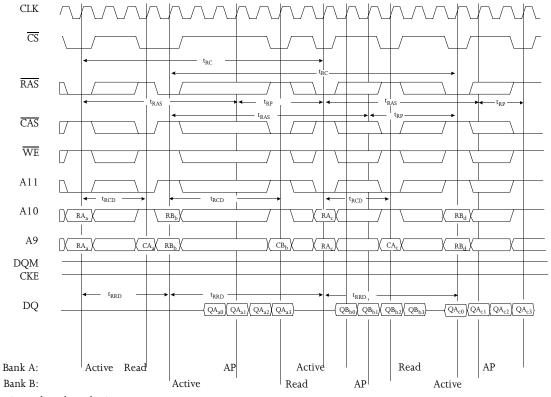

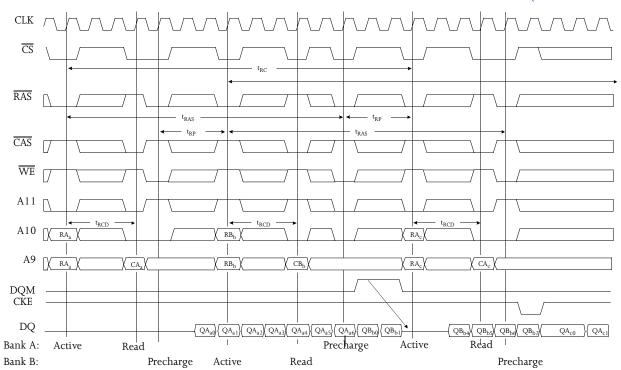

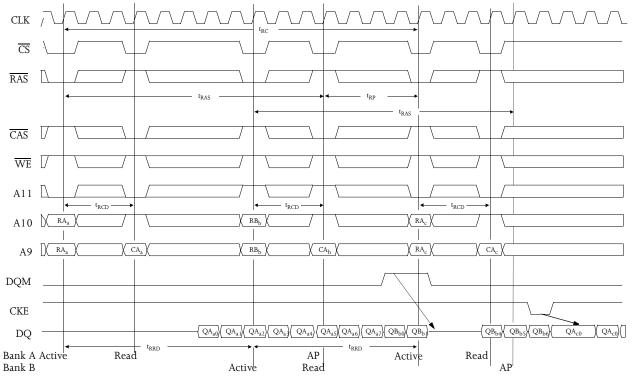

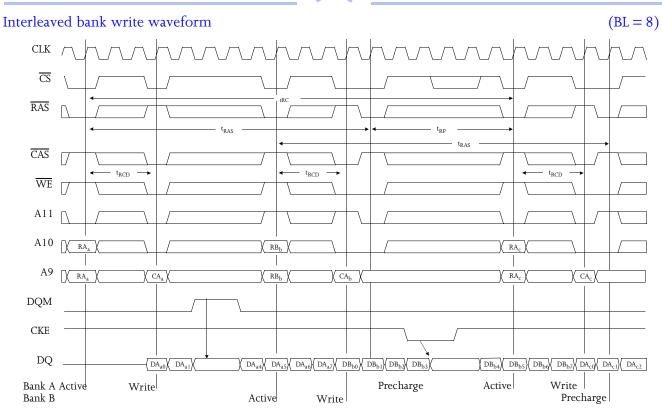

The operational advantages of an SDRAM are as follows: (1) the ability to synchronously output data at a high clock frequency with automatic increments of column-address (burst access); (2) bank-interleaving, which hides precharge time and attains seamless operation; and (3) the capability to change column-address randomly on every clock cycle during burst access.

This SDRAM product also features a programmable mode register, allowing users to select read latency as well as burst length and type (sequential or interleaved). Lower latency improves first data access in terms of CLK cycles, while higher latency improves maximum frequency of operation. This feature enables flexible performance optimization for a variety of applications.

SDRAM commands and functions are decoded from control inputs. Basic commands are as follows:

• Mode register set

- Deactivate bank

- Deactivate all banks

- Select row; activate bank

- Select column; write

- Select column: read

- Deselect; power down

- CBR refresh

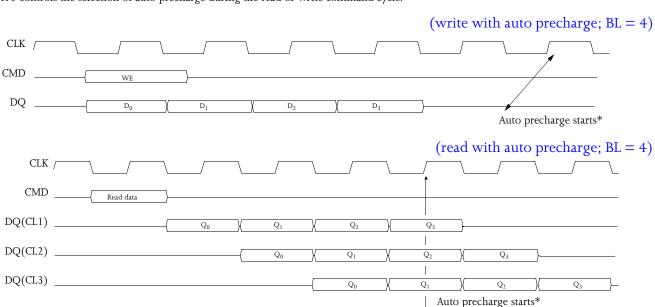

- Auto precharge with read/write

- Self-refresh

Both devices are available in 400-mil plastic TSOP type 2 package. The AS4LC2M8S1 / AS4LC2M8S0 have 44 pins, and the AS4LC1M16S1 / AS4LC1M16S0 have 50 pins. All devices operate with a power supply of 3.3V ± 0.3V. Multiple power and ground pins are provided for low switching noise and EMI. Inputs and outputs are LVTTL compatible.

## Logic block diagram

† For AS4LC2M8S1/AS4LC2M8S0, Banks A and B will read  $1M \times 8$  (2048  $\times$  512  $\times$  8).

Pin descriptions

| Pin                        | Name                                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|----------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CLK                        | System clock                                                | All operations synchronized to rising edge of CLK.                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

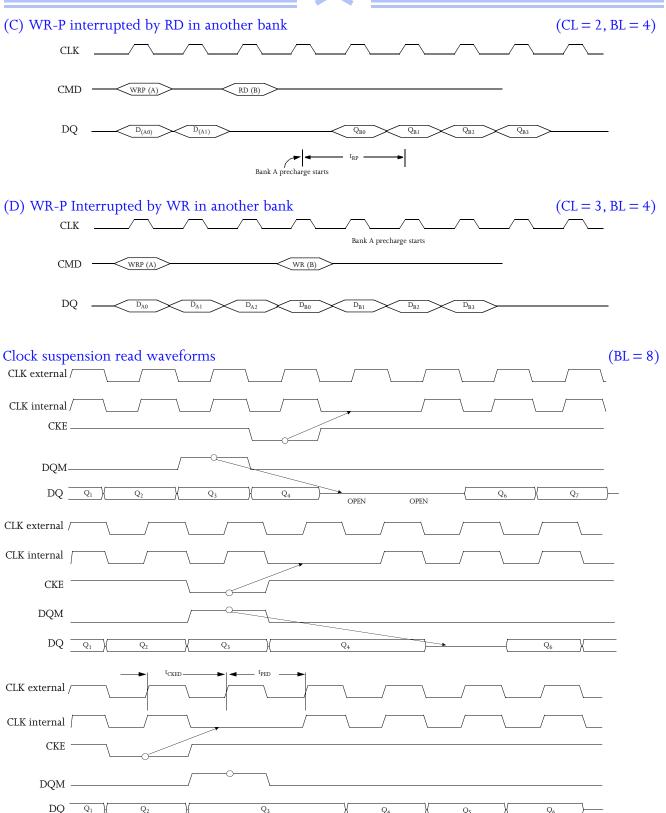

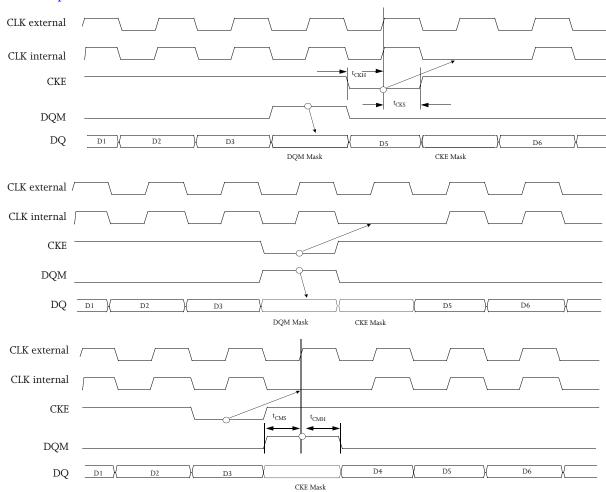

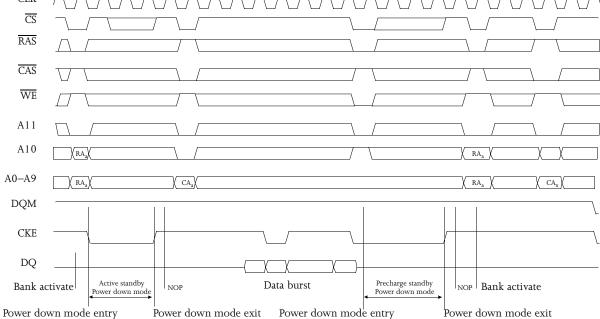

| CKE                        | Clock enable                                                | Controls CLK input. If CKE is high, the next CLK rising edge is valid. If CKE is low, the internal clock is suspended from the next clock cycle and the burst address and output states are frozen. If both banks are idle and CKE goes low, the SDRAM will enter power down mode from the next clock cycle. When in power down mode and CKE is low, no input commands will be acknowledged. To exit power down mode, raise CKE high before the rising edge of CLK. |  |  |  |  |

| CS                         | Chip select                                                 | Enables or disables device operation by masking or enabling all inputs except CLK, CKE, UDQM/LDQM (×16), DQM (×8).                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| A0~A10                     | Address                                                     | Row and column addresses are multiplexed. Row address: A0 $\sim$ A10. Column address (2M $\times$ 8): A0 $\sim$ A8. Column address (1M $\times$ 16): A0 $\sim$ A7.                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| A11                        | Bank select                                                 | Memory cell array is organized in 2 banks. All selects which internal bank will be active. All is latched during bank activate, read, write, mode register set, and precharge operations. Asserting All low selects Bank A; All high selects Bank B.                                                                                                                                                                                                                |  |  |  |  |

| RAS<br>CAS<br>WE           | Row address strobe<br>Column address strobe<br>Write enable | Command inputs. $\overline{RAS}$ , $\overline{CAS}$ , and $\overline{WE}$ , along with $\overline{CS}$ , define the command being entered.                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

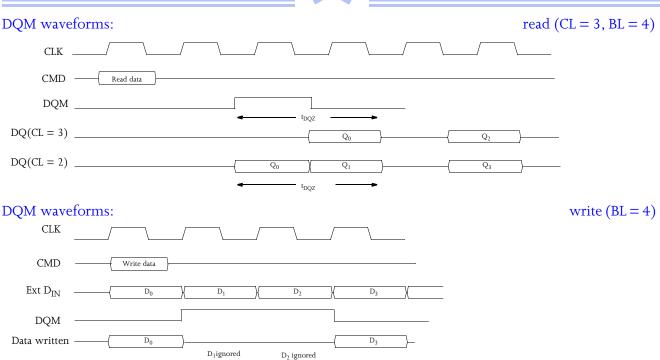

| ×8: DQM<br>×16: UDQM, LDQM | Output disable/ write mask                                  | Controls I/O buffers. When DQM is high, output buffers are disabled during a read operation and input data is masked during a write operation. DQM latency is 2 clocks for Read and 0 clocks for Write. For $\times 16$ , LDQM controls the lower byte (DQ0 $-$ 7) and UDQM controls the upper byte (DQ8 $-$ 15). UDQM and LDQM are considered to be in the same state when referred to jointly as DQM.                                                             |  |  |  |  |

| DQ0~DQ15                   | Data input/output                                           | Data inputs/outputs are multiplexed.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| $V_{CC}/V_{SS}$            | Power supply/ground                                         | Power and ground for core logic and input buffers.                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| $V_{CCQ}/V_{SSQ}$          | Data output power/ground                                    | Power and ground for data output buffers.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

Operating modes

| Орстанну                 | Comma             |                | CKEn-1 | CKEn | CS | RAS | CAS | WE | DQM | A11   | A10      | A9-A0             | Note |

|--------------------------|-------------------|----------------|--------|------|----|-----|-----|----|-----|-------|----------|-------------------|------|

|                          |                   |                |        | X    | L  | L   | L   | L  | X   | АП    |          |                   |      |

|                          | Mode register set |                | Н      |      |    |     |     |    |     |       | Op coo   | ie                | 1,2  |

|                          | Auto refr         | esh            | Н      | Н    | L  | L   | L   | Н  | X   |       | X        |                   | 3    |

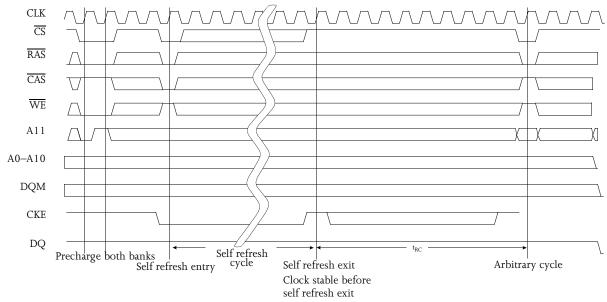

|                          | Self              | Entry          | Н      | L    | L  | L   | L   | Н  | X   |       | X        |                   | 3    |

|                          | refresh           | Exit           | L      | Н    | L  | Н   | Н   | Н  | X   |       | X        |                   | 3    |

|                          |                   | EXIL           | ь      | 11   | Н  | X   | X   | X  | X   |       | X        |                   | 3    |

| Bank activa              | ite               |                | Н      | X    | L  | L   | Н   | Н  | X   | $V^*$ | row      | address           |      |

| Read                     | Auto pre          | charge disable | - H    | X    | L  | Н   | L   | Н  | X   | V     | L        | column<br>address | 4    |

| Neau                     | Auto pre          | charge enable  | - п    | Λ    | L  | п   | L   | п  | Λ   | V     | Н        |                   | 4,5  |

| Write                    | Auto pre          | charge disable | - H    | X    | L  | Н   | L   | L  | X   | V     | L column | 4                 |      |

| Wille                    | Auto pre          | charge enable  | - п    | Λ    | L  |     | L   | L  | Λ   | V     | Н        | address           | 4,5  |

| Burst stop               |                   |                | Н      | X    | L  | Н   | Н   | L  | X   |       | X        |                   | 6    |

| D l                      | Selected          | bank           | – H    | X    | L  | L   |     | L  | X   | V     | L        | v                 |      |

| Precharge                | Both ban          | ks             |        |      | L  | L   | Н   | L  |     | X     | Н        | – X               |      |

| -1 1                     |                   | Н              | L      | Н    | X  | X   | X   | X  |     |       |          |                   |      |

| Clock susp<br>active pow |                   | Entry          | п      | L    | L  | V   | V   | V  | X   | X     |          |                   |      |

| active pow               | Exit              |                | L      | Н    | X  | X   | X   | X  | X   |       |          |                   |      |

|                          |                   | Entwee         | Н      | L    | Н  | X   | X   | X  | X   |       |          |                   |      |

| Precharge j              | power             | Entry          | п      | L    | L  | Н   | Н   | Н  | X   |       | X        |                   |      |

| down mod                 | le                | F:4            | т      | TT   | Н  | X   | X   | X  | X   |       | Λ        |                   |      |

|                          | Exit              | EXIL           | L      | Н    | L  | Н   | Н   | Н  | X   |       |          |                   |      |

| DQM                      |                   |                | Н      | X    | X  | X   | X   | X  | V   | X     | X        | X                 | 7    |

| No oper-ti               | on com            | . n. d         | тт     | v    | Н  | X   | X   | X  | X   |       | v        |                   |      |

| No operation command     |                   | Н              | Λ      | X    |    | Н   | Н   | X  | - X |       |          |                   |      |

|                          |                   |                |        |      |    |     |     |    |     |       |          |                   |      |

<sup>\*</sup> V = Valid.

- OP= operation code. A0~A11 see page 5.

- MRS can be issued only when both banks are precharged and no data burst is ongoing. A new command can be issued 2 clock cycles after MRS.

- Auto refresh functions similarly to CBR DRAM refresh. However, precharge is automatic. Auto/self refresh can only be issued after both banks are precharged.

- A11: bank select address. If low during read, write, row active and precharge, bank A is selected. If high during those states, bank B is selected. Both banks are selected and A11 is ignored if A10 is high during row precharge.

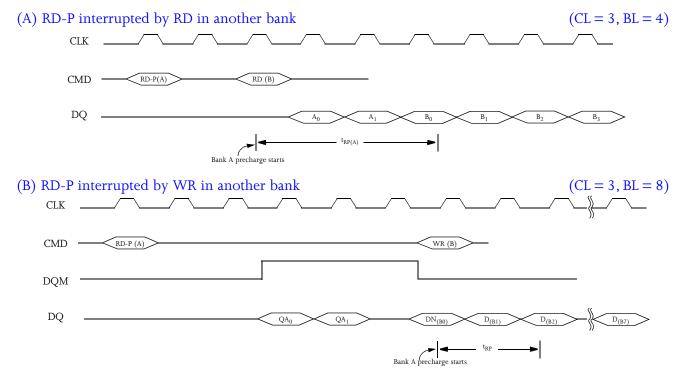

- A new read/write/deac command to the same bank cannot be issued during a burst read/write with auto precharge. A new row active command can be issued after  $t_{\mbox{\scriptsize RP}}$  from the end of the burst.

- Burst stop command valid at every burst length except full-page burst.

- DQM sampled at positive edge of CLK. Data-in may be masked at every CLK (Write DQM latency is 0). Data-out mask is active 2 CLK cycles after issuance. (Read DQM latency is 2).

## Mode register fields

| Register programmed with MRS |                  |     |    |    |             |    |    |              |    |    |    |

|------------------------------|------------------|-----|----|----|-------------|----|----|--------------|----|----|----|

| Address                      | A11~A10          | A9  | A8 | A7 | A6          | A5 | A4 | A3           | A2 | A1 | A0 |

| Function                     | RFU <sup>†</sup> | WBL | TM |    | CAS latency |    | BT | Burst length |    | h  |    |

$^{\dagger}\,\text{RFU}=0$  during MRS cycle.

| Write burst length |                            |  |  |  |  |

|--------------------|----------------------------|--|--|--|--|

| A9                 | Length                     |  |  |  |  |

| 0                  | Programmed<br>burst length |  |  |  |  |

| 1                  | Single burst               |  |  |  |  |

| Burst type |             |  |  |  |  |

|------------|-------------|--|--|--|--|

| A3         | Туре        |  |  |  |  |

| 0          | Sequential  |  |  |  |  |

| 1          | Interleaved |  |  |  |  |

| Test mode  |   |                   |  |  |  |  |  |

|------------|---|-------------------|--|--|--|--|--|

| A8 A7 Type |   |                   |  |  |  |  |  |

| 0          | 0 | Mode register set |  |  |  |  |  |

| 0          | 1 | Reserved          |  |  |  |  |  |

| 1          | 0 | Reserved          |  |  |  |  |  |

| 1          | 1 | Reserved          |  |  |  |  |  |

|    | CAS latency |    |          |  |  |  |  |  |  |  |

|----|-------------|----|----------|--|--|--|--|--|--|--|

| A6 | A5          | A4 | Latency  |  |  |  |  |  |  |  |

| 0  | 0           | 0  | Reserved |  |  |  |  |  |  |  |

| 0  | 0           | 1  | 1        |  |  |  |  |  |  |  |

| 0  | 1           | 0  | 2        |  |  |  |  |  |  |  |

| 0  | 1           | 1  | 3        |  |  |  |  |  |  |  |

| 1  | X           | X  | Reserved |  |  |  |  |  |  |  |

|    | Р  | Surst length |           |          |

|----|----|--------------|-----------|----------|

| A2 | A1 | A0           | BT = 0    | BT = 1   |

| 0  | 0  | 0            | 1         | 1        |

| 0  | 0  | 1            | 2         | 2        |

| 0  | 1  | 0            | 4         | 4        |

| 0  | 1  | 1            | 8         | 8        |

| 1  | 0  | 0            | Reserved  | Reserved |

| 1  | 0  | 1            | Reserved  | Reserved |

| 1  | 1  | 0            | Reserved  | Reserved |

| 1  | 1  | 1            | Full page | Reserved |

Burst sequence (burst length = 4)

| Initial address |    |            |   |   |   |            |   |   |   |

|-----------------|----|------------|---|---|---|------------|---|---|---|

| A1              | A0 | Sequential |   |   |   | Interleave |   |   |   |

| 0               | 0  | 0          | 1 | 2 | 3 | 0          | 1 | 2 | 3 |

| 0               | 1  | 1          | 2 | 3 | 0 | 1          | 0 | 3 | 2 |

| 1               | 0  | 2          | 3 | 0 | 1 | 2          | 3 | 0 | 1 |

| 1               | 1  | 3          | 0 | 1 | 2 | 3          | 2 | 1 | 0 |

Burst sequence (burst length = 8)

| I  | Initial address |    |   |            |   |   |   |            |   |   |   |   |   |   |   |   |   |   |

|----|-----------------|----|---|------------|---|---|---|------------|---|---|---|---|---|---|---|---|---|---|

| A2 | A1              | A0 |   | Sequential |   |   |   | Interleave |   |   |   |   |   |   |   |   |   |   |

| 0  | 0               | 0  | 0 | 1          | 2 | 3 | 4 | 5          | 6 | 7 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 0  | 0               | 1  | 1 | 2          | 3 | 4 | 5 | 6          | 7 | 0 | 1 | 0 | 3 | 2 | 5 | 4 | 7 | 6 |

| 0  | 1               | 0  | 2 | 3          | 4 | 5 | 6 | 7          | 0 | 1 | 2 | 3 | 0 | 1 | 6 | 7 | 4 | 5 |

| 0  | 1               | 1  | 3 | 4          | 5 | 6 | 7 | 0          | 1 | 2 | 3 | 2 | 1 | 0 | 7 | 6 | 5 | 4 |

| 1  | 0               | 0  | 4 | 5          | 6 | 7 | 0 | 1          | 2 | 3 | 4 | 5 | 6 | 7 | 0 | 1 | 2 | 3 |

| 1  | 0               | 1  | 5 | 6          | 7 | 0 | 1 | 2          | 3 | 4 | 5 | 4 | 7 | 6 | 1 | 0 | 3 | 2 |

| 1  | 1               | 0  | 6 | 7          | 0 | 1 | 2 | 3          | 4 | 5 | 6 | 7 | 4 | 5 | 2 | 3 | 0 | 1 |

| 1  | 1               | 1  | 7 | 0          | 1 | 2 | 3 | 4          | 5 | 6 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

## Recommended operating conditions

| Parameter                             | Symbol                            | Min              | Nominal | Max            | Unit | Notes  |

|---------------------------------------|-----------------------------------|------------------|---------|----------------|------|--------|

| Cumply valtage                        | v <sub>cc</sub> ,v <sub>ccQ</sub> | 3.0              | 3.3     | 3.6            | V    | 8<br>8 |

| Supply voltage                        | GND                               | 0.0              | 0.0     | 0.0            | V    |        |

| Input valters                         | $V_{IH}$                          | 2.0              | ı       | $V_{CC} + 0.3$ | V    | 8      |

| Input voltage                         | $V_{\mathrm{IL}}$                 | $-0.3^{\dagger}$ | -       | 0.8            | V    | 8      |

| Output voltage <sup>‡</sup>           | V <sub>OH</sub>                   | 2.4              | ı       | _              | V    |        |

| tput voltage $^{\ddagger}$ $V_{OL}$ 2 |                                   | I                | ı       | 0.4            | V    |        |

| Ambient operating temperature         | $T_{A}$                           | 0                |         | 70             | °C   |        |

$<sup>^{\</sup>dagger}$  V<sub>IL</sub> Min = -1.5V for pulse widths less than 5 ns.

Recommended operating conditions apply throughout this document unless otherwise specified.

### Absolute maximum ratings

| 8                             |                                   |      |      |      |       |

|-------------------------------|-----------------------------------|------|------|------|-------|

| Parameter                     | Symbol                            | Min  | Max  | Unit | Notes |

| Input voltage                 | V <sub>IN</sub> ,V <sub>OUT</sub> | -1.0 | +4.6 | V    |       |

| Power supply voltage          | $v_{cc}, v_{ccQ}$                 | -1.0 | +4.6 | V    |       |

| Storage temperature (plastic) | T <sub>STG</sub>                  | -55  | +150 | °C   |       |

| Power dissipation             | $P_{\mathrm{D}}$                  | _    | 1    | W    |       |

| Short circuit output current  | I <sub>OUT</sub>                  | _    | 50   | mA   |       |

Note: Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions outside those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

$<sup>^{\</sup>ddagger}$  I<sub>OH</sub> = -2mA, and I<sub>OL</sub> = 2mA.

## DC electrical characteristics

|                                                         |                    |                                                                                                                                                                                                                                  |        | _   | -7  | -   | -8  | _   | 10                                                             |       |             |

|---------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|-----|-----|----------------------------------------------------------------|-------|-------------|

| Parameter                                               | Symbol             | Test conditions                                                                                                                                                                                                                  |        | Min | Max | Min | Max | Min | Max                                                            | Unit  | Notes       |

| Input leakage current                                   | ${ m I}_{ m IL}$   | $0V \le V_{IN} \le V_{CC}$ ,<br>Pins not under test = $0V$                                                                                                                                                                       |        | -5  | +5  | -5  | +5  | -5  | +5                                                             | μΑ    |             |

| Output leakage<br>current                               | $I_{OL}$           | $D_{OUT}$ disabled, $0V \le V_{OUT} \le V_{CCQ}$                                                                                                                                                                                 |        | -10 | +10 | -10 | +10 | -10 | +10                                                            | μΑ    |             |

| Operating current (one bank active)                     | $I_{CC1}$          | $t_{RC} \ge min, I_O = 0mA,$<br>burst length = 1                                                                                                                                                                                 | CL =3  | _   | 140 | -   | 100 | _   | 100                                                            | mA    | 1,3,<br>4,5 |

| Precharge standby                                       | I <sub>CC2P</sub>  | $CKE \le V_{IL}(max)$ , $t_{CK} = 15 \text{ ns}$                                                                                                                                                                                 |        | _   | 2.0 | _   | 2.0 | _   | 2.0                                                            | mA    |             |

| current (power<br>down mode)                            | $I_{\rm CC2PS}$    | CKE and CLK $\leq$ V <sub>IL</sub> (max), t <sub>CK</sub> = $\infty$                                                                                                                                                             |        | _   | 2.0 | -   | 2.0 | _   | 2.0                                                            | mA    |             |

| Precharge standby current (non-power-                   | I <sub>CC2N</sub>  | $CS \ge V_{IH}(min)$ , $CKE \ge V_{IH}(min)$ ,<br>$t_{CK} = 15$ ns; input signals changed<br>once during 30 ns                                                                                                                   |        | _   | 30  | -   | 30  | _   | +10 μA  100 mA  2.0 mA  2.0 mA  30 mA  6 mA  2 mA  2 mA  35 mA | 1,2,3 |             |

| down mode)                                              | I <sub>CC2NS</sub> | $\begin{aligned} \text{CLK} &\leq \text{V}_{\text{IL}}(\text{max}), \text{ CKE} \geq \text{V}_{\text{IH}}(\text{min}), \\ \text{t}_{\text{CK}} &= \infty; \text{ input signals stable} \end{aligned}$                            |        | _   | 6   | _   | 6   | _   | 6                                                              | mA    | 1,2,3       |

| Active standby                                          | $I_{CC3P}$         | CKE $\leq$ V <sub>IL</sub> (max), t <sub>CK</sub> = 15 ns                                                                                                                                                                        |        | _   | 2   | _   | 2   | _   | 2                                                              | mA    | 1,2,3       |

| current (power-<br>down mode)                           | $I_{CC3PS}$        | CLK, CKE $\leq$ V <sub>IL</sub> (max), t <sub>CK</sub> = $\infty$                                                                                                                                                                |        | _   | 2   | ı   | 2   | _   | 2                                                              | mA    | 1,2,3       |

| Active standby<br>current (non-power-<br>down mode, one | I <sub>CC3N</sub>  | $\begin{aligned} \text{CKE} &\geq \text{V}_{\text{IH}}(\text{min}), \text{ CS} \geq \text{V}_{\text{IH}}(\text{min}), \\ \text{t}_{\text{CK}} &= 15 \text{ ns; input signals changed} \\ \text{once during 30 ns} \end{aligned}$ |        | _   | 35  | l   | 35  |     | 35                                                             | mA    | 1,2,3       |

| bank active)                                            | $I_{CC3NS}$        | $\begin{aligned} \text{CKE} &\geq \text{V}_{\text{IH}}(\text{min}), \text{ CLK} &\geq \text{V}_{\text{IL}}(\text{max}), \\ \text{t}_{\text{CK}} &= \infty; \text{ input signals stable} \end{aligned}$                           |        | _   | 10  | -   | 10  | _   | 10                                                             | mA    | 1,2,3       |

|                                                         |                    | $I_O = 0 \text{ mA}$                                                                                                                                                                                                             | CL =3  |     | 140 | -   | 130 | _   | 120                                                            |       |             |

| Operating current (burst mode)                          | $I_{CC4}$          | Page burst<br>All banks activated                                                                                                                                                                                                | CL = 2 |     | 125 | _   | 115 | _   | 100                                                            | mA    | 1,2,<br>3,5 |

| (Saist mode)                                            |                    | $t_{CCD} = t_{CCD}(min)$                                                                                                                                                                                                         | CL =1  |     | 80  | _   | 70  | _   | 70                                                             |       | 5,5         |

| Refresh current                                         | I <sub>CC5</sub>   | $t_{RC} \ge t_{RC}(\min)$                                                                                                                                                                                                        |        |     | 100 | _   | 90  | _   | 80                                                             | mA    | 1,2,<br>3,5 |

| Self refresh current                                    | Т                  | CKE ≤ 0.2 V                                                                                                                                                                                                                      |        |     | 2   | -   | 2   | _   | 2                                                              | mA    |             |

| ben reiresii current                                    | $I_{CC6}$          | CAE > U.Z V                                                                                                                                                                                                                      |        |     | 1   | _   | 1   | _   | 1                                                              | mA    | 15          |

CL = CAS latency.

## AC parameters common to all waveforms

|                    |                                                                                                                     | CAS -7 -8 |      |      | -8  | -10  |     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

|--------------------|---------------------------------------------------------------------------------------------------------------------|-----------|------|------|-----|------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Sym                | Parameter                                                                                                           | latency   | Min  | Max  | Min | Max  | Min | Max  | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Notes |

|                    |                                                                                                                     | 3         | -    | 5.5  | _   | 6    | _   | 6    | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6     |

| t <sub>AC</sub>    | CLK to valid output delay                                                                                           | 2         | _    | 8.5  | _   | 7    | _   | 6    | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6,8   |

|                    |                                                                                                                     | 1         | _    | 18   | _   | 22   | _   | 22   | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6,8   |

| t <sub>AH</sub>    | Address hold time                                                                                                   |           | -    | 1    | _   | 1    |     | 1    | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7     |

| t <sub>AS</sub>    | Address setup time                                                                                                  |           | 2    | _    | 2   | _    | 2   | _    | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7     |

| $t_{\mathrm{BDL}}$ | Last data-in to burst stop                                                                                          |           | 0    | _    | 0   | _    | 0   | _    | $t_{CK}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9     |

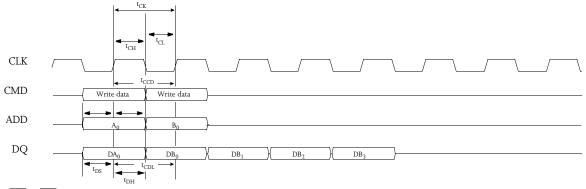

| t <sub>CCD</sub>   | Read/write command to read/write command                                                                            |           | 1    | _    | 1   | _    | 1   | _    | t <sub>CK</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9     |

| t <sub>CDL</sub>   | Last data-in to new<br>column address delay                                                                         |           | 1    | _    | 1   | _    | 1   | _    | t <sub>CK</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9     |

| t <sub>CH</sub>    | CLK high-level width                                                                                                |           | 2.75 | _    | 3   | _    | 3   | _    | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7     |

|                    |                                                                                                                     | 3         | 7    | 1000 | 8   | 1000 | 10  | 1000 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10    |

| $t_{CK}$           | CLK cycle time                                                                                                      | 2         | 8.7  | 1000 | 10  | 1000 | 12  | 1000 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10    |

|                    |                                                                                                                     | 1         | 20   | 1000 | 25  | 1000 | 25  | 1000 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10    |

| t <sub>CKED</sub>  | CKE to CLOCK disable or power-down entry mode                                                                       |           | 1    | _    | 1   | _    | 1   | _    | t <sub>CK</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| t <sub>CKH</sub>   | CKE hold time                                                                                                       |           | 1    | _    | 1   | _    | 1   | _    | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

| t <sub>CKS</sub>   | CKE setup time                                                                                                      |           | 2    | _    | 2   | _    | 2   | _    | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

| t <sub>CL</sub>    | CLK low-level width                                                                                                 |           | 2.75 | _    | 3   | _    | 3.5 | _    | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7     |

| t <sub>CMH</sub>   | $\overline{\text{CS}}$ , $\overline{\text{RAS}}$ , $\overline{\text{CAS}}$ , $\overline{\text{WE}}$ , DQM hold time |           | 1    | -    | 1   | _    | 1   | _    | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

| t <sub>CMS</sub>   | CS, RAS, CAS, WE, DQM setup time                                                                                    |           | 2    | _    | 2   | _    | 2   | _    | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

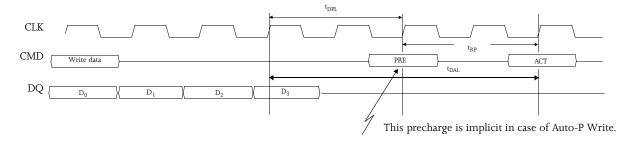

|                    | Data-in to ACTIVE                                                                                                   | 3         | 5    | _    | 5   | -    | 5   | _    | t <sub>CK</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5,11  |

| $t_{DAL}$          | command                                                                                                             | 2         | 5    | _    | 5   | -    | 5   | _    | t <sub>CK</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5,11  |

|                    |                                                                                                                     | 1         | 4    | _    | 4   | _    | 4   | _    | t <sub>CK</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5,11  |

| $t_{\mathrm{DH}}$  | Data in hold time                                                                                                   |           | 1    | _    | 1   | _    | 1   | _    | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

| $t_{\mathrm{DPL}}$ | Data in to PRECHARGE                                                                                                |           | 2    | _    | 2   | _    | 2   | _    | t <sub>CK</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12    |

| $t_{\rm DQD}$      | DQM to input data delay                                                                                             |           | 1    | _    | 1   | _    | 1   | _    | t <sub>CK</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9     |

| t <sub>DQM</sub>   | DQM to data mask during writes                                                                                      |           | 0    | -    | 0   | _    | 0   | _    | t <sub>CK</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9     |

| t <sub>DQZ</sub>   | DQM to data high Z<br>during reads                                                                                  |           | 2    | _    | 2   | _    | 2   | _    | t <sub>CK</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9     |

| t <sub>DS</sub>    | Data in setup time                                                                                                  |           | 2    | _    | 2   | _    | 2   | _    | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

| t <sub>DWD</sub>   | Write command to input data delay                                                                                   |           | 0    | _    | 0   | _    | 0   | _    | t <sub>CK</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9     |

|                    | Data out high id-                                                                                                   | 3         | -    | 5.5  | _   | 6    | _   | 9    | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13    |

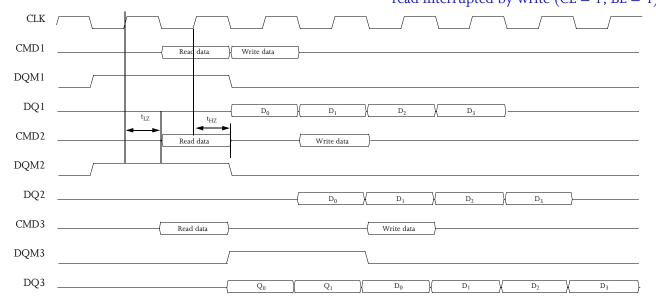

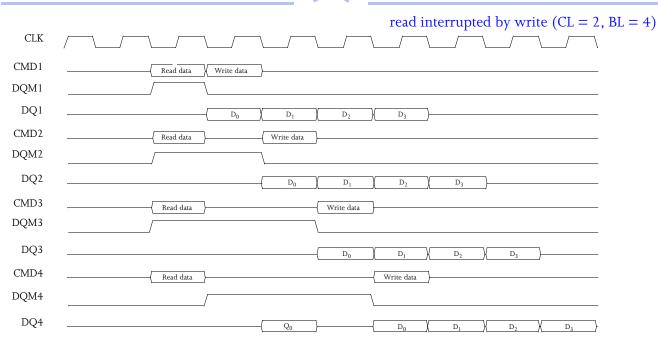

| t <sub>HZ</sub>    | Data-out high-impedance time                                                                                        | 2         | _    | 8.5  | _   | 9    | _   | 9    | ns 6 ns 6,8 ns 6,8 ns 7 ns 7 ns 7 t <sub>CK</sub> 9 t <sub>CK</sub> 9 t <sub>CK</sub> 9 ns 7 ns 10 ns 10 ns 10 ns 10 ns 10 t <sub>CK</sub> ns ns ns 7 ns 10 t <sub>CK</sub> 9 t <sub>CK</sub> 9 t <sub>CK</sub> 9 ns 7 ns 10 ns 10 t <sub>CK</sub> 9 t <sub>CK</sub> 9 t <sub>CK</sub> 9 ns 7 ns 10 ns 10 t <sub>CK</sub> 9 ns 10 t <sub>CK</sub> 9 ns 9 ns 7 ns 9 ns 9 t <sub>CK</sub> 9,11 t <sub>CK</sub> 5,11 t <sub>CK</sub> 5,11 t <sub>CK</sub> 9 t <sub>CK</sub> 9 t <sub>CK</sub> 9 t <sub>CK</sub> 9 |       |

|                    |                                                                                                                     | 1         | -    | 18   | _   | 22   | _   | 22   | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13    |

| t <sub>LZ</sub>    | Data-out low-impedance time                                                                                         |           | 1    | _    | 1   | _    | 1   | _    | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

|                  |                                              | CAS     |     | <b>-7</b> | _   | -8      | -:  | 10      |                 |       |

|------------------|----------------------------------------------|---------|-----|-----------|-----|---------|-----|---------|-----------------|-------|

| Sym              | Parameter                                    | latency | Min | Max       | Min | Max     | Min | Max     | Unit            | Notes |

| t <sub>MRD</sub> | Load mode register to active/refresh command |         | 2   | _         | 2   | _       | 2   | _       | t <sub>CK</sub> | 5     |

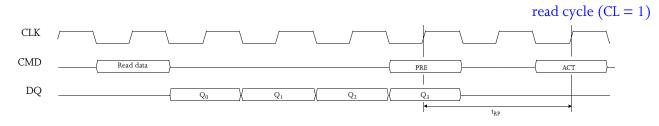

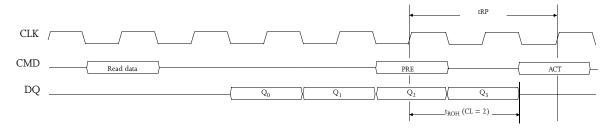

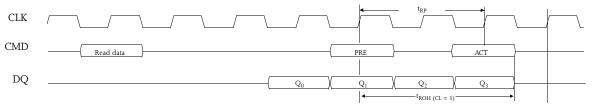

|                  | Output data hald time @                      | 3       | 2   | _         | 2.5 | _       | 3   | _       | ns              | 6     |

| t <sub>OH</sub>  | Output data hold time @ 30 pF                | 2       | 2   | _         | 2.5 | _       | 3   | _       | ns              | 6     |

|                  | 0 0 P1                                       | 1       | 2   | _         | 2.5 | _       | 3   | _       | t <sub>CK</sub> | 6     |

| t <sub>PED</sub> | CKE to CLOCK enable or power-down exit mode  |         | 1   | _         | 1   | _       | 1   | -       | t <sub>CK</sub> |       |

| t <sub>RAS</sub> | Active to precharge command                  |         | 42  | 120,000   | 48  | 120,000 | 50  | 120,000 | ns              |       |

| $t_{RC}$         | Active command period                        |         | 70  | _         | 80  | _       | 80  | _       | ns              | 8     |

| $t_{RCAR}$       | Auto refresh period                          |         | 70  | _         | 80  | _       | 80  | _       | ns              |       |

| t <sub>RCD</sub> | Active to read or write delay                | 3       | 3   | _         | 3   | _       | 3   | _       | t <sub>CK</sub> | 8     |

| t <sub>REF</sub> | Refresh period—2048 rows                     |         | _   | 64        | _   | 64      | _   | 64      | ms              |       |

|                  | Data-out high Z from                         | 3       | 3   | _         | 3   | _       | 3   | _       | $t_{CK}$        | 9     |

| $t_{ROH}$        | precharge/burst stop                         | 2       | 2   | _         | 2   | _       | 2   | _       | t <sub>CK</sub> | 9     |

|                  | command                                      | 1       | 1   | _         | 1   | _       | 1   | _       | t <sub>CK</sub> | 9     |

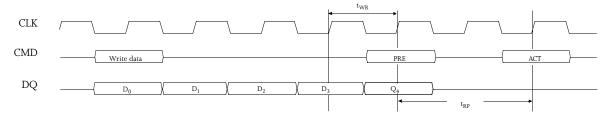

| t <sub>RP</sub>  | Precharge command period                     | 3       | 3   | _         | 3   | -       | 3   | _       | t <sub>CK</sub> | 8     |

| t <sub>RRD</sub> | Active Bank A to Active<br>Bank B command    |         | 14  | _         | 16  | _       | 20  | _       | ns              |       |

| t <sub>T</sub>   | Transition time                              |         | 0.3 | 1.0       | 0.3 | 1.0     | 0.3 | 1.0     | ns              |       |

| t <sub>WR</sub>  | WRITE recovery time                          |         | 2   | _         | 2   | _       | 2   | _       | t <sub>CK</sub> |       |

| t <sub>XSR</sub> | Exit SELF REFRESH to<br>ACTIVE command       |         | 70  | _         | 80  | _       | 80  | _       | ns              | 20    |

#### Notes

- 1 I<sub>DD</sub> is dependent on output loading and cycle rates. Specified values are obtained with minimum cycle time and the outputs open.

- 2 Other input signals are allowed to transition no more than once in any two-clock period and are otherwise at valid  $V_{\mathrm{IH}}$  or  $V_{\mathrm{IL}}$  levels.

- 3 Address transitions average one transition every two-clock period.

- 4 The I<sub>DD</sub> current will decrease as the CAS-latency is reduced. This is due to the fact that the maximum cycle rate is slower as the CAS-latency is reduced.

- 5  $t_{CK} = 7 \text{ ns for } -7$ , 8 ns for -8, and 10 ns for -10.

- 6 If clock  $t_r > 1$  ns,  $(t_{r/2} 0.5)$ ns should be added to the parameter.

- 7 If clock  $(t_r \text{ and } t_f) > 1 \text{ ns, } [(t_r + t_f)/2 1] \text{ ns should be added to the parameter.}$

- 8  $V_{IH}$  overshoot:  $V_{IH(max)} = V_{DDQ} + 2V$  for a pulse width  $\leq 3$  ns, and the pulse width cannot be greater than one third of the cycle rate.  $V_{IL}$  undershoot:  $V_{IL(min)} = -2V$  for a pulse width  $\leq 3$  ns and the pulse width cannot be greater than one third of the cycle rate.

- 9 Required clocks are specified by JEDEC functionalisty and are not dependent on any timing parameter.

- 10 The clock frequency must remain constant during access or precharge states (READ, WRITE, including  $t_{WR}$  and PRECHARGE commands). CKE may be used to reduce the data rate.

- 11 Timing actually specified t<sub>WR</sub> plus t<sub>RP</sub>; clock(s) specified as a reference only at minimum cycle rate.

- 12 Timing actually specified by  $t_{WR}$ .

- $t_{HZ}$  defines the time at which the output achieves the open circuit condition; it is not a reference to  $v_{OH}$  or  $v_{OL}$ . The last valid data element will meet  $t_{OH}$  before going to HIGH-Z.

- 14 CLK must be toggled a minimum of two times during this period.

- 15 Enables on-chip refresh and address counters.

- 16 All voltages referenced to V<sub>SS</sub>.

- 17 The minimum specifications are used only to indicate the cycle time at which proper operation over the full temperature range (0° C  $\leq$  T<sub>A</sub>  $\leq$  70° C) is endured.

- 18 A proper power-up initialization sequence (as described on page 10) is needed before proper device operation is ensured. (V<sub>DD</sub> and V<sub>DDQ</sub> must be powered up simultaneously. V<sub>SS</sub> and V<sub>SSQ</sub> must be at the same potential.)Two AUTOREFRESH command wake-ups should be repeated any time the t<sub>REF</sub> refresh requirement is exceeded.

- 19 AC characteristics assume  $t_T = 1$  ns.

- 20 In addition to meeting the transition rate specification, the clock and CKE must transit between  $V_{IH}$  and  $V_{IL}$  (or between  $V_{IL}$  and  $V_{IH}$ ) in a monotonic manner.

- 21 AC timing and  $I_{DD}$  tests have  $V_{IL}$  = 0V and  $V_{IH}$  = 3.0 V with timing referenced to 1.4V crossover point.

- $22\quad I_{\mbox{\scriptsize DD}}$  specifications are tested after the device is properly initialized.

- 23 Minimum clock cycles = (minimum time/clock cycle time) rounded up.

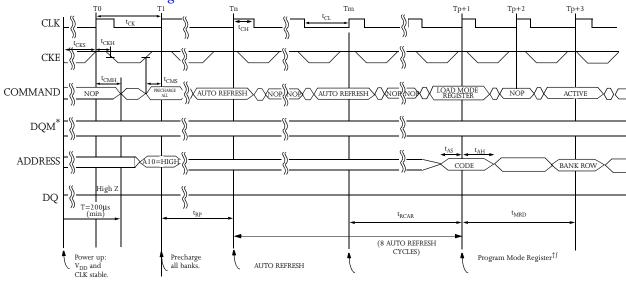

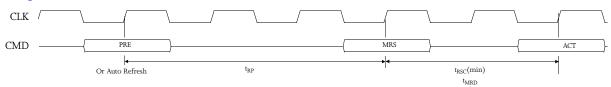

### Device operation

| Command             | Pin settings                                                                                                                                      | Description                                                                                                                                              |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     |                                                                                                                                                   | The following sequence is recommended prior to normal operation.                                                                                         |

|                     |                                                                                                                                                   | 1 Apply power, start clock, and assert CKE and DQM high. All other                                                                                       |

|                     |                                                                                                                                                   | signals are NOP.                                                                                                                                         |

| D.                  |                                                                                                                                                   | 2 After power-up, pause for a minimum of 200μs. CKE/DQM = high; all others NOP.                                                                          |

| Power up            |                                                                                                                                                   | 3 Precharge both banks.                                                                                                                                  |

|                     |                                                                                                                                                   | 4 Perform Mode Register Set command to initialize mode register.                                                                                         |

|                     |                                                                                                                                                   | 5 Perform a minimum of 8 auto refresh cycles to stabilize internal                                                                                       |

|                     |                                                                                                                                                   | circuitry.                                                                                                                                               |

|                     |                                                                                                                                                   | (Steps 4 and 5 may be interchanged.)                                                                                                                     |

|                     |                                                                                                                                                   | The mode register stores the user selected opcode for the SDRAM                                                                                          |

|                     |                                                                                                                                                   | operating modes. The CAS latency, burst length, burst type, test mode                                                                                    |

|                     |                                                                                                                                                   | and other vendor specific functions are selected/programmed during                                                                                       |

| Mode register set   |                                                                                                                                                   | the Mode Register Set command cycle. The default setting of the mode                                                                                     |

| Wiode register set  | $A0\sim A11 = opcode$                                                                                                                             | register is not defined after power-up. Therefore, it is recommended                                                                                     |

|                     |                                                                                                                                                   | that the power-up and mode register set cycle be executed prior to                                                                                       |

|                     |                                                                                                                                                   | normal SDRAM operation. Refer to the Mode Register Set table and                                                                                         |

|                     |                                                                                                                                                   | timing for details.                                                                                                                                      |

|                     |                                                                                                                                                   | The SDRAM performs a "no operation" (NOP) when RAS, CAS, and                                                                                             |

| De las las las as a | CC 1::1                                                                                                                                           | WE = high. Since the NOP performs no operation, it may be used as a                                                                                      |

| Device deselect and | $\frac{\text{CS = high, or}}{\overline{\text{RAS, CAS, WE}}} = \text{high}$                                                                       | wait state in performing normal SDRAM functions. The SDRAM is deselected when $\overline{CS}$ is high. $\overline{CS}$ high disables the command decoder |

| no operation        | KAS, CAS, WE – IIIgli                                                                                                                             | such that RAS, CAS, WE and address inputs are ignored. Device                                                                                            |

|                     |                                                                                                                                                   | deselection is also considered a NOP.                                                                                                                    |

|                     |                                                                                                                                                   | The SDRAM is configured with two internal banks. Use the Bank                                                                                            |

|                     | $\overline{CS} = \overline{RAS} = low; \overline{CAS} = \overline{WE} =$                                                                          | Activate command to select a row in one of the two idle banks. Initiate                                                                                  |

| Bank activation     | high; $A0 \sim A10 = \text{row address}$ ;                                                                                                        | a read or write operation after $t_{RCD}$ (min) from the time of bank                                                                                    |

|                     | A11 = bank select                                                                                                                                 | activation.                                                                                                                                              |

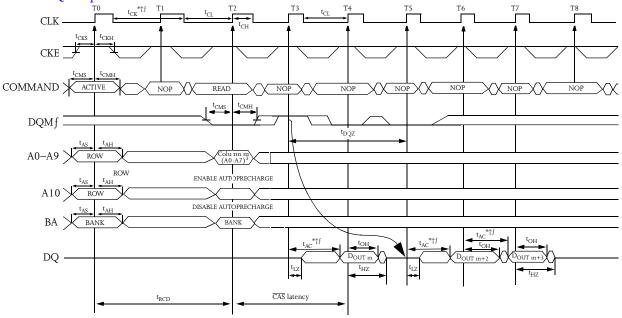

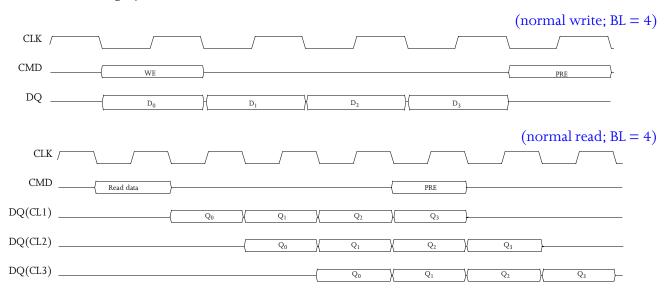

|                     |                                                                                                                                                   | Use the Burst Read command to access a consecutive burst of data from                                                                                    |

|                     |                                                                                                                                                   | an active row in an active bank. Burst read can be initiated on any                                                                                      |

|                     | $\overline{\text{CS}} = \overline{\text{CAS}} = \text{A10} = \text{low}; \overline{\text{RAS}} =$                                                 | column address of an active row. The burst length, sequence and                                                                                          |

|                     | $\overline{\text{WE}} = \text{CAS} = \text{A10} = \text{low}; \text{ RAS} = \overline{\text{WE}} = \text{high}; \text{A11} = \text{bank select},$ | latency are determined by the mode register setting. The first output                                                                                    |

| Burst read          | $A0\sim A8 = \text{column address}; (A9)$                                                                                                         | data appears after the CAS latency from the read command. The output                                                                                     |

| Durst read          | $= don't care for 2M \times 8; A8,$                                                                                                               | goes into a high impedance state at the end of the burst (BL = $1,2,4,8$ )                                                                               |

|                     | $A9 = don't care for 1M \times 16$                                                                                                                | unless a new burst read is initiated to form a gapless output data                                                                                       |

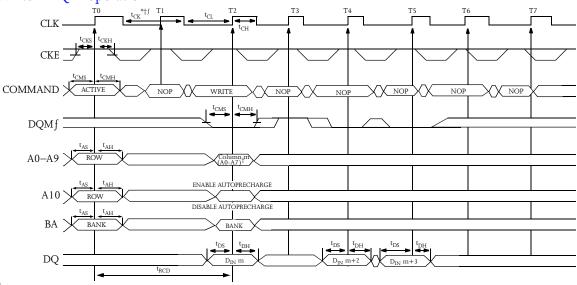

|                     |                                                                                                                                                   | stream. A full-page burst does not terminate automatically at the end of                                                                                 |