# AN8027, AN8037

## AC-DC switching power supply control IC with standby mode

#### Overview

The AN8027 and AN8037 are ICs developed for selfexcited switching regulator of RCC local resonance control type.

These ICs are designed to achieve stability and high efficiency over a wide input voltage range and loads range (light loads to heavy loads), for supporting input levels used worldwide and improved conformance with energy conservation laws.

#### Features

- Support improved conformance with energy conservation laws by providing two operating modes.

- Standby mode (light loads):

- Achieves better efficiency due to reduced frequency .

- Normal mode: Achieves high efficiency in RCC local resonance operation with zero-cross detection.

- Incorporating an input voltage compensation function available to a wide input range for worldwide use.

- This function compensates the maximum on-period in inverse proportion to the input voltage.

- Incorporating a timer latch function.

- The time period can be adjusted according to the overload in normal mode or standby mode.

- This function makes it possible to protect the IC from damage that may be caused by the short-circuiting of the IC's external capacitor for the timer.

- Incorporating an overvoltage protection function. (detects at V<sub>CC</sub> pin)

- Incorporating a pulse-by-pulse overcurrent protection function, which makes latch protection possible at the time of the short-circuiting of the transformer's primary winding.

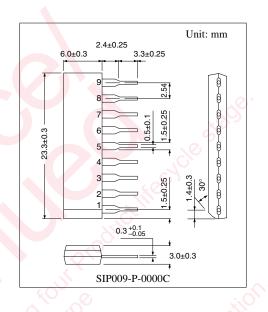

- Adopting a 9-pin single inline package (E-9S: available to manufacturing in overseas).

- AN8027: Transformer resetting is detected from the high- or low-level signal on the TR pin.

- AN8037: Transformer resetting is detected from the falling edge of the high-level signal on the TR pin. Refer to the "[1] operation descriptions 7. local resonance operation" section in the application notes.

#### Applications

• Televisions, VCRs, facsimiles, and printers

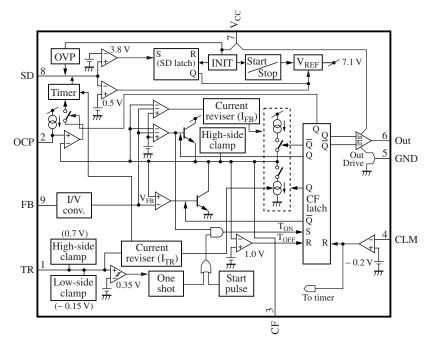

#### Block Diagram

#### Absolute Maximum Ratings

| Parameter                                   | Symbol           | Rating        | Unit |

|---------------------------------------------|------------------|---------------|------|

| Supply voltage                              | V <sub>CC</sub>  | 24            | V    |

| Constant output current                     | I <sub>OUT</sub> | ±150          | mA   |

| Peak output current                         | I <sub>OP</sub>  | ±1000         | mA   |

| TR pin allowable application current        | I <sub>TR</sub>  | ±5            | mA   |

| OCP pin allowable application voltage       | V <sub>OCP</sub> | - 0.3 to +7.0 | V    |

| CLM pin allowable application voltage       | V <sub>CLM</sub> | - 0.3 to +7.0 | V    |

| SD pin allowable application voltage        | V <sub>SD</sub>  | - 0.3 to +7.0 | V    |

| FB pin allowable application current        | I <sub>FB</sub>  | 0 to -2.0     | mA   |

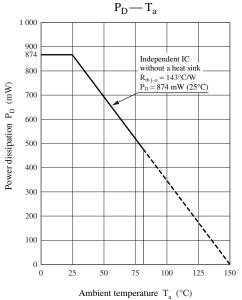

| Power dissipation ( $T_a \le 25^{\circ}C$ ) | P <sub>D</sub>   | 874           | mW   |

| Power dissipation ( $T_a = 85^{\circ}C$ )   |                  | 454           | mW   |

| Operating ambient temperature *             | T <sub>opr</sub> | -30 to +85    | °C   |

| Storage temperature *                       | T <sub>stg</sub> | -55 to +150   | °C   |

Note) 1. \*: Except for the operating ambient temperature and storage temperature, all ratings are for  $T_a = 25^{\circ}C$ .

2. Do not apply external currents or voltages to any pins not specifically mentioned.

For circuit current, '+' denotes current flowing into the IC, and '-' denotes current flowing out of the IC.

#### Recommended Operating Range

| Parameter      | Symbol          | Range                                           | Unit |

|----------------|-----------------|-------------------------------------------------|------|

| Supply voltage | V <sub>CC</sub> | From the stop voltage to the OVP supply voltage | V    |

## Electrical Characteristics at $V_{CC} = 18 \text{ V}, \text{ T}_a = 25^{\circ}\text{C}$

| Parameter                                                           | Symbol                | Conditions                                                                      | Min    | Тур    | Max    | Unit |

|---------------------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------|--------|--------|--------|------|

| Low voltage protection (U.V.L.O.)<br>initial startup supply voltage | V <sub>CC-START</sub> |                                                                                 | 13.4   | 14.9   | 16.4   | V    |

| Low voltage protection (U.V.L.O.) operation stop supply voltage     | V <sub>CC-STOP</sub>  |                                                                                 | 7.7    | 8.6    | 9.5    | V    |

| Overvoltage protection (OVP)<br>operating supply voltage            | V <sub>CC-OVP</sub>   |                                                                                 | 19.4   | 20.5   | 21.6   | V    |

| Overvoltage protection (SD)<br>operating threshold voltage          | V <sub>TH1-SD</sub>   |                                                                                 | 3.5    | 3.9    | 4.3    | V    |

| Overvoltage protection (SD)<br>reset threshold voltage              | V <sub>TH2-SD</sub>   |                                                                                 | 0.4    | 0.8    | 1.2    | V    |

| Remote (RM) operating<br>threshold voltage                          | V <sub>TH1-RM</sub>   |                                                                                 | 0.05   | 0.15   | 0.3    | V    |

| Shutdown (SD) standby voltage                                       | V <sub>STB-SD</sub>   | SD pin = Open                                                                   | 1.0    | 1.5    | 2.0    | V    |

| Overvoltage protection (OVP)<br>reset supply voltage                | V <sub>CC-OVPC</sub>  |                                                                                 | 7.3    | 8.1    | 8.9    | V    |

| Remote (RM) operating time circuit current                          | I <sub>CC-RM</sub>    | $V_{CC} = 18 \text{ V}, V_{SD} = 0 \text{ V}$                                   | 3.0    | 4.0    | 5.0    | mA   |

| Overvoltage protection (SD)<br>operating time circuit current 1     | I <sub>CC1-SD</sub>   | $V_{CC} = 10 \text{ V}, \text{ V}_{SD} = 4.3 \text{ V} \rightarrow \text{Open}$ | 1.2    | 1.5    | 1.8    | mA   |

| Overvoltage protection (SD)<br>operating time circuit current 2     | I <sub>CC2-SD</sub>   | $V_{CC} = 18 \text{ V}, \text{ V}_{SD} = 4.3 \text{ V} \rightarrow \text{Open}$ | 3.6    | 4.5    | 5.4    | mA   |

| Timer latch (SD) charge current 1                                   | I <sub>SD1-TIM</sub>  | FB pin = Open, $I_{TR} = -270 \ \mu A$                                          | 68     | 102    | 136    | μΑ   |

| Timer latch (SD) charge current 2                                   | I <sub>SD2-TIM</sub>  | FB pin = Open, $I_{TR} = -1.64 \text{ mA}$                                      | 179    | 267    | 355    | μΑ   |

| Timer latch (SD) start feedback<br>current                          | I <sub>FB-TIM</sub>   | $I_{TR} = -1 \text{ mA}, R_{OCP} = 30 \text{ k}\Omega$                          | - 0.95 | - 0.75 | - 0.55 | mA   |

| Transformer reset detection (TR)<br>threshold voltage               | V <sub>TH-TR</sub>    |                                                                                 | 0.15   | 0.25   | 0.35   | V    |

| Transformer reset detection (TR)<br>upper limit clamp voltage       | V <sub>CLH-TR</sub>   | $I_{TR} = 3 \text{ mA}$                                                         | 0.55   | 0.7    | 0.85   | V    |

| Transformer reset detection (TR)<br>lower limit clamp voltage       | V <sub>CLL-TR</sub>   | $I_{TR} = -3 \text{ mA}$                                                        | - 0.3  | - 0.15 | 0      | V    |

| Overcurrent protection (CLM)<br>threshold voltage                   | V <sub>TH-CLM</sub>   |                                                                                 | -220   | -200   | -180   | mV   |

| Oscillator (CF) upper limit voltage                                 | V <sub>H-CF</sub>     | FB pin = Open, $C_F = 2200 \text{ pF}$                                          | 3.8    | 4.2    | 4.6    | V    |

| Oscillator (CF) lower limit voltage 1                               | V <sub>L1-CF</sub>    | FB pin = Open, $C_F = 2200 \text{ pF}$                                          | 0.8    | 1.0    | 1.2    | V    |

| Oscillator (CF) lower limit voltage 2                               | V <sub>L2-CF</sub>    | $I_{FB} = -0.5 \text{ mA}, C_F = 2200 \text{ pF}$                               | 0      | 0.1    | 0.3    | V    |

| Oscillator (CF) maximum<br>on-period current gain                   | G <sub>ION-CF</sub>   | FB pin = Open, $I_{TR} = -750 \mu A$                                            | 0.8    | 1.0    | 1.2    |      |

| Oscillator (CF) maximum<br>on-period current                        | I <sub>ON-CF</sub>    | $I_{TR} = 0 mA$                                                                 | 200    | 250    | 300    | μΑ   |

| Oscillator (CF) minimum<br>off-period current 1                     | I <sub>OFF1-CF</sub>  | $I_{FB} = -0.4 \text{ mA}$                                                      | -880   | -660   | -440   | μΑ   |

## $\blacksquare$ Electrical Characteristics at V\_{CC} = 18 V, T\_a = 25°C (continued)

| Parameter                                       | Symbol                | Conditions                                                                       | Min    | Тур   | Max    | Unit |

|-------------------------------------------------|-----------------------|----------------------------------------------------------------------------------|--------|-------|--------|------|

| Oscillator (CF) minmum<br>off-period current 2  | I <sub>OFF2-CF</sub>  | $I_{FB} = -0.8 \text{ mA}$                                                       | -210   | -160  | -110   | μA   |

| Minimum off-period threshold feedback current   | I <sub>FB-TOFF</sub>  |                                                                                  | - 0.78 | - 0.6 | - 0.42 | mA   |

| Overcurrent protection (OCP) pin source current | I <sub>OCP-OCP</sub>  |                                                                                  | -130   | -100  | -70    | μA   |

| Output oscillator frequency                     | F <sub>OSC</sub>      | $C_F = 2200 \text{ pF}, I_{TR} = 475 \mu\text{A},$<br>$I_{FB} = -0.5 \text{ mA}$ | 50     | 65    | 80     | kHz  |

| Pre-startup low-level output voltage            | V <sub>OL-STB</sub>   | $V_{CC} = 13.5 \text{ V}, I_{OUT} = 1 \text{ mA}$                                | —      | 1.0   | 1.25   | V    |

| Low-level output voltage                        | V <sub>OL</sub>       | $I_{OUT} = 0.1 \text{ A}$                                                        |        | 0.9   | 2.0    | V    |

| High-level output voltage                       | V <sub>OH</sub>       | $I_{OUT} = -0.1 \text{ A}$                                                       | 15.5   | 16.3  |        | V    |

| Pre-startup circuit current 1                   | I <sub>CC-STB1</sub>  | V <sub>CC</sub> = 13.5 V                                                         | 75     | 100   | 125    | μA   |

| Circuit current 1                               | I <sub>CC1-OPR1</sub> | V <sub>CC</sub> = 10 V                                                           | 8.5    | 11.5  | 14.5   | mA   |

| Circuit current 2                               | I <sub>CC2-OPR2</sub> | V <sub>CC</sub> = 18 V                                                           | 9.0    | 12.0  | 15.0   | mA   |

| Circuit current during startup 1                | I <sub>START1</sub>   |                                                                                  |        | 200   | 380    | μΑ   |

#### • Design reference data

Note) The characteristics listed below are theoretical values based on the IC design and are not guaranteed.

| Parameter                                                                 | Symbol                    | Conditions                                                                                | Min | Тур  | Max | Unit |

|---------------------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------|-----|------|-----|------|

| Low voltage protection (U.V.L.O.)<br>start/stop supply voltage difference | $\Delta V_{CC}$           |                                                                                           |     | 6.3  |     | V    |

| Remote (RM) reset threshold voltage                                       | V <sub>TH2-RM</sub>       |                                                                                           |     | 0.1  | _   | V    |

| Timer latch (SD) overcurrent protection time                              | T <sub>CLM-SD</sub>       |                                                                                           |     | 0.1  |     | S    |

| Transformer reset detection (TR) threshold hysteresis width               | $\Delta V_{TH-TR}$        |                                                                                           |     | 0.05 |     | V    |

| Maximum on-period                                                         | T <sub>ON(max)</sub>      | $I_{TR} = 0 \text{ mA}, I_{FB} = -0.2 \text{ mA}$                                         | _   | 26.5 |     | μs   |

| Minimum off-period                                                        | T <sub>OFF(min)</sub>     | $I_{TR} = 0 \text{ mA}, I_{FB} = -0.2 \text{ mA}$                                         |     | 5    |     | μs   |

| Overcurrent protection (OCP)<br>power-on charge period                    | T <sub>SD(ON)-OCP</sub>   | $I_{FB} = -0.5 \text{ mA}, R_{OCP} = 22 \text{ k}\Omega$                                  |     | 1.8  |     | μs   |

| Overcurrent protection (OCP)<br>power-off charge period                   | T <sub>SD(OFF)</sub> -OCP | $I_{FB} = -0.5 \text{ mA}, R_{OCP} = 30 \text{ k}\Omega$                                  |     | 8.8  |     | μs   |

| Output rise time                                                          | t <sub>r</sub>            | 10% to 90%, $I_{OUT} = 0 \text{ mA}$                                                      | _   | 60   |     | ns   |

| Output fall time                                                          | t <sub>f</sub>            | 10% to 90%, $I_{OUT} = 0 \text{ mA}$                                                      |     | 20   |     | ns   |

| TR output response time                                                   | T <sub>TR</sub>           |                                                                                           | _   | 800  |     | ns   |

| CLM output response time                                                  | T <sub>CLM</sub>          |                                                                                           | _   | 100  |     | ns   |

| Pre-startup circuit current 2                                             | I <sub>CC-STB2</sub>      | $V_{CC} = 13.5 \text{ V},$<br>$T_a = -30^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}$ | 50  | 100  | 150 | μA   |

Only for AN8037

Timer period during startup

100

\_\_\_\_

μs

\_

T<sub>START</sub>

### Pin Descriptions

| Pin No. | Pin name | I/O | Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Equivalent Circuit            |

|---------|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| 1       | TR       | Ι   | Transformer reset detection input. When the IC detects transformer resetting and the fall-<br>ing edge of a high-level signal is input to<br>this pin of the AN8037 or a low-level signal<br>is input to the same pin of the AN8027, the<br>level of the Out pin becomes high. However,<br>the transformer reset signal is ignored if the<br>signal is shorter than the minimum off-pe-<br>riod determined by the CF pin. Also note<br>that the maximum on-period is corrected ac-<br>cording to the source currents. | V <sub>REF</sub>              |

| 2       | OCP      |     | Connection for the resistor that determines<br>the overload level of the IC to activate the<br>timer latch protection circuit.<br>By judging the operating mode (i.e., the nor-<br>mal or standby mode) of the IC from the<br>secondary side, the timer period is adjusted<br>with the selection of external resistance ac-<br>cording to the operating mode.                                                                                                                                                         | V <sub>REF</sub>              |

| 3       | CF       | _   | Connection for the capacitor that determines<br>the on- and off-periods of the IC output (Out).<br>The on- and off-periods are corrected by $I_{ON}$<br>which is proportional to the flowing out cur-<br>rent at the TR pin, and $I_{OFF}$ which corre-<br>sponds to the current at FB pin.                                                                                                                                                                                                                           | V <sub>REF</sub>              |

| 4       | CLM      | Ι   | Input to the pulse-by-pulse overcurrent pro-<br>tection circuit.<br>Normally, we recommend adding an external<br>filter for this input. If overcurrent continues<br>for several cycles, the IC determines that the<br>operation is erroneous, thus triggering the<br>latch protection function.                                                                                                                                                                                                                       | V <sub>REF</sub><br>CLM(-)(4) |

| 5       | GND      |     | IC ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | т <sup>5</sup> т              |

## ■ Pin Descriptions (continued)

| Pin No. | Pin name        | I/O | Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Equivalent Circuit                                                     |

|---------|-----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| 6       | Out             | Ο   | Output used to directly drive a power MOSFET.<br>A totem pole structure is adopted in this<br>output circuit.<br>The absolute maximum ratings for the output<br>current are:<br>Peak: ±1 A<br>DC: ±150 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V <sub>CC</sub>                                                        |

| 7       | V <sub>CC</sub> |     | Power supply.<br>This pin monitors supply voltage and has the<br>threshold for the start, stop, OVP, and OVP<br>reset levels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                      |

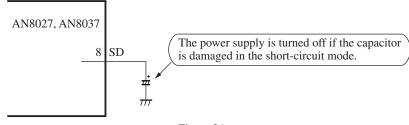

| 8       | SD              | Ι   | This pin is used in RM (remote), OVP (over-<br>voltage protection), and timer latch.<br>RM:<br>The IC is in remote operation if this pin is<br>short-circuited to the ground and the output<br>of the IC is turned off.<br>OVP:<br>When overvoltage signal of the power sup-<br>ply is detected and high is inputted to the ter-<br>minal, it turns off the internal circuit. At the<br>same time, it holds that condition (latch).<br>Timer latch:<br>It detects the output voltage fall due to the<br>overcurrent condition of the power supply<br>output through the current level inputted to<br>FB. When the I <sub>FB</sub> decreases under the current<br>of certain value, the charge current flows in<br>the capacitor which is connected to this ter-<br>minal. Then, when the capacitor is charged<br>up to the threshold voltage of the OVP, the<br>OVP works so that the IC could keep the op-<br>eration stop condition. | V <sub>CC</sub><br>OVP 3.9 V<br>Comp. 3.9 V<br>RM 0.1 V<br>Comp. 25 μA |

| 9       | FB              | Ι   | Connection for the photocoupler used for the<br>power supply output error-voltage feedback.<br>This input can decrease the photocoupler dark<br>current by about 200 µA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>REF</sub><br>V <sub>FB</sub><br>TTT I <sub>FB</sub> 9 TTT       |

#### Application Notes

#### [1] Operation descriptions

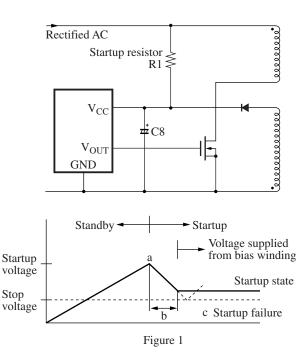

- 1. Start/stop circuit block

- Startup mechanism

After the AC voltage is applied and the supply voltage due to the current in the startup resistor reaches the startup voltage and the IC begins to operate, drive of the power MOSFET begins. This causes a bias in the transformer, and the supply voltage is provided to the IC from the bias winding. (This is point a in figure 1.) During the period between the point when the startup voltage is reached, and the point when the bias winding can generate a voltage enough to supply the IC, the IC supply voltage is provided by the capacitor (C8) connected to  $V_{CC}$ . Since the supply voltage falls during this period (area b in figure 1), if the supply voltage falls below the IC stop-voltage before an adequate supply voltage can be provided by the bias winding, it will not be possible to start the power supply. (This is the state at point c in figure 1.)

Functions

This IC includes a function that monitors the  $V_{CC}$  voltage. It starts IC operation when  $V_{CC}$  reaches the startup voltage (14.9 V typical), and stops operation when the voltage falls below the stop voltage (8.6 V typical). Since a large voltage difference (6.3 V typical) is taken between the start and stop voltages, it is easy to select values for the start resistor and the capacitor connected to  $V_{CC}$ .

Note) To start up the IC operation, the startup current which is a pre-start current plus a circuit drive current is necessary. Set the resistance value so as to supply a startup current of  $400 \ \mu$ A.

#### 2. Oscillation circuit

The oscillation circuit makes use of the charge and discharge of current to and from the capacitor  $C_{CF}$  connected to the CF pin (pin 3) to determine the switching timing of the power MOSFET.

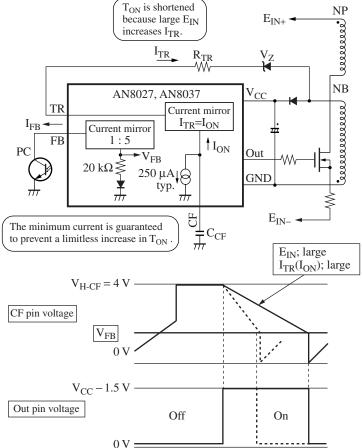

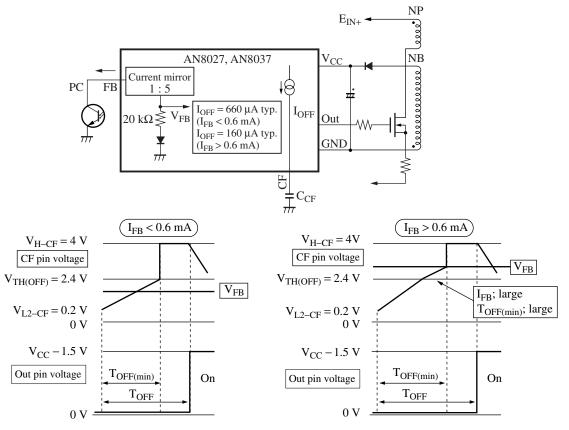

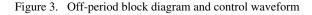

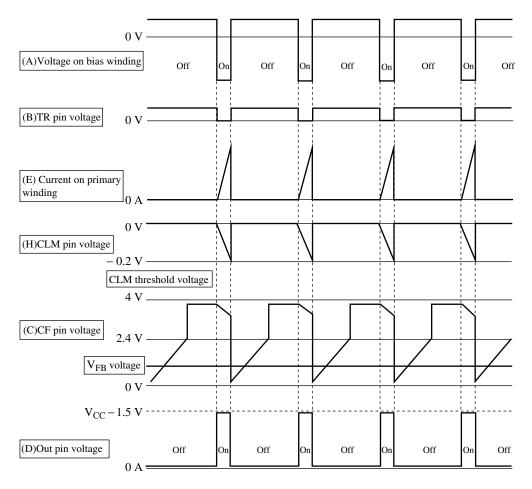

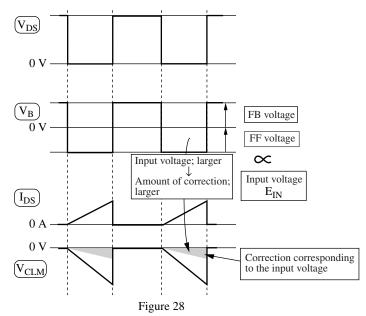

The IC is in constant voltage control by changing the on-period of the power MOSFET without making offperiod change while the IC is in normal (RCC continuous) operation mode. At that time, the on-period is controlled by directly changing the output pulse width of the oscillation circuit, and the maximum on-period can be adjusted with input voltage compensation by detecting the input voltage with the flow of current from the TR pin (TR source current). Refer to figure 2. When the IC is in standby mode (for light loads), the stable, efficient control of the IC is ensured by detecting the flow of current from the FB pin ( $I_{FB}$ ) and changing the off-period for a decrease in frequency. Refer to figure 3.

The following provides information on how to set on- and off-period.

• Setting the on-period

The output on-period is the discharge period when the CF pin is between the peak value oft  $V_{\text{H-CF}}$  = 4 V (typical) and  $V_{\text{FB}}$  .

An approximate on-period of the power MOSFET is obtained from the following formula. Refer to figure 2.

$$\begin{split} \Gamma_{ON} &= C_{CF} \times (V_{H-CF} - V_{FB}) / I_{ON} \\ & \text{whereas, } V_{H-CF} = 4 \text{ V typ.} \\ & I_{ON} = I_{TR} + 250 \text{ } \mu\text{A typ.} \\ & I_{TR} = (E_{IN} \times \text{NB}/\text{NP} - V_Z) / R_{TR} \\ & V_{FB} = 0.7 \text{ V typ.} (I_{FB} \leq 200 \text{ } \mu\text{A}) \\ & V_{FB} = 4 \text{ } k\Omega \times I_{FB} \text{ typ.} (I_{FB} > 200 \text{ } \mu\text{A}) \end{split}$$

- [1] Operation descriptions (continued)

- 2. Oscillation circuit (continued)

- Setting the on-period (continued)

- T<sub>ON</sub> : On-period

- $C_{CF}\ :$  Value of a capacitor connected to CF pin

- $V_{FB}$  : Voltage internally converted from feedback signal  $I_{FB}$

- $V_{H-CF}$ : CF upper limit voltage

- I<sub>ON</sub> : On-period discharge current

- $I_{TR}$  : Flowing current at TR pin

- $E_{IN}$  : Voltage on primary winding

- NB : Number of turns in the bias winding

- NP : Number of turns in the primary winding

- V<sub>Z</sub> : Voltage on Zener diode connected to bias winding

- $R_{TR}\ \ \, :$  Value of a resistor connected to the TR pin

The power MOSFET is turned off if the voltage at the CLM pin reaches the pulse-by-pulse overcurrent protection threshold voltage (i.e., -200 mV typical) when the overcurrent protection function of the IC is operating.

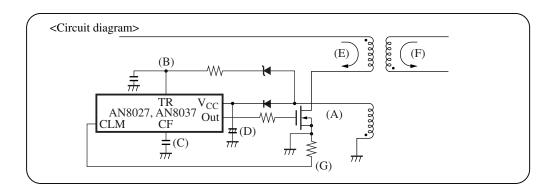

Figure 2. On-period block diagram and control waveform

The maximum on-period can be used for overcurrent protection. When the input voltage is low, the maximum on-period overcurrent protection is possible. When the input voltage is high, the CLM pulse-by-pulse overcurrent protection is possible.

- [1] Operation descriptions (continued)

- 2. Oscillation circuit (continued)

- Setting the off-period

The minimum off-period is the charge period from  $V_{L-CF} = 0.2 \text{ V}$  (typical) to  $V_{TH(OFF)}$  or  $V_{FB}$ .

An approximate minimum off-period of the power MOSFET is obtained from the following formula. Refer to figure 3.

$$\begin{split} T_{OFF(min)} &= C_{CF} \times V_{TH(OFF)} \ / \ I_{OFF1} \quad (I_{FB} \leq 0.6 \ \text{mA}) \\ &= \{C_{CF} \times V_{TH(OFF)} \ / \ I_{OFF1}\} + \{C_{CF} \times (V_{FB} - V_{TH(OFF)}) \ / \ I_{OFF2}\} \quad (I_{FB} > 0.6 \ \text{mA}) \\ &\quad V_{TH(OFF)} = 2.4 \ V \ typ. \\ &\quad I_{OFF1} = 660 \ \mu A \ typ. \\ &\quad I_{OFF2} = 160 \ \mu A \ typ. \\ \hline T_{OFF(min)} : Minimum \ off-period \\ C_{CF} &: Value \ of \ a \ capacitor \ connected \ to \ the \ CF \ pin \\ V_{FB} &: Voltage \ internally \ converted \ from \ feedback \ signal \ I_{FB} \\ V_{TH(OFF)} : Threshold \ voltage \ of \ V_{FB} \ to \ extend \ off-period \\ I_{OFF1} &: Charge \ current \ until \ CF \ pin \ voltage \ increases \ from \ 0.2 \ V \ to \ 2.4 \ V \\ I_{OFF2} &: Charge \ current \ until \ CF \ pin \ voltage \ increases \ from \ 2.4 \ V \ to \ V_{FB} \end{split}$$

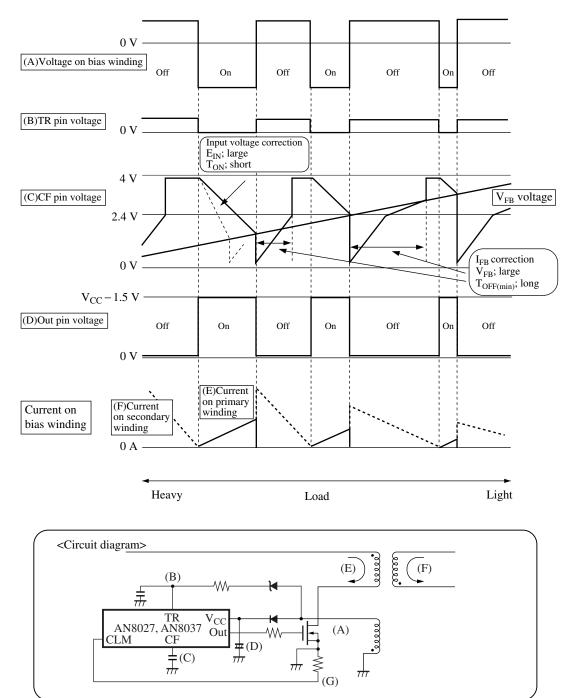

When the IC is in local resonance operation, the off-period is determined by the longer one of either the time required for the input voltage on the TR pin to drop below the threshold voltage or the minimum off-period ( $T_{OFF(min)}$ ) specified by the  $C_{CF}$ .

Thus the power MOSFET is in continuous on/off operation.

- [1] Operation descriptions (continued)

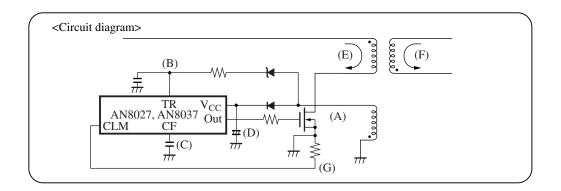

- 3. Control waveform timing chart

- 1) Normal (RCC continuous) operation mode

- [1] Operation descriptions (continued)

- 3. Control waveform timing chart (continued)

- 2) Standby (Intermittent) mode (for light loads)

- [1] Operation descriptions (continued)

- 3. Control waveform timing chart (continued)

- 3) Pulse-by-pulse overcurrent protection (CLM) operation

- [1] Operation descriptions (continued)

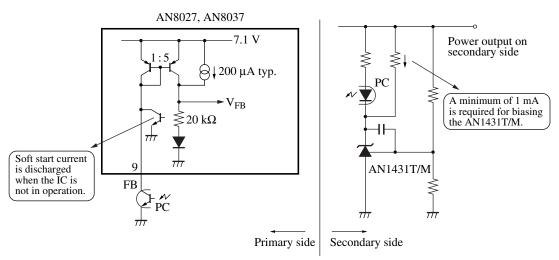

- 4. Power supply output control system ( $I_{FB}$ : feedback)

Constant-voltage control of the power supply output is performed by changing the on- and off-period of the power MOSFET. The on- and off-period are controlled with the photocoupler connected to the FB pin (Pin 9). The photocoupler adjusts the current at the FB pin according to the signal that is output from the output voltage detection circuit on the secondary side and changes the  $V_{FB}$  voltage. Refer to figure 4.

The higher the AC input voltage is and the lower the load current is, the higher the current flow from FB pin, the higher the  $V_{FB}$  voltage, and the shorter the on-period (or longer the off-period in standby mode) will be.

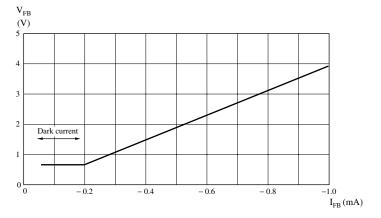

Note that a current cancellation capacity of about  $200 \,\mu\text{A}$  is provided to compensate for the dark current of the photocoupler. Refer to figure 5.

Figure 4. Power output control

Figure 5. Feedback current vs.  $V_{FB}$  characteristics

#### 5. Soft start

When a power supply is started, it starts up in an overload state due to the capacitor connected to the power supply output. At that moment, the output voltage is low. Therefore, the IC in usual voltage regulation tries to start up the power output circuit at a maximum duty cycle. Although the IC tries to limit the current by the pulse-by-pulse overcurrent protection at the CLM pin, the pulses cannot be suppressed to zero due to delays caused by the filter. As a result, high current flows to the main switch (i.e., power MOSFET) and to the diode on the secondary side. Therefore, in the worst case, these components are totally broken. To prevent this, soft start is used to suppress inrush currents at power supply startup.

#### [1] Operation descriptions (continued)

5. Soft start (continued)

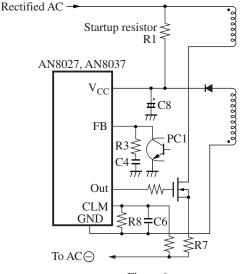

As shown in figure 6, connect R3 and C4 between the FB pin (Pin 9) and GND pin (Pin 5) so that the switching regulator will be in soft start operation. When the voltage supplied to the IC reaches the start voltage and the operation of the startup circuit begins, an open bias voltage of approximately 6.4 V is output to the FB pin. As a result, the charge current I<sub>FB</sub> flows into C4 from the FB pin. Then the switching regulator starts up at high V<sub>FB</sub>, thus performing output control while the T<sub>ON</sub> period is short. The voltage difference between both edges of C4 rises according to the time constant determined by R3 and C4, thus decreasing I<sub>FB</sub> with the lapse of time and increasing the T<sub>ON</sub> period gradually.

The above operation increases the flow of current to the power MOSFET gradually after the switching regulator is turned on, thus suppressing the inrush current. However, this reduces the transient response of the feedback loop, so care is required in designing this circuit.

Figure 6

• Notes on selecting R3

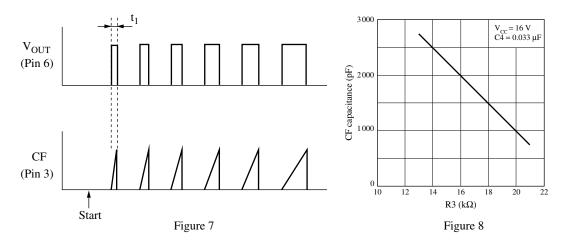

The oscillation circuit of this IC is designed under the condition that the  $T_{ON}$  period is definite. If excessively low resistance value for R3 is selected, the slope of the triangular wave on the CF pin immediately after the startup may become extremely steep, leading to malfunction of the oscillation circuit. Accordingly, we recommend that you adjust R3 so that the drive pulse width  $t_1$  immediately after the startup is 0.5 ms or greater. (Refer to figure 7.)

Note that the drive pulse width  $t_1$  depends on the capacitance value of the  $C_{CF}$  that is connected to the CF pin (Pin 3). Figure 8 indicates recommended values of R3 corresponding to the capacitance value  $C_{CF}$ .

(In actual mounting conditions, the correlation shown in figure 8 may deviate slightly.)

- [1] Operation descriptions (continued)

- 5. Soft start (continued)

- Effective period for the soft start

The effective period for the soft start with the connection of R3 and C4 to the FB pin is approximately calculated by the following formula.

[Approximate formula]

$t_{SS} = R3 \times C4 \ (s)$

It is thought that the effectiveness of the above formula is weakened because of the following reason: The voltage difference between both ends of C4 rises up to 63% of the voltage at the FB pin within the time constant  $\tau$  (= R3 × C4), resulting in decrease of the charge current I<sub>FB</sub>, although it depends on the value of R3.

Note that if you increase the capacitance value of C4 unnecessarily, it would decrease the sensitivity of the feedback by the photocoupler.

• Soft start at the re-startup

This IC includes a discharge circuit to instantly discharge charged electrons in the capacitor connected to the FB pin in order to ensure the soft start at the re-startup.

Conditions for the operation of the discharge circuit are as follows:

- 1)  $V_{CC}$  has become the stop voltage or below. (at the normal operation)

- 2)  $V_{CC}$  has become the OVP reset threshold voltage or below. (at the OVP operation)

6. Notes on the feedback control

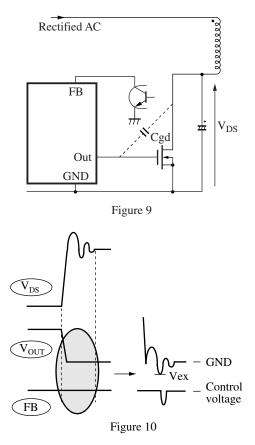

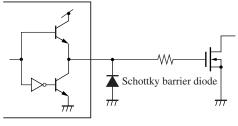

If the IC output pin (pin 6) falls to a negative voltage lower than that of the GND pin, the startup operation may fail or the output oscillation may become unstable.

ICs in general, not just this IC, do not respond well when negative voltages lower than the ground level are applied to their pins. (Except for special applications.) This is because parasitic device operations may be induced when negative voltages are applied due to the structure of ICs themselves.

In the case mentioned above, when the IC output ( $V_{OUT}$ ) is turned off, the power MOSFET drain-to-source voltage,  $V_{DS}$ , jumps from a low voltage to a high voltage. The voltage chattering that occurs at this time is superposed on  $V_{OUT}$  through the parasitic capacitance Cgd between the power MOSFET gate and drain, and generates a negative voltage with respect to the pin. No problems occur if the peak voltage, Vex, of this negative voltage does not exceed the parasitic device conduction voltage (about – 0.7 V).

However, the amplitude of the chattering is larger for higher input voltages and for larger leakage inductance in the transformer used. Also, the influence of this phenomenon becomes more noticeable for the larger Cgd of the power MOSFET used, and the Vex peak value also increases. If the parasitic device conduction voltage is exceeded, then, in this IC, the parts of the circuit around the feedback circuit (FB) (in particular, the FB discharge circuit) are influenced. This can cause momentary drops in the FB pin voltage (the control voltage), and as a result increase the FB current I<sub>FB</sub> and thus does not allow the drive pulse on-period T<sub>ON</sub> to be increased. It may also prevent stabilization of the circuit. These are symptoms of the case described here. (Refer to figures 9 and 10.)

- [1] Operation descriptions (continued)

- 6. Notes on the feedback control (continued)

#### [Countermeasures]

If an application exhibits the symptoms of the case described above, or similar symptoms, first insert a Schottky barrier diode between  $V_{OUT}$  and GND. It is not possible to completely remove the mechanism described above from a power supply system. It is also not possible to prevent levels from being pulled down to negative voltages in the control IC itself. Therefore, the most important point in designing countermeasures is to prevent such negative voltages from reaching the parasitic device conductance voltage.

Note) If a Schottky barrier diode is added to the circuit and the condition improves initially but the symptoms reappear when the input voltage or other parameter is increased, try replacing the Schottky barrier diode with one that has a larger forward current (both peak and average values). The current capacity of the Schottky barrier diode is sometime insufficient.

#### (Reference)

The following our Schottky diodes are available.

| Part No.           | Reverse voltage | Forward current (average) | Forward current (peak) |

|--------------------|-----------------|---------------------------|------------------------|

| MA2C700A (MA700A*) | 30 V            | 30 mA                     | 150 mA                 |

| MA2C723 (MA723*)   | 30 V            | 200 mA                    | 300 mA                 |

| MA2C719 (MA719*)   | 40 V            | 500 mA                    | 1 A                    |

Note) \*: Former part number

#### 7. Local resonance operation (power MOSFET turn-on delay circuit)

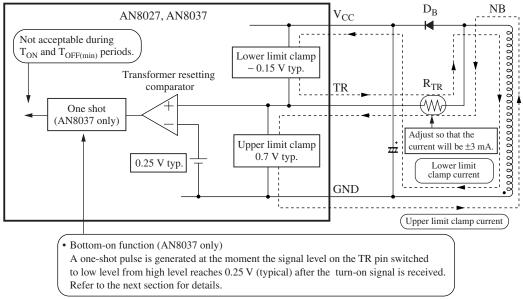

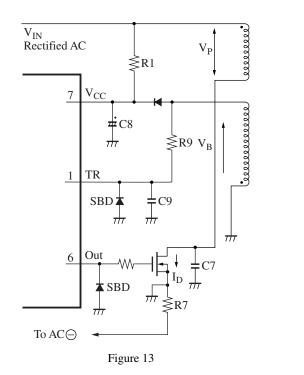

Local resonance operation by using the AN8027 or AN8037 is possible with circuits as shown in figure 13. C7 is the resonance capacitor, and R9 and C9 form a delay circuit for adjusting the power MOSFET turn on time. When the power MOSFET is off, the voltage that occurs in the drive winding is input to the TR pin (pin 1) through R9 and C9. The power MOSFET will be held in the off state while a high level (a level higher than the threshold voltage, which is 0.25 V typical) is input to the TR pin.

The TR pin also has a clamping capability for upper and lower limit voltages. The upper limit voltage is clamped at 0.7 V (typical) (sink current: -3 mA), and the lower limit voltage is clamped at about -0.15 V typical (source current: 3 mA). (Refer to figure 11.)

The power MOSFET off-period is determined by the longer period of the following two periods: the period until the TR pin input voltage becomes lower than the threshold voltage as the bias winding voltage falls after the transformer discharges its energy, and the minimum off-period ( $T_{OFF(min)}$ ) stipulated by the internal oscillator. (Refer to the "Setting the off-period" section in the "Operating descriptions, 2. Oscillation circuit.") As a result, ringing in the bias winding does not be regarded as a turn on signal during the minimum off-period.

- [1] Operation descriptions (continued)

- 7. Local resonance operation (power MOSFET turn-on delay circuit) (continued)

Figure 11

#### 8. Bottom-on function (AN8037 only)

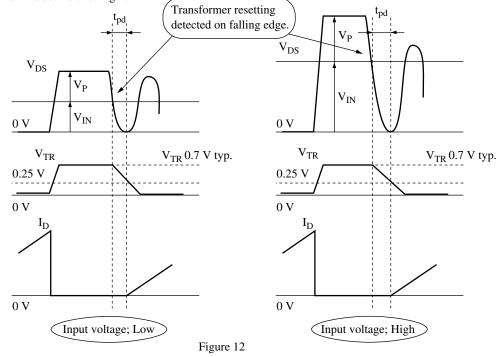

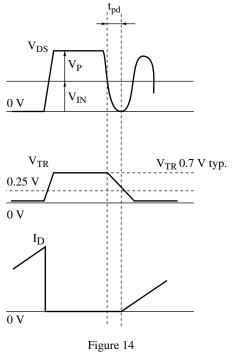

Unlike the AN8027 or our conventional AN8026, AN8028, or AN8029 IC, which detects transformer resetting with the high or low level in comparison to the threshold voltage on the TR pin, the AN8037 detects transformer resetting on the falling edge across the threshold voltage.

This ensures the reliable local resonance operation of the IC regardless of input voltage fluctuations in a wide input range for worldwide use, thus eliminating difficulty in turning on the power MOSFET when  $V_{DS}$  is close to the minimum value. Refer to figure 12.

Panasonic

- [1] Operation descriptions (continued)

- 8. Bottom-on function (AN8037 only) (continued)

Select the constants of R9 and C9 to determine the turn-on delay time so that the power MOSFET will be turned on at a frequency of half the resonant frequency. Practically, refer to figure 12 and determine the turn-on delay time so that the power MOSFET will be turned on at  $V_{DS} = 0$  V. The approximate resonant frequency can be obtained from the following formula.

$$f_{SYNC} = \frac{1}{2\pi \sqrt{L \cdot C}}$$

[Hz] C: resonant capacitance

L: inductance of primary winding of transformer

The turn-on delay time  $t_{pd(ON)}$  to turn on the power MOSFET at a frequency of half the resonant frequency is, therefore, as follows.

$t_{pd(ON)} = \pi \sqrt{L \cdot C} [s]$

Note that since insertion of the resonance capacitor results in increased losses, using the parasitic capacitance of the power MOSFET itself should also be considered. However, in this case the sample-to-sample variations and temperature variations should be considered.

9. Notes on R9 and C9 value selection

If an excessively low value is used for R9, the current flowing into the TR pin after power supply startup will exceed the maximum rating for the IC, and incorrect operation (in the worst case, destruction of the device) may occur. We recommend using a value of R9 in the range that satisfies the following conditions.

$\frac{V_{B(-)} - \text{The TR lower limit clamp voltage } (-0.15 \text{ V typical})}{R9} \ge -3 \text{ mA}}{V_{B(-)}\text{: negative peak voltage}}$   $\frac{V_{B(+)} - \text{The TR upper limit clamp voltage } (1.5 \text{ V typical})}{R9} \le 3 \text{ mA}}{V_{B(+)}\text{: positive peak voltage}}$

Adjust t<sub>PD(ON)</sub> with C9 by taking the inductance and resonant capacitance of the transformer into consideration.

#### [1] Operation descriptions (continued)

10. Output block

This IC adopts a totem pole (push-pull) structure output circuit in which npn transistors as shown in figure 15 sinks and sources current to rapidly drive the power MOSFET which is a capacitive load.

This circuit provides maximum sink and source currents of  $\pm 0.1$  A (DC), and peak currents of  $\pm 1.0$  A. Furthermore, this circuit has a sink capability of 1 mA (typical) even when the supply voltage has fallen under the stop voltage, and thus can turn off the power MOSFET reliably.

The main requirement on the control IC in this type of power supply is the ability to provide a large peak current. That is to say, a high average current is not required in steady state operation. This is because the power MOSFET is a capacitive load, and while a large peak current is required to drive such a load rapidly, once the load has been charged or discharged a much smaller current suffices to retain that state.

This IC has a guaranteed peak current capability of  $\pm 1$  A, values which were determined by considering the capacitance of the power MOSFETs that will be used.

The parasitic inductance and capacitance of the power MOSFET can cause ringing, and pull down the output pin below the ground level. If the output pin goes to a negative voltage that is larger than the voltage drop of the diode, this state can turn on the parasitic diode formed by the collector of the output npn transistor and the substrate. Insert a Schottky barrier diode between the output and ground if this is a problem. (Refer to figure 15.)

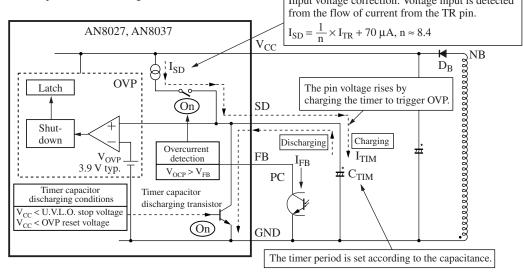

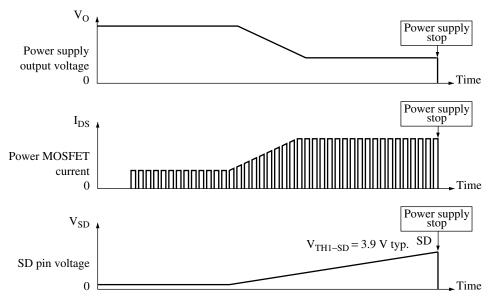

#### 11. Timer latch

The pulse-by-pulse overcurrent protection function by itself cannot fully protect the transformer, the first recovery diode or Schottky diode on the secondary side, or the power MOSFET, if the power output is overloaded or short-circuited for a certain period. If the overcurrent state continues for a certain period or longer time, the timer latch function makes it possible to interrupt the IC in a certain period by charging the capacitor connected to the SD pin.

The overload of the power output or short-circuiting of the power output is monitored as a voltage drop in power output, at which time the pulse-by-pulse overcurrent protection is in operation. The voltage drop in power output is detected as a decrease in current through the FB current feedback pin (pin 9). If this current is less than a certain value, the on-chip comparator of the IC is in inverted operation to provide constant current to the SD pin. Refer to figure 16.

Then external capacitor connected to the SD pin is charged and the voltage on the SD pin rises to the SD operating threshold voltage (i.e., 3.9 V typical), overvoltage protection (OVP) is triggered, and the operation of the IC is suspended. Refer to figure 17.

Figure 16

- [1] Operation descriptions (continued)

- 11. Timer latch (continued)

Figure 17. Basic timer latch operation

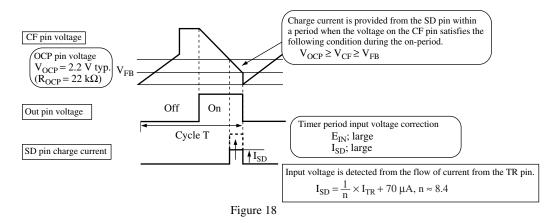

#### 12. Setting the timer period

The period between the detection of the erroneous power output and the moment OVP is triggered (hereinafter called timer period) needs to be longer than the rise time of the power supply. Since at operation start the IC is in the same condition as the overload or output short-circuit condition, if the timer period is shorter, the power supply works latch and can not start.

Therefore, the IC has a design making it possible to adjust the timer period with the external capacitor connected to the SD pin. Make sure, however, that the capacitor is not too high, otherwise the power supply may be damaged.

- [1] Operation descriptions (continued)

- 12. Setting the timer period (continued)

Timer period  $(T_{TIM})$  is obtained from the following formula.

$$\begin{split} T_{TIM(S)} &= \{C_{SD} \times (V_{TH1-SD} - V_{STB-SD})\} / I_{SD(AVE)} \\ V_{TH1-SD} &= 3.9 \ V \ typ. \\ V_{STB-SD} &= 1.6 \ V \ typ. \\ I_{SD(AVE)} &= I_{SD} \times T_{SD} \ / T \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{SD} &= C_{CF} \times (V_{OCP} - V_{FB}) / I_{ON} \\ T_{CF} &= C_{CF} \times (V_{CP} - V_{FB}) / I_{ON} \\ T_{CF} &= C_{CF} \times (V_{CP} - V_{FB}) / I_{ON} \\ T_{FB} &= C_{CF} \times (V_{CP} - V_{FB}) / I_{ON} \\ T_{FB} &= C_{CF} \times (V_{CP} - V_{FB}) / I_{ON} \\ T_{FB} &= C_{CF} \times (V_{CP} - V_{FB}) / I_{ON} \\ T_{FB} &= C_{CF} \times (V_{CP} - V_{FB}) / I_{ON} \\ T_{CF} &= C_{CF} \times (V_{CP} - V_{FB}) / I_{ON} \\ T_{FB} &= C_{CF} \times (V_{CP} - V_{FB}) / I_{CP} \\ T_{CF} &= C_{CF} \times (V_{CP} - V_{FB}) / I_{CP} \\ T_{CF} &= C_{CF} \times (V$$

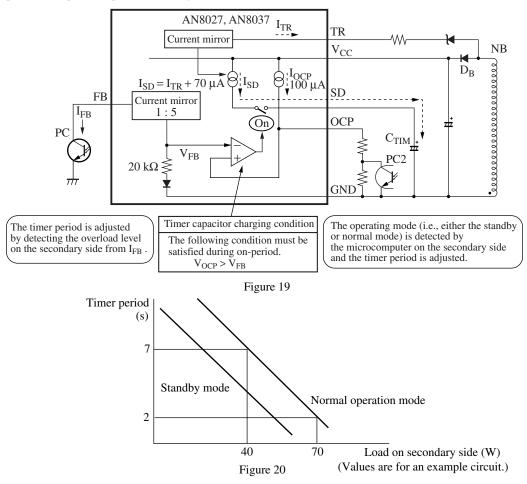

By detecting the overload level on the secondary side from  $I_{FB}$  and changing  $T_{SD}$ , the timer period can be adjusted according to the overload level. Furthermore, in the application circuit, the timer period can be adjusted in both standby and normal modes. To enable this, let the microcomputer on the secondary side detect the operating mode (i.e., either the standby or normal mode) of the IC to vary the value of the resistor connected to the OCP pin with the photocoupler. Refer to figures 19 and 20.

- [1] Operation descriptions (continued)

- 13. Overvoltage protection (OVP) circuit

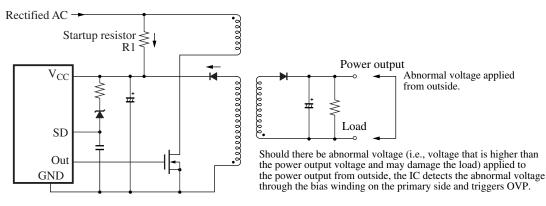

OVP stands for overvoltage protection. The overvoltage protection circuit is a self-diagnostic function that shuts down the power supply to protect the load if a voltage that is significantly and abnormally higher than the normal output voltage occurs in the power supply output, due to, for example, a malfunction in the control system or an abnormal voltage applied externally. (Refer to figure 22.)

Basically, the overvoltage protection circuit should be designed so that the  $V_{CC}$  pin voltage of the IC can be monitored. Since the  $V_{CC}$  pin voltage is normally supplied from the transformer bias winding, this voltage is proportional to the secondary side output voltage. Thus the overvoltage protection circuit operates when an overvoltage occurs in the secondary side output.

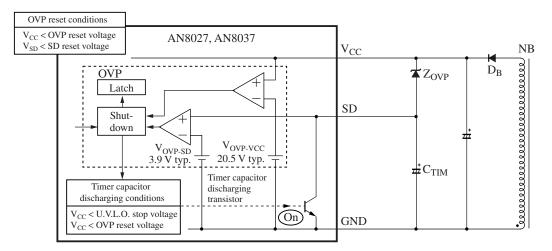

- 1) If, as a result of an abnormality in the power supply output, the voltage input to the  $V_{CC}$  pin exceeds the threshold value (20.5 V typical), the IC internal reference voltage is shut down, and all control operation is stopped. The IC then holds this state. If latching at a voltage lower than the threshold value is required, connect a Zener diode between the  $V_{CC}$  and SD pins as shown in figure 22 and take method 2) below to set the voltage.

- 2) If the SD pin input voltage exceeds a threshold value of 3.9 V typical, the IC internal reference voltage is shut down, and all control operation is stopped. The IC then holds this state.

- 3) OVP is reset in two methods. One is to decrease the output voltage on the secondary side so that the  $V_{CC}$  pin voltage is less than the OVP reset voltage, i.e., 8.1 V typical. The other is to decrease the SD pin input voltage  $(V_{SD})$  to a value less than the SD reset voltage, i.e., 0.7 V typical, by external resetting. If  $V_{SD}$  is less than 0.1 V typical, however, the IC will be in remote operation to shut off the output.

The IC incorporates a circuit that discharges a constant current of approximately 25 mA from the capacitor connected to the SD pin for the re-start operation. The operation of this circuit is stopped when the SD pin voltage drops to 1.5 V or below. Refer to figure 21.

Figure 21

The following is a formula to allow the IC to be in OVP operation with the SD pin in the above method 2).  $V_{th(OUT)} = \frac{V_{(OUT)} \text{ Secondary side output voltage under normal operation}}{V_{CC} \text{ pin voltage under normal operation}} \times V7$

$V7 = V_{TH-SD1} + V_Z$

V<sub>th(OUT)</sub>: Secondary side output overvoltage threshold value

V<sub>TH-SD1</sub>: SD operating threshold value

V<sub>Z</sub> : Zener voltage (externally connected to OVP pin)

- [1] Operation descriptions (continued)

- 13. Overvoltage protection (OVP) circuit (continued)

- Operating supply current characteristics

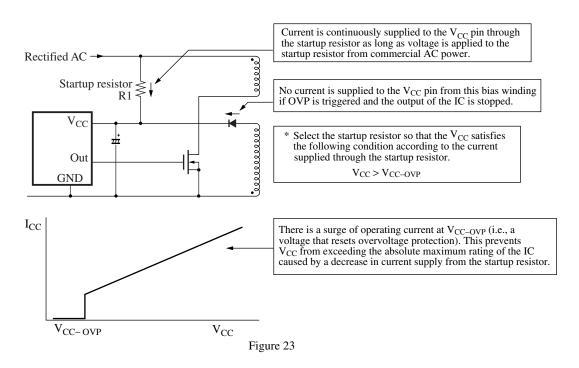

When the OVP circuit operates and the power supply current drops, this can induce a rise of the supply voltage  $V_{CC}$ . In the worst case, it may exceed the IC's guaranteed breakdown voltage (24 V).

Therefore, the circuit is provided with characteristics that cause the supply current to rise in constant resistance mode when the OVP circuit operates, and thus prevent increases in the supply voltage.

Due to these characteristics, if the supply voltage  $V_{CC}$  when the OVP circuit operates is stabilized at a value (note that this value depends on the value of the startup resistor) that is larger than the OVP release voltage, the OVP circuit will not be reset as long as the AC input is not cut. (Refer to figure 23.) Note that this does not apply to an external reset.

- [1] Operation descriptions (continued)

- 14. Remote on/off function

- The SD pin of the AN8027 or AN8037 has a remote on/off function besides the following functions.

- Timer latch function

- Overvoltage protection function

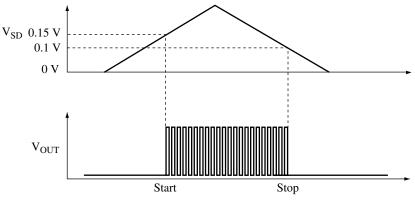

The remote on/off function turns the power supply output on and off remotely with external signals. Furthermore, this function turns the power supply off by setting the SD pin voltage extremely close to the ground voltage (i.e., 0 V) if the capacitor connected to the SD pin for timer latch use is damaged in the short-circuit mode. Refer to figure 24.

Figure 24

On the other hand, a hysteresis width of 50 mV (typical) is provided for threshold SD voltage to prevent the output of the IC in remote operation from chattering. Refer to figure 25.

Figure 25

- [1] Operation descriptions (continued)

- 15. Overcurrent protection circuit (pulse-by-pulse overcurrent protection)

This circuit uses the fact that overcurrents in the power supply output are proportional to the current flowing in the primary side main switch (power MOSFET). This circuit limits overcurrents in the power supply output by constraining the upper limit of the pulse current flowing in the main switch, and thus protects components sensitive to excessive current.

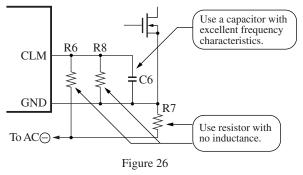

The current flowing in the main switch is detected by connecting a resistor between the power MOSFET source and ground and monitoring the voltage that appears across that resistor. When the power MOSFET is turned on and the CLM (current limit) threshold voltage is detected, the output is turned off. This controls the circuit so that a current in excess of that limit cannot flow by turning off the power MOSFET. The CLM threshold voltage is about – 0.2 V typical with respect to ground at  $T_a = 25^{\circ}$ C. While this control operation is repeated every cycle, once an overcurrent is detected, the off state is held for the remainder of that cycle, and the circuit is not turned on until

the next period. This type of overcurrent detection is called "pulse-by-pulse overcurrent detection."

R6 and C6 in figure 26 form a filter circuit that rejects noise generated due to the incidental equivalent parasitic capacitance when the power MOSFET is on.

For the grounding point, we recommend that the power MOSFET source pin and the IC GND pin be connected over as short a distance as possible.

Notes on the detection level precision

This overcurrent detection level is reflected on the operating current level of the power supply overcurrent protection function. Therefore, if this detection level varies with sample-to-sample variations or with temperature, the operating current level of the overcurrent protection function of the power supply itself will vary. Since variations in this level imply a need for increased ruggedness in parts used, or even the destruction of circuit components, we have increased the precision of this IC as much as possible.

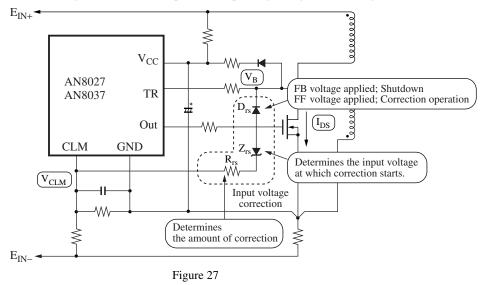

16. Overcurrent protection circuit (input voltage correction function)

As an extended application, this section presents a circuit design that applies a correction so that the overcurrent protection operating point is held fixed with respect to variations in the input voltage. This circuit uses the proportional relationship between the input voltage and the inverted voltage of the bias winding, and superposes inverted voltage of the bias winding on the overcurrent protection operating voltage. (Refer to figures 27 and 28.)

- [1] Operation descriptions (continued)

- 16. Overcurrent protection circuit (input voltage correction function) (continued)

#### 17. Overcurrent protection circuit (Timer latch protection)

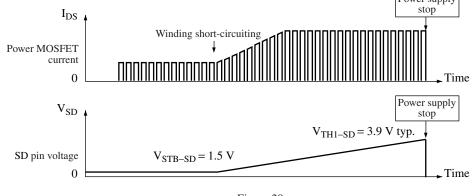

The CLM pin is used for timer latch in addition to pulse-by-pulse overcurrent protection.

This is because the pulse-by-pulse overcurrent protection alone cannot prevent the power MOSFET connected to the Out pin from damage in most cases if the primary winding is short-circuited and excessive current flows to the power MOSFET.

If an excessive current flows to the power MOSFET for a certain period due to the short-circuiting of the primary winding, this circuit charges the capacitor connected to the SD pin, shut down the power supply, and holds this state. (Refer to figure 29.)

Figure 29

The timer period (T<sub>CLM</sub>) is obtained from the following formula.

[Setting the timer period]

|   | $T_{CLM} = \{C_{SD} \times (V_{TH1-SD} - V_{STB-SD})\}/I_{CLM(AVE)}$ | C <sub>SD</sub> : Capacitor connected to SD pin            |

|---|----------------------------------------------------------------------|------------------------------------------------------------|

|   | $I_{CLM(AVE)} = I_{CLM} \times T_{OFF} / T$                          | V <sub>TH1-SD</sub> : Shutdown operating threshold voltage |

|   | $(I_{CLM} = 100 \ \mu A)$                                            | V <sub>STB-SD</sub> : Shutdown standby voltage             |

|   |                                                                      | $I_{CLM}$ : CLM timer charge current (100 $\mu$ A)         |

| ( | Example: If $T_{OFF}$ / T is 50%, $C_{SD}$ is 10 $\mu$ F.            | T <sub>OFF</sub> : Off-period                              |

| ļ | $T_{IM} \approx 500 \text{ ms}$                                      | T : Cycle                                                  |

|   | \/                                                                   |                                                            |

[2] Package power dissipation

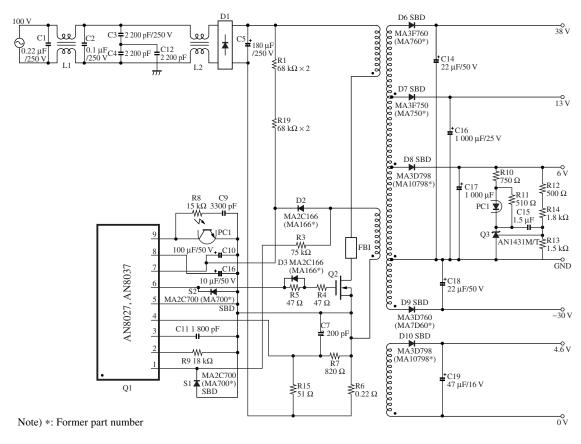

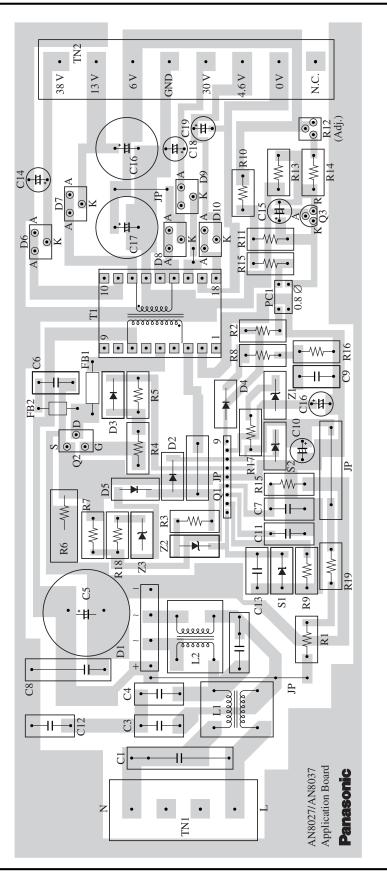

- Application Circuit Examples

- Circuit Diagram

- Application Circuit

Examples (continued)

- Evaluation board chart

## Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) If any of the products or technical information described in this book is to be exported or provided to non-residents, the laws and regulations of the exporting country, especially, those with regard to security export control, must be observed.

- (2) The technical information described in this book is intended only to show the main characteristics and application circuit examples of the products, and no license is granted under any intellectual property right or other right owned by our company or any other company. Therefore, no responsibility is assumed by our company as to the infringement upon any such right owned by any other company which may arise as a result of the use of technical information described in this book.

- (3) The products described in this book are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

- Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- Any applications other than the standard applications intended.

- (4) The products and product specifications described in this book are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions (operating power supply voltage and operating environment etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off and mode-switching. Otherwise, we will not be liable for any defect which may arise later in your equipment.

Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

- (6) Comply with the instructions for use in order to prevent breakdown and characteristics change due to external factors (ESD, EOS, thermal stress and mechanical stress) at the time of handling, mounting or at customer's process. When using products for which damp-proof packing is required, satisfy the conditions, such as shelf life and the elapsed time since first opening the packages.

- (7) This book may be not reprinted or reproduced whether wholly or partially, without the prior written permission of Matsushita Electric Industrial Co., Ltd.