# - Table of Contents -

| 1.   | General Description                         | 3  |

|------|---------------------------------------------|----|

| 2.   | Features                                    | 3  |

| 3.   | Functional Block Diagram                    | 4  |

| 4.   | Pin Description                             | 4  |

| 5.   | Pad Location                                | 6  |

| 6.   | ROM Map Configurations                      | 11 |

| 7.   | LCD Display RAM Map                         | 12 |

| 7.1. | 16 Gray Scale LCD Display RAM Map           | 14 |

| 7.2. | 4 Gray Scale LCD Display RAM Map            | 16 |

| 7.3. | Black and White LCD Display RAM Map         | 17 |

| 8.   | LCD Power Supply                            | 19 |

| 9.   | LCDC Control register                       | 21 |

| 10.  | Oscillators                                 | 22 |

| 11.  | General Purpose I/O                         | 24 |

| 12.  | Timer1                                      | 26 |

| 13.  | Timer2                                      | 27 |

| 14.  | Time Base                                   | 28 |

| 15.  | Watch Dog Timer                             | 29 |

| 16.  | Voice Output                                | 30 |

| 17.  | Low Voltage Detection/Reset                 | 34 |

| 18.  | Infrared output                             | 35 |

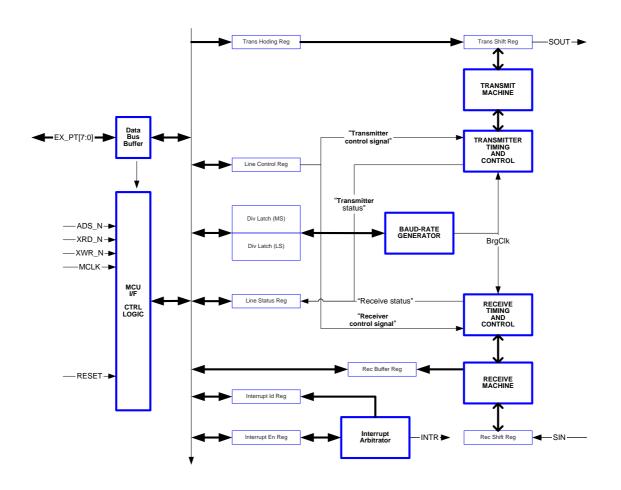

| 19.  | Universal Asynchronous Receiver/Transmitter | 37 |

| 19.1 | 1. Interface Registers                      | 38 |

| 19.2 | 2. Baud Rate Configuration Register         | 38 |

| 19.3 | 3. Interrupt & Identification Register      | 39 |

| 19.4 | 4. Line Control Register                    | 40 |

| 19.5 | 5. Line Status Register                     | 41 |

| 20. | Extension Register Access             | 42 |

|-----|---------------------------------------|----|

| 21. | Summary of Registers and Mask Options | 42 |

| 22. | Absolute Maximum Rating               | 45 |

| 23. | Recommended Operating Conditions      | 45 |

| 24. | AC/DC Characteristics                 | 45 |

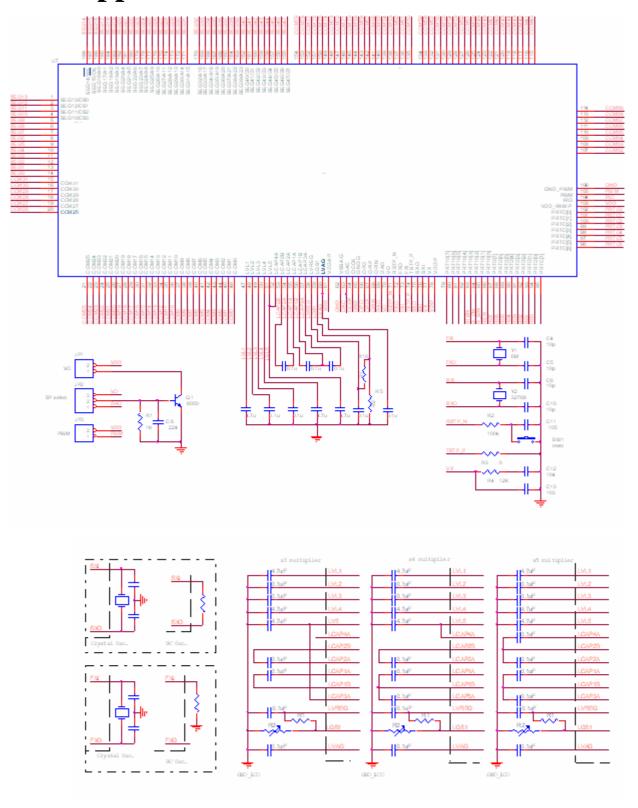

| 25. | Application Circuit                   | 47 |

| 26. | Important Note                        | 49 |

| 27. | Updated History                       | 49 |

# 1. General Description

HE84G752B is a member of 8-bit Micro-controller series developed by King Billion Electronics. External address and data buses are provided to access external memory. This chip has 4096 pixel, 16 gray-scale LCD driver built-in with 4 different configurations, and up to 34-bit general purpose I/O ports. The built-in OP comparator can be used with light, voice, temperature and humility sensor or used to detect the battery low. The 7/8 bits current-type D/A converter and PWM driver output provides the complete speech output solutions. The 512K bytes ROM and 3K bytes RAM can be used for the storage of large speech data, image and text, etc. An UART is included to provide the serial communication capability. IR output makes it suitable for remote control applications.

The instruction sets of HE80000 series is easy to learn and simple to use. There are only thirty-two instructions and four addressing modes. Most of instructions take only 3 oscillator clocks to complete. The performance and low power consumption make it suitable for battery-powered applications such as translator, data bank, educational toy, digital voice recorder, etc.

# 2. Features

✓ Operation Voltage:  $2.4V \sim 3.6V$

✓ Dual Clock System: Fast clock 32768 Hz ~ 8 MHz

Slow clock 32768 Hz

✓ Four operation modes: Fast, Slow, Idle, Sleep modes.

✓ Internal Program ROM: 256K bytes ✓ Internal Data ROM: 256K bytes

✓ Internal RAM: 3 K bytes (page0~page11)

- ✓ 24 bi-directional general-purpose I/O ports with push-pull or Open-Drain output type selectable for each I/O pin by mask option.

- ✓ Up to 2048 pixels 16, 4 gray-scale or Black/White LCD driver.

- ✓ Segment extender interface with KD83 and KD80.

- ✓ 4 LCD configurations (COM X SEG): 32 COM x 64 SEG.

- ✓ Built-in LCD power supply with regulator and 3, 4, and 5 times charge pump circuit.

- ✓ One 7/8-bit current-type D/A converter.

- ✓ One 7/8-bit PWM output.

- ✓ One built-in OP comparator.

- ✓ Built-in UART for serial communication.

- ✓ IR output.

- ✓ Low voltage reset: 2.2V

- ✓ Low voltage detection: 2.4V, 2.6V, 2.8V and 3.0V

- ✓ Two external interrupts, three internal timer interrupts and extension UART interrupt

- ✓ Watch dog timer to prevent deadlock condition.

- ✓ Two 16-bit timers and one time-base timer.

- ✓ Instruction set: 32 instructions, 4 addressing mode.

# 3. Functional Block Diagram

| SEG<br>COM                             | LCD<br>Driver            | 8 Bit CPU    | Fast Clock<br>OSC. | FXI, FXO       |

|----------------------------------------|--------------------------|--------------|--------------------|----------------|

| LVL[51], LGS1, LVREG<br>LCAP?A, LCAP?B | LCD Power<br>Supply      | 512 KB ROM   | Slow Clock<br>OSC  | SXI, SXO       |

| OLFR, OCCK                             | Segment Ext. Interface   | 3 KB RAM TC1 | PWM                | PWM            |

| SEGA, SEGD                             | Ext. Memory<br>Interface | TC2          | DAC                | VO, DAO        |

| PRTC, PRTD, PRT10, PRT17               | I/O Port                 | TB WDT       | OP Amp             | OPO,OPIN, OPIP |

| SIN, SOUT                              | UART                     | LVR<br>LVD   | IR                 | IRO            |

# 4. Pin Description

| Pin Name  | Pin#            | I/O | Description             |

|-----------|-----------------|-----|-------------------------|

| COM[310]  | 15~46           | О   | LCD COMMON Driver Pads. |

| SEG[63:0] | 1~14<br>139~188 | О   | LCD SEGMENT Driver Pads |

| LVL1      | 47              | P   | LCD Bias Voltage 1.     |

| LVL2      | 48              | P   | LCD Bias Voltage 2      |

| Pin Name                                | Pin#      | I/O     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------|-----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LVL3                                    | 49        |         | LCD Bias Voltage 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| LVL4                                    | 50        |         | LCD Bias Voltage 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| LVL5                                    | 51        |         | LCD Bias Voltage 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| LCAP4A                                  | 52        |         | Charge Pump Capacitor Pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LCAP2B                                  | 53        |         | Charge Pump Capacitor Pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LCAP2A                                  | 54        |         | Charge Pump Capacitor Pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LCAP1A                                  | 55        |         | Charge Pump Capacitor Pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LCAP1B                                  | 56        |         | Charge Pump Capacitor Pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LCAP3A                                  | 57        | О       | Charge Pump Capacitor Pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LVREG                                   | 58        | О       | Voltage Regulator Output. VDD is regulated to generate LVREG, which is in turns pumped to LVP. Adjust resistor between LGS1 and LVREG to set LVREG voltage.                                                                                                                                                                                                                                                                                                                                    |

| LGS1                                    | 59        |         | Regulator Voltage Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| LVAG                                    | 60        |         | Reference Voltage Output. Fixed 0.9 Volt DC reference voltage                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VDD LCD(VDDA)                           | 61        |         | Power supply for LCD charge-pump.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| GND_LCD(VSSA)                           | 62        | P       | LCD power system ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| OAC                                     | 63        | О       | LCD frame signal for interfacing with LCD segment extender KD80.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| OCCK                                    | 64        | О       | LCD data load pin for interfacing with LCD segment extender KD80.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| GND                                     | 65        | P       | Power ground Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| OPO                                     | 66        | О       | Output of OP Amp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| OPIP                                    | 67        | I       | Non-inverting input of OP Amp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| OPIN                                    | 68        | I       | Inverting input of OP Amp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DAO                                     | 69        | О       | Alternate output of DAC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VO                                      | 70        | О       | DAC Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RSTP_N                                  | 71        | T       | System Reset input pin. Level trigger, active low on this pin will put the chip in reset state.                                                                                                                                                                                                                                                                                                                                                                                                |

| FXO,<br>FXI                             | 72,<br>73 | O,<br>B | External fast clock pin. Two types of oscillator can be selected by MO_FXTAL ('0' for RC type and '1' for crystal type). For RC type oscillator, one resistor needs to be connected between FXI and GND. For crystal oscillator, one crystal needs to be placed between FXI and FXO. Please refer to application circuit for details.                                                                                                                                                          |

| TSTP_P                                  | 74        | T       | Test input pin. Please bond this pad and reserve a test point on PCB for debugging. But for improving ESD, please connect this point with zero Ohm resistor to GND.                                                                                                                                                                                                                                                                                                                            |

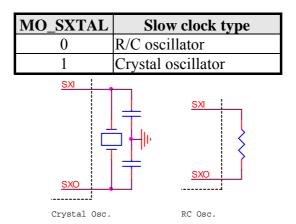

| SXO,<br>SXI                             | 75,<br>76 | O,<br>I | External slow clock pins. Slow clock is clock source for LCD display, TIMER1, Time-Base and other internal blocks. Both crystal and RC oscillator are provided. The slow clock type can be selected by mask option MO_SXTAL. Choose '0' for RC type and '1' for crystal oscillator.                                                                                                                                                                                                            |

| VX                                      | 77        | I       | Input pin for x32 PLL circuit. Connect to external resistor and capacitors as shown in application circuit.                                                                                                                                                                                                                                                                                                                                                                                    |

| VDD                                     | 78        | P       | Positive power Input. A $0.1~\mu F$ decoupling capacitors should be placed as close to IC VDD and GND pads as possible for best decoupling effect.                                                                                                                                                                                                                                                                                                                                             |

| PRT10[70]                               | 79~86     | В       | 8-bit bi-directional I/O port 10. The output type of I/O pad can also be selected by mask option MO_10PP[70] ('1' for push-pull and '0' for open-drain). As the output structure of I/O pad does not contain tri-state buffer. When using the I/O pad as input pad, "1" must be outputted before reading.                                                                                                                                                                                      |

| PRTD[72]<br>PRTD[1]/SIN<br>PRTD[0]/SOUT | 87~94     | В       | 8-bit bi-directional I/O port D. The output type of I/O pad can also be selected by mask option MO_DPP[70] ('1' for push-pull and '0' for open-drain). As the output structure of I/O pad does not contain tri-state buffer. When using the I/O as input, '1' must be outputted before reading the pin. PRTD[72] can be used as wake-up pins. PRTD[76] can be as external interrupt sources. PRTD[1] shares pad with UART Receiver SIN pin. PRTD[0] shares pad with UART transmitter SOUT pin. |

| PRTC[7:0]                               | 95~102    | В       | 8-bit bi-directional I/O port C. The output type of I/O pad can also be selected by mask option MO_CPP[70] ('1' for push-pull and '0' for open-drain). As the output structure of I/O pad does not contain tri-state buffer. When using the I/O as input, '1' must be outputted before reading the pin.                                                                                                                                                                                        |

| VDD_RAM                                 | 103       |         | Dedicated power input for RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| IRO                                     | 104       | О       | The Infrared output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PWM                                     | 105       | Ο       | The PWM output can drive speaker or buzzer directly. Using VDD & PWM to drive                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Pin Name | Pin#    | I/O | Description                      |

|----------|---------|-----|----------------------------------|

|          |         |     | output device.                   |

| GND_PWM  | 106     | P   | Dedicated Ground for PWM output. |

| NC       | 107~138 |     |                                  |

I: Input, O: Output, B: Bidirectional, P: Power.

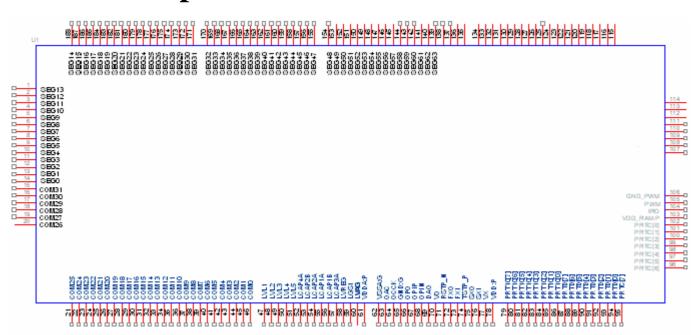

# 5. Pad Location

| PIN     | PIN     | X            | Y            |  |

|---------|---------|--------------|--------------|--|

| Numbe r | Name    | Coordinate   | Coordinate   |  |

|         |         |              |              |  |

|         |         |              |              |  |

| 1       | SEG[13] | X = -4123.60 | Y= 934.55    |  |

| 2       | SEG[12] | X = -4123.60 | Y= 834.55    |  |

| 3       | SEG[11] | X = -4123.60 | Y= 734.55    |  |

| 4       | SEG[10] | X = -4123.60 | Y = 634.55   |  |

| 5       | SEG[9]  | X = -4123.60 | Y = 534.55   |  |

| 6       | SEG[8]  | X = -4123.60 | Y = 434.55   |  |

| 7       | SEG[7]  | X = -4123.60 | Y = 334.55   |  |

| 8       | SEG[6]  | X = -4123.60 | Y = 234.55   |  |

| 9       | SEG[5]  | X = -4123.60 | Y= 134.55    |  |

| 10      | SEG[4]  | X = -4123.60 | Y = 34.55    |  |

| 11      | SEG[3]  | X = -4123.60 | Y = -65.45   |  |

| 12      | SEG[2]  | X = -4123.60 | Y = -165.45  |  |

| 13      | SEG[1]  | X = -4123.60 | Y = -265.45  |  |

| 14      | SEG[0]  | X = -4123.60 | Y = -365.45  |  |

| 15      | COM[31] | X = -4123.60 | Y = -465.45  |  |

| 16      | COM[30] | X = -4123.60 | Y = -565.45  |  |

| 17      | COM[29] | X = -4123.60 | Y = -665.45  |  |

| 18      | COM[28] | X = -4123.60 | Y= -765.45   |  |

| 19      | COM[27] | X = -4123.60 | Y = -865.45  |  |

| 20      | COM[26] | X = -4123.60 | Y= -965.45   |  |

| 21      | COM[25] | X = -3930.50 | Y = -1354.55 |  |

| 22      | COM[24] | X = -3830.50 | Y = -1354.55 |  |

| 23      | COM[23] | X = -3730.50 | Y = -1354.55 |  |

| 24      | COM[22] | X = -3630.50 | Y = -1354.55 |  |

| 25      | COM[21] | X = -3530.50 | Y = -1354.55 |  |

| 26      | COM[20] | X = -3430.50 | Y = -1354.55 |  |

| 27      | COM[19] | X = -3330.50 | Y = -1354.55 |  |

| 28      | COM[18] | X = -3230.50 | Y = -1354.55 |  |

|         |         |              |              |  |

| 29 | COM[17] | X = -3130.50 | Y = -1354.55 |

|----|---------|--------------|--------------|

| 30 | COM[16] | X = -3030.50 | Y = -1354.55 |

| 31 | COM[15] | X = -2930.50 | Y = -1354.55 |

| 32 | COM[14] | X = -2830.50 | Y = -1354.55 |

| 33 | COM[13] | X = -2730.50 | Y = -1354.55 |

| 34 | COM[12] | X = -2630.50 | Y = -1354.55 |

| 35 | COM[11] | X = -2530.50 | Y = -1354.55 |

| 36 | COM[10] | X = -2430.50 | Y = -1354.55 |

| 37 | COM[9]  | X = -2330.50 | Y = -1354.55 |

| 38 | COM[8]  | X = -2230.50 | Y = -1354.55 |

| 39 | COM[7]  | X = -2130.50 | Y = -1354.55 |

| 40 | COM[6]  | X = -2030.50 | Y = -1354.55 |

| 41 | COM[5]  | X = -1930.50 | Y = -1354.55 |

| 42 | COM[4]  | X = -1830.50 | Y = -1354.55 |

| 43 | COM[3]  | X = -1730.50 | Y = -1354.55 |

| 44 | COM[2]  | X = -1630.50 | Y = -1354.55 |

| 45 | COM[1]  | X = -1530.50 | Y = -1354.55 |

| 46 | COM[0]  | X = -1430.50 | Y = -1354.55 |

| 47 | LVL1    | X = -1230.50 | Y = -1354.55 |

| 48 | LVL2    | X = -1130.50 | Y = -1354.55 |

| 49 | LVL3    | X = -1030.50 | Y = -1354.55 |

| 50 | LVL4    | X = -930.50  | Y = -1354.55 |

| 51 | LVL5    | X = -830.50  | Y = -1354.55 |

| 52 | LCAP4A  | X = -730.50  | Y = -1354.55 |

| 53 | LCAP2B  | X = -630.50  | Y = -1354.55 |

| 54 | LCAP2A  | X = -530.50  | Y = -1354.55 |

| 55 | LCAP1A  | X = -430.50  | Y = -1354.55 |

| 56 | LCAP1B  | X = -330.50  | Y = -1354.55 |

| 57 | LCAP3A  | X = -230.50  | Y = -1354.55 |

| 58 | LVREG   | X = -130.50  | Y = -1354.55 |

| 59 | LGS1    | X = -30.50   | Y = -1354.55 |

| 60 | LVAG    | X = 69.50    | Y = -1354.55 |

| 61 | VDDA    | X= 169.50    | Y = -1354.55 |

| 62 | VSSA    | X = 369.50   | Y = -1354.55 |

| 63 | OAC     | X = 469.50   | Y = -1354.55 |

| 64 | OCCK    | X= 569.50    | Y = -1354.55 |

| 65 | GND     | X= 669.50    | Y = -1354.55 |

| 66 | OPO     | X= 769.50    | Y = -1354.55 |

| 67 | OPIP    | X = 869.50   | Y = -1354.55 |

| 68  | OPIN     | X= | 969.50  | Y = -1354.55 |

|-----|----------|----|---------|--------------|

| 69  | DAO      | X= | 1069.50 | Y = -1354.55 |

| 70  | VO       | X= | 1169.50 | Y = -1354.55 |

| 71  | RSTP_N   | X= | 1269.50 | Y = -1354.55 |

| 72  | FXO      | X= | 1369.50 | Y = -1354.55 |

| 73  | FXI      | X= | 1469.50 | Y = -1354.55 |

| 74  | TSTP_P   | X= | 1569.50 | Y = -1354.55 |

| 75  | SXO      | X= | 1669.50 | Y = -1354.55 |

| 76  | SXI      | X= | 1769.50 | Y = -1354.55 |

| 77  | VX       | X= | 1869.50 | Y = -1354.55 |

| 78  | VDD      | X= | 1969.50 | Y = -1354.55 |

| 79  | PRT10[7] | X= | 2169.50 | Y = -1354.55 |

| 80  | PRT10[6] | X= | 2269.50 | Y = -1354.55 |

| 81  | PRT10[5] | X= | 2369.50 | Y = -1354.55 |

| 82  | PRT10[4] | X= | 2469.50 | Y = -1354.55 |

| 83  | PRT10[3] | X= | 2569.50 | Y = -1354.55 |

| 84  | PRT10[2] | X= | 2669.50 | Y = -1354.55 |

| 85  | PRT10[1] | X= | 2769.50 | Y = -1354.55 |

| 86  | PRT10[0] | X= | 2869.50 | Y = -1354.55 |

| 87  | PRTD[7]  | X= | 2969.50 | Y = -1354.55 |

| 88  | PRTD[6]  | X= | 3069.50 | Y = -1354.55 |

| 89  | PRTD[5]  | X= | 3169.50 | Y = -1354.55 |

| 90  | PRTD[4]  | X= | 3269.50 | Y = -1354.55 |

| 91  | PRTD[3]  | X= | 3369.50 | Y = -1354.55 |

| 92  | PRTD[2]  | X= | 3469.50 | Y = -1354.55 |

| 93  | PRTD[1]  | X= | 3569.50 | Y = -1354.55 |

| 94  | PRTD[0]  | X= | 3669.50 | Y = -1354.55 |

| 95  | PRTC[7]  | X= | 3769.50 | Y = -1354.55 |

| 96  | PRTC[6]  | X= | 4122.00 | Y = -1126.45 |

| 97  | PRTC[5]  | X= | 4122.00 | Y = -1026.45 |

| 98  | PRTC[4]  | X= | 4122.00 | Y = -926.45  |

| 99  | PRTC[3]  | X= | 4122.00 | Y = -826.45  |

| 100 | PRTC[2]  | X= | 4122.00 | Y = -726.45  |

| 101 | PRTC[1]  | X= | 4122.00 | Y = -626.45  |

| 102 | PRTC[0]  | X= | 4122.00 | Y = -526.45  |

| 103 | VDD_RAM  | X= | 4122.00 | Y = -426.45  |

| 104 | IRO      | X= | 4122.00 | Y = -326.45  |

| 105 | PWM      | X= | 4122.00 | Y = -226.45  |

| 106 | GND_PWM  | X= | 4122.00 | Y = -126.45  |

| 107 | NC      | X= | 4122.00 | Y= | 473.55  |

|-----|---------|----|---------|----|---------|

| 108 | NC      | X= | 4122.00 | Y= | 573.55  |

| 109 | NC      | X= | 4122.00 | Y= | 673.55  |

| 110 | NC      | X= | 4122.00 | Y= | 773.55  |

| 111 | NC      | X= | 4122.00 | Y= | 873.55  |

| 112 | NC      | X= | 4122.00 | Y= | 973.55  |

| 113 | NC      | X= | 4122.00 | Y= | 1073.55 |

| 114 | NC      | X= | 4122.00 | Y= | 1173.55 |

| 115 | NC      | X= | 3668.40 | Y= | 1354.05 |

| 116 | NC      | X= | 3568.40 | Y= | 1354.05 |

| 117 | NC      | X= | 3468.40 | Y= | 1354.05 |

| 118 | NC      | X= | 3368.40 | Y= | 1354.05 |

| 119 | NC      | X= | 3268.40 | Y= | 1354.05 |

| 120 | NC      | X= | 3168.40 | Y= | 1354.05 |

| 121 | NC      | X= | 3068.40 | Y= | 1354.05 |

| 122 | NC      | X= | 2968.40 | Y= | 1354.05 |

| 123 | NC      | X= | 2868.40 | Y= | 1354.05 |

| 124 | NC      | X= | 2768.40 | Y= | 1354.05 |

| 125 | NC      | X= | 2668.40 | Y= | 1354.05 |

| 126 | NC      | X= | 2568.40 | Y= | 1354.05 |

| 127 | NC      | X= | 2468.40 | Y= | 1354.05 |

| 128 | NC      | X= | 2368.40 | Y= | 1354.05 |

| 129 | NC      | X= | 2268.40 | Y= | 1354.05 |

| 130 | NC      | X= | 2168.40 | Y= | 1354.05 |

| 131 | NC      | X= | 2068.40 | Y= | 1354.05 |

| 132 | NC      | X= | 1968.40 | Y= | 1354.05 |

| 133 | NC      | X= | 1868.40 | Y= | 1354.05 |

| 134 | NC      | X= | 1768.40 | Y= | 1354.05 |

| 135 | NC      | X= | 1568.40 | Y= | 1354.05 |

| 136 | NC      | X= | 1468.40 | Y= | 1354.05 |

| 137 | NC      | X= | 1368.40 | Y= | 1354.05 |

| 138 | NC      | X= | 1268.40 | Y= | 1354.05 |

| 139 | SEG[63] | X= | 1168.40 | Y= | 1354.05 |

| 140 | SEG[62] | X= | 1068.40 | Y= | 1354.05 |

| 141 | SEG[61] | X= | 968.40  | Y= | 1354.05 |

| 142 | SEG[60] | X= | 868.40  | Y= | 1354.05 |

| 143 | SEG[59] | X= | 768.40  | Y= | 1354.05 |

| 144 | SEG[58] | X= | 668.40  | Y= | 1354.05 |

| 145 | SEG[57] | X= | 568.40  | Y= | 1354.05 |

| 146 | SEG[56] | X= 468.40    | Y= | 1354.05 |

|-----|---------|--------------|----|---------|

| 147 | SEG[55] | X = 368.40   | Y= | 1354.05 |

| 148 | SEG[54] | X = 268.40   | Y= | 1354.05 |

| 149 | SEG[53] | X = 168.40   | Y= | 1354.05 |

| 150 | SEG[52] | X = 68.40    | Y= | 1354.05 |

| 151 | SEG[51] | X = -31.60   | Y= | 1354.05 |

| 152 | SEG[50] | X = -131.60  | Y= | 1354.05 |

| 153 | SEG[49] | X = -231.60  | Y= | 1354.05 |

| 154 | SEG[48] | X = -331.60  | Y= | 1354.05 |

| 155 | SEG[47] | X = -531.60  | Y= | 1354.05 |

| 156 | SEG[46] | X = -631.60  | Y= | 1354.05 |

| 157 | SEG[45] | X = -731.60  | Y= | 1354.05 |

| 158 | SEG[44] | X = -831.60  | Y= | 1354.05 |

| 159 | SEG[43] | X= -931.60   | Y= | 1354.05 |

| 160 | SEG[42] | X = -1031.60 | Y= | 1354.05 |

| 161 | SEG[41] | X = -1131.60 | Y= | 1354.05 |

| 162 | SEG[40] | X = -1231.60 | Y= | 1354.05 |

| 163 | SEG[39] | X = -1331.60 | Y= | 1354.05 |

| 164 | SEG[38] | X = -1431.60 | Y= | 1354.05 |

| 165 | SEG[37] | X = -1531.60 | Y= | 1354.05 |

| 166 | SEG[36] | X = -1631.60 | Y= | 1354.05 |

| 167 | SEG[35] | X = -1731.60 | Y= | 1354.05 |

| 168 | SEG[34] | X = -1831.60 | Y= | 1354.05 |

| 169 | SEG[33] | X= -1931.60  | Y= | 1354.05 |

| 170 | SEG[32] | X = -2031.60 | Y= | 1354.05 |

| 171 | SEG[31] | X = -2231.60 | Y= | 1354.05 |

| 172 | SEG[30] | X = -2331.60 | Y= | 1354.05 |

| 173 | SEG[29] | X = -2431.60 | Y= | 1354.05 |

| 174 | SEG[28] | X = -2531.60 | Y= | 1354.05 |

| 175 | SEG[27] | X = -2631.60 | Y= | 1354.05 |

| 176 | SEG[26] | X = -2731.60 | Y= | 1354.05 |

| 177 | SEG[25] | X = -2831.60 | Y= | 1354.05 |

| 178 | SEG[24] | X = -2931.60 | Y= | 1354.05 |

| 179 | SEG[23] | X = -3031.60 | Y= | 1354.05 |

| 180 | SEG[22] | X = -3131.60 | Y= | 1354.05 |

| 181 | SEG[21] | X = -3231.60 | Y= | 1354.05 |

| 182 | SEG[20] | X = -3331.60 | Y= | 1354.05 |

| 183 | SEG[19] | X = -3431.60 | Y= | 1354.05 |

| 184 | SEG[18] | X = -3531.60 | Y= | 1354.05 |

| 185 | SEG[17] | X = -3631.60 | Y= | 1354.05 |

|-----|---------|--------------|----|---------|

| 186 | SEG[16] | X = -3731.60 | Y= | 1354.05 |

| 187 | SEG[15] | X = -3831.60 | Y= | 1354.05 |

| 188 | SEG[14] | X = -3931.60 | Y= | 1354.05 |

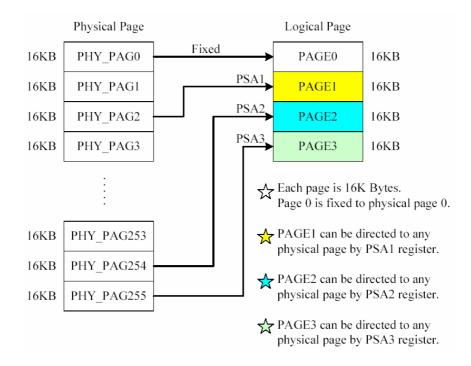

# 6. ROM Map Configurations

The chip has built-in 512K bytes internal ROM. In addition, address and data buses are provided to access External ROM. The MCU can access up to 4M bytes program ROM and up to 16M bytes data space through external buses. The SEG[47..40], SEG[39..16] pads are used as either data and address buses for external ROM or LCD segment driver pads depending on the mask option MO\_EXMEM. When the external ROM mask option is selected, the MCU will retrieve the instructions and data from external ROM through the address and data buses.

The bit  $14 \sim 15$  bit of 16-bit logical program address can be mapped to any one (16K bytes per page) of 256 pages through mapping registers PSA1, PSA2, PSA3. As logical page 0 can not be moved and is always physical page 0, the PSA1  $\sim$  PSA3 contain the physical page addresses of logical pages  $1 \sim 3$ .

|        | Logical Address |     |     |     |     |    |    |    |    |    |    |    |    |    |    |

|--------|-----------------|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| A15    | A14             | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 |

| Page . | Addr.           | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 |

| A[1514] | Logical Page | Physical Page Address | Physical Address |

|---------|--------------|-----------------------|------------------|

| 00      | 0            | 0                     | 00A[130]         |

| 01      | 1            | PSA1                  | PSA1+A[130]      |

| 10      | 2            | PSA2                  | PSA2+A[130]      |

| 11      | 3            | PSA3                  | PSA3+A[130]      |

| Register | Address | Type |     | Bits Definition |     |     |     |     |     |     |      |

|----------|---------|------|-----|-----------------|-----|-----|-----|-----|-----|-----|------|

| PSA1     | 0x2C    | R/W  | A21 | A20             | A19 | A18 | A17 | A16 | A15 | A14 | 0x01 |

| PSA2     | 0x2D    | R/W  | A21 | A20             | A19 | A18 | A17 | A16 | A15 | A14 | 0x02 |

| PSA3     | 0x2E    | R/W  | A21 | A20             | A19 | A18 | A17 | A16 | A15 | A14 | 0x03 |

| Address | Option2              |

|---------|----------------------|

| 000000  | Int. PROM<br>(256KB) |

| 040000  | Unused               |

| 400000  | Int. DROM<br>(256KB) |

| 440000  |                      |

| FFFFFF  |                      |

# 7. LCD Display RAM Map

The gray-scale LCD driver can be configured to be a 16 gray-scale, 4 gray-scales or black and white display by mask option MO\_GRAY\_MODE.

| MO_GRAY_MODE[10] | Gray levels |

|------------------|-------------|

| 00               | 16          |

| 01 | 4       |

|----|---------|

| 10 | 2 (B/W) |

| 11 | 2 (B/W) |

For 4 gray-scale display, 2-bit of RAM is required for each pixel and 4 bit for 16 gray-scale display, 1-bit for black and white display. For different LCD configuration, the LCD display RAM is arranged differently. The following figure shows one byte of RAM in different LCD configurations:

| 0F | 0E | 0D | 0C | 0B | 0A | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| XX |

|                | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Black/White    | SEG7  | SEG6  | SEG5  | SEG4  | SEG3  | SEG2  | SEG1  | SEG0  |

| 4 Gray scales  | SEG3  |       | SEG2  |       | SEG1  |       | SEG0  |       |

| 16 Gray scales |       | SE    | G1    |       | SEG0  |       |       |       |

The 16 Gray Scale register GRAY0  $\sim$  GRAYF is the mapping register between the levels selected in RAM and the real gray scale. In other words, if the content of GRAY0 is 0x03, when value of a certain pixel is 0, the displayed effect will correspond to actual gray level 3. The 16 gray scale display use all 16 registers GRAY0  $\sim$  GRAYF to select among 32 available gray levels to correspond to level 0  $\sim$  15, while 4 gray scale display utilizes registers GRAY0  $\sim$  GRAY3 to select among 32 gray levels to correspond to level 0  $\sim$  3. Thus user can pick the gray levels which give the best and most linear effect.

16 Gray Scale registers share a common register address GRAY16. When writing is made to the register, it will step down to next register in order. The writing sequence can be reset by clearing bit 5 of LCDC register.

| <b>GRAY16</b> |       |      | Field |      |      |       |  |

|---------------|-------|------|-------|------|------|-------|--|

| Seq.          | Bit4  | Bit3 | Bit2  | Bit1 | Bit0 | Reset |  |

| 1             |       |      | GRAY0 |      |      | 0x00  |  |

| 2             |       |      | GRAY1 |      |      | 0x02  |  |

| 3             |       |      | GRAY2 |      |      | 0x04  |  |

| 4             |       |      | GRAY3 |      |      | 0x06  |  |

| 5             |       |      | GRAY4 |      |      | 0x08  |  |

| 6             |       |      | GRAY5 |      |      | 0x0A  |  |

| 7             | GRAY6 |      |       |      |      |       |  |

| 8             |       |      | GRAY7 |      |      | 0x0E  |  |

| 9             |       |      | GRAY8 |      |      | 0x10  |  |

| 10            |       |      | GRAY9 |      |      | 0x12  |  |

| 11            |       |      | GRAYA |      |      | 0x14  |  |

| 12            |       |      | GRAYB |      |      | 0x16  |  |

| 13            |       |      | GRAYC |      |      | 0x18  |  |

| 14            | GRAYD |      |       |      |      |       |  |

| 15            | GRAYE |      |       |      |      |       |  |

| 16            |       |      | GRAYF |      |      | 0x1E  |  |

# 7.1. 16 Gray Scale LCD Display RAM Map

|      |      |                | J |        |

|------|------|----------------|---|--------|

|      | Cnf  | 32 X 64        |   |        |

| Page | Loc. | F              | 0 |        |

|      | 00   | S31 ~ S00      |   |        |

|      | 10   | S63 ~ S32      |   |        |

|      |      | 303 ~ 332      |   | COM0   |

|      | 20   | *              |   |        |

|      | 30   |                |   |        |

|      | 40   | S31 ~ S00      |   |        |

|      | 50   | S63 ~ S32      |   | COM1   |

|      | 60   | *              |   |        |

| 1    | 70   | *              |   |        |

|      | 80   | S31 ~ S00      |   |        |

|      | 90   | S63 ~ S32      |   | COM2   |

|      | A0   | *              |   | CONIZ  |

|      | В0   | *              |   |        |

|      | C0   | S31 ~ S00      |   |        |

|      | D0   | S63 ~ S32      |   | G01.62 |

|      | E0   |                |   | COM3   |

|      | F0   | *              |   |        |

|      | 00   | S31 ~ S00      |   |        |

|      | 10   | S63 ~ S32      |   |        |

|      |      | 303 ≈ 332<br>* |   | COM4   |

|      | 20   | *              |   |        |

|      | 30   |                |   |        |

|      | 40   | S31 ~ S00      |   |        |

|      | 50   | S63 ~ S32      |   | COM5   |

|      | 60   | *              |   |        |

| 2    | 70   | *              |   |        |

| _    | 80   | S31 ~ S00      |   |        |

|      | 90   | S63 ~ S32      |   | COM6   |

|      | A0   | *              |   | COMO   |

|      | В0   | *              |   |        |

|      | C0   | S31 ~ S00      |   |        |

|      | D0   | S63 ~ S32      |   | G03.45 |

|      | E0   | *              |   | COM7   |

|      | F0   | *              |   |        |

|      | 00   | S31 ~ S00      |   |        |

|      | 10   | S63 ~ S32      |   |        |

|      | 20   | 303 ≈ 332<br>* |   | COM8   |

|      |      | *              |   |        |

|      | 30   |                |   |        |

|      | 40   | S31 ~ S00      |   |        |

|      | 50   | S63 ~ S32      |   | COM9   |

|      | 60   | *              |   |        |

| 3    | 70   | *              |   |        |

|      | 80   | S31 ~ S00      |   |        |

|      | 90   | S63 ~ S32      |   | COM10  |

|      | A0   | *              |   | COMITO |

|      | В0   | *              |   |        |

|      | C0   | S31 ~ S00      |   |        |

|      | D0   | S63 ~ S32      |   | 001411 |

|      | E0   | *              |   | COM11  |

|      | F0   | *              |   |        |

| 4    | 00   | S31 ~ S00      |   |        |

| 7    | 10   | 331 - 300      |   |        |

|      |      | 905 974        |   | COM12  |

|      | 20   | S95 ~ S64      |   |        |

|      | 30   | *              |   |        |

|      | Cnf  | 32 X 64   |           |          |  |  |  |

|------|------|-----------|-----------|----------|--|--|--|

| Page | Loc. |           | 0         |          |  |  |  |

|      | 40   | S31 ~ S00 | •         |          |  |  |  |

|      | 50   | S63 ~ S32 |           |          |  |  |  |

|      | 60   | *         |           | COM13    |  |  |  |

|      | 70   | *         |           |          |  |  |  |

|      | 80   | S31 ~ S00 |           |          |  |  |  |

|      | 90   | S63 ~ S32 |           |          |  |  |  |

|      | A0   | *         |           | COM14    |  |  |  |

|      | B0   | *         |           |          |  |  |  |

|      | CO   | S31 ~ S00 |           |          |  |  |  |

|      | D0   | S63 ~ S32 |           | G03.54.5 |  |  |  |

|      | E0   | *         |           | COM15    |  |  |  |

|      | F0   | *         |           |          |  |  |  |

|      | 00   | S31 ~ S00 |           |          |  |  |  |

|      | 10   | S63 ~ S32 |           | 00111    |  |  |  |

|      | 20   | *         |           | COM16    |  |  |  |

|      | 30   | *         | $\exists$ |          |  |  |  |

|      | 40   | S31 ~ S00 |           |          |  |  |  |

|      | 50   | S63 ~ S32 | $\neg$    | 001415   |  |  |  |

|      | 60   | *         |           | COM17    |  |  |  |

| _    | 70   | *         | $\neg$    |          |  |  |  |

| 5    | 80   | S31 ~ S00 |           |          |  |  |  |

|      | 90   | S63 ~ S32 | G01.510   |          |  |  |  |

|      | A0   | *         |           | COM18    |  |  |  |

|      | В0   | *         |           |          |  |  |  |

|      | C0   | S31 ~ S00 |           |          |  |  |  |

|      | D0   | S63 ~ S32 |           | COMMO    |  |  |  |

|      | E0   | *         |           | COM19    |  |  |  |

|      | F0   | *         |           |          |  |  |  |

|      | 00   | S31 ~ S00 |           |          |  |  |  |

|      | 10   | S63 ~ S32 |           | COM20    |  |  |  |

|      | 20   | *         |           | COM20    |  |  |  |

|      | 30   | *         |           |          |  |  |  |

|      | 40   | S31 ~ S00 |           |          |  |  |  |

|      | 50   | S63 ~ S32 |           | COM21    |  |  |  |

|      | 60   | *         |           | COMZI    |  |  |  |

| 6    | 70   | *         |           |          |  |  |  |

| ٥    | 80   | S31 ~ S00 |           |          |  |  |  |

|      | 90   | S63 ~ S32 |           | COM22    |  |  |  |

|      | A0   | *         |           | COMIZZ   |  |  |  |

|      | В0   | *         |           |          |  |  |  |

|      | C0   | S31 ~ S00 |           |          |  |  |  |

|      | D0   | S63 ~ S32 |           | COM23    |  |  |  |

|      | E0   | *         |           | CO1V123  |  |  |  |

|      | F0   | *         |           |          |  |  |  |

| 7    | 00   | S31 ~ S00 |           |          |  |  |  |

|      | 10   | S63 ~ S32 |           | COM24    |  |  |  |

|      | 20   | S95 ~ S64 |           | C 011127 |  |  |  |

|      | 30   | *         |           |          |  |  |  |

|      | 40   | S31 ~ S00 |           |          |  |  |  |

|      | 50   | S63 ~ S32 |           | COM25    |  |  |  |

|      | 60   | *         |           | 201.120  |  |  |  |

|      | 70   | *         |           |          |  |  |  |

|      | 80   | S31 ~ S00 |           | A ·      |  |  |  |

|      | 90   | S63 ~ S32 |           | COM26    |  |  |  |

|      | A0   | *         |           |          |  |  |  |

|      | Cnf  | 32 X 64        |        |  |  |  |

|------|------|----------------|--------|--|--|--|

| Page | Loc. | F 0            |        |  |  |  |

|      | В0   | *              |        |  |  |  |

|      | C0   | S31 ~ S00      |        |  |  |  |

|      | D0   | S63 ~ S32      | COM27  |  |  |  |

|      | E0   | *              | CONIZ  |  |  |  |

|      | F0   | *              |        |  |  |  |

|      | 00   | S31 ~ S00      |        |  |  |  |

|      | 10   | S63 ~ S32      | COM28  |  |  |  |

|      | 20   | *              | COMZ8  |  |  |  |

|      | 30   | *              |        |  |  |  |

|      | 40   | $S31 \sim S00$ |        |  |  |  |

|      | 50   | S63 ~ S32      | COM29  |  |  |  |

|      | 60   | *              | COMIZ  |  |  |  |

| 8    | 70   | *              |        |  |  |  |

| 0    | 80   | S31 ~ S00      |        |  |  |  |

|      | 90   | S63 ~ S32      | COM30  |  |  |  |

|      | A0   | *              | COMSO  |  |  |  |

|      | В0   | *              |        |  |  |  |

|      | C0   | S31 ~ S00      |        |  |  |  |

|      | D0   | S63 ~ S32      | COM31  |  |  |  |

|      | E0   | *              | COMIST |  |  |  |

|      | F0   | *              |        |  |  |  |

# 7.2. 4 Gray Scale LCD Display RAM Map

|      |      |       |           | - 1 |        |

|------|------|-------|-----------|-----|--------|

|      | Cnf  | 32x   | <u>64</u> |     |        |

| Page | Loc. | F     |           | 0   |        |

|      | 00   | S63 ~ | ~ S00     |     | COM0   |

|      | 10   | *     | *         |     | COMO   |

|      | 20   | S63 ~ | ~ S00     |     | COM1   |

|      | 30   | *     | *         |     | COMI   |

|      | 40   | S63 ~ | ~ S00     |     | COM2   |

|      | 50   | *     | *         |     | COMZ   |

|      | 60   | S63 ~ | ~ S00     |     | COM3   |

| 1    | 70   | *     | *         |     | COMS   |

| 1    | 80   | S63 ~ | ~ S00     |     | COM4   |

|      | 90   | *     | *         |     | COM4   |

|      | A0   | S63 ~ | ~ S00     |     | COM5   |

|      | В0   | *     | *         |     | COMS   |

|      | C0   | S63 ~ | ~ S00     |     | COM6   |

|      | D0   | *     | *         |     | COMO   |

|      | E0   | S63 ~ | ~ S00     |     | COM7   |

|      | F0   | *     | *         |     | COM7   |

| 2    | 00   | S63 ~ | ~ S00     |     | COM8   |

|      | 10   | *     | *         |     | COMO   |

|      | 20   | S63 ~ | ~ S00     |     | COM9   |

|      | 30   | *     | *         |     | COM    |

|      | 40   | S63 ~ | ~ S00     |     | COM10  |

|      | 50   | *     | *         |     | COMITO |

|      | 60   | S63 ~ | - S00     |     | COM11  |

|      | 70   | *     | *         |     | COMIT  |

|      | 80   | S63 ~ | - S00     |     | COM12  |

|      | 90   | *     | *         |     | COMIZ  |

|      | A0   | S63 ~ | - S00     |     | COM13  |

|      | В0   | *     | *         |     | COMITS |

|      |      |       |           |     |        |

|       | Cnf  | 32x64     |         |

|-------|------|-----------|---------|

| Page  | Loc. | F 0       |         |

| 1 480 | C0   | S63 ~ S00 |         |

|       | D0   | * *       | COM14   |

|       | E0   | S63 ~ S00 |         |

|       | F0   | * *       | COM15   |

|       | 00   | S63 ~ S00 | 001416  |

|       | 10   | * *       | COM16   |

|       | 20   | S63 ~ S00 | COM17   |

|       | 30   | * *       | COM17   |

|       | 40   | S63 ~ S00 | COM10   |

|       | 50   | * *       | COM18   |

|       | 60   | S63 ~ S00 | COM10   |

| 3     | 70   | * *       | COM19   |

| 3     | 80   | S63 ~ S00 | COM20   |

|       | 90   | * *       | COMIZO  |

|       | A0   | S63 ~ S00 | COM21   |

|       | В0   | * *       | COMZI   |

|       | C0   | S63 ~ S00 | COM22   |

|       | D0   | * *       | COMIZZ  |

|       | E0   | S63 ~ S00 | COM23   |

|       | F0   | * *       | COM23   |

|       | 00   | S63 ~ S00 | COM24   |

|       | 10   | * *       | COMZ4   |

|       | 20   | S63 ~ S00 | COM25   |

|       | 30   | * *       | CONIZS  |

|       | 40   | S63 ~ S00 | COM26   |

|       | 50   | * *       | COMZO   |

|       | 60   | S63 ~ S00 | COM27   |

| 4     | 70   | * *       | COIVIZ  |

| 7     | 80   | S63 ~ S00 | COM28   |

|       | 90   | * *       | CO14120 |

|       | A0   | S63 ~ S00 | COM29   |

|       | В0   | * *       | 001112) |

|       | C0   | S63 ~ S00 | COM30   |

|       | D0   | * *       | 2011130 |

|       | E0   | S63 ~ S00 | COM31   |

|       | F0   | * *       | 001,131 |

# 7.3. Black and White LCD Display RAM Map

|      | Cnf  |   | 32x64     |       |

|------|------|---|-----------|-------|

| Page | Loc. | F | 0         |       |

| 1    | 00   | * | S63 ~ S00 | COM0  |

|      | 10   | * | S63 ~ S00 | COM1  |

|      | 20   | * | S63 ~ S00 | COM2  |

|      | 30   | * | S63 ~ S00 | COM3  |

|      | 40   | * | S63 ~ S00 | COM4  |

|      | 50   | * | S63 ~ S00 | COM5  |

|      | 60   | * | S63 ~ S00 | COM6  |

|      | 70   | * | S63 ~ S00 | COM7  |

|      | 80   | * | S63 ~ S00 | COM8  |

|      | 90   | * | S63 ~ S00 | COM9  |

|      | A0   | * | S63 ~ S00 | COM10 |

|      | В0   | * | S63 ~ S00 | COM11 |

|      | C0   | * | S63 ~ S00 | COM12 |

|      | Cnf  |   | 32x       | ĸ64      |   |       |

|------|------|---|-----------|----------|---|-------|

| Page | Loc. | F |           |          | 0 |       |

|      | D0   | * | S         | 63 ~ S00 |   | COM13 |

|      | E0   | * | S         | 63 ~ S00 |   | COM14 |

|      | F0   | * | S         | 63 ~ S00 |   | COM15 |

|      | 00   | * | S         | 63 ~ S00 |   | COM16 |

|      | 10   | * | S         | 63 ~ S00 |   | COM17 |

|      | 20   | * | S         | 63 ~ S00 |   | COM18 |

|      | 30   | * | S         | 63 ~ S00 |   | COM19 |

|      | 40   | * | S         | 63 ~ S00 |   | COM20 |

|      | 50   | * | S         | 63 ~ S00 |   | COM21 |

|      | 60   | * | S         | 63 ~ S00 |   | COM22 |

| 2    | 70   | * | S         | 63 ~ S00 |   | COM23 |

|      | 80   | * | S         | 63 ~ S00 |   | COM24 |

|      | 90   | * | S         | 63 ~ S00 |   | COM25 |

|      | A0   | * | S         | 63 ~ S00 |   | COM26 |

|      | В0   | * | S         | 63 ~ S00 |   | COM27 |

|      | C0   | * | S63 ~ S00 |          |   | COM28 |

|      | D0   | * | S         | 63 ~ S00 |   | COM29 |

|      | E0   | * | S63 ~ S00 |          |   | COM30 |

|      | F0   | * | S         | 63 ~ S00 |   | COM31 |

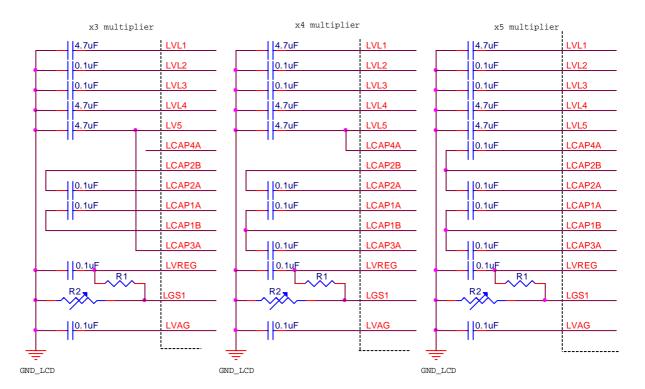

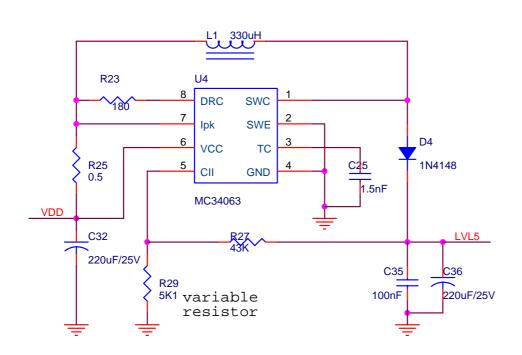

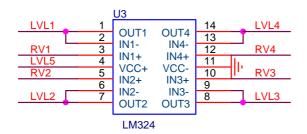

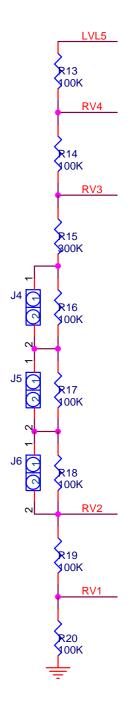

# **8. LCD Power Supply**

The built-in LCD power supply is equipped with input voltage regulator, voltage multiplier and bias voltage generating circuit with active buffer instead of passive resistor voltage dividing network. If the external LCD power is provided, the internal LCD power system shall be disabled. The following table shows the relationship of the LCD power system

| LCDE(LCDC BIT0) | MO_PSMODE[1:0] | Function                                         |

|-----------------|----------------|--------------------------------------------------|

|                 |                | Internal voltage multiplier and Bias voltage     |

| 1               | 00             | generating circuit are enable to supply the      |

|                 |                | LCD display power.                               |

|                 |                | Internal voltage multiplier is enabled, but the  |

| 1               | 01             | Bias voltage generating circuit is disabled,and  |

| 1               | V1             | the external power sources are applied           |

|                 |                | LV4~LV1.                                         |

|                 |                | Internal voltage multiplier is disabled, but the |

|                 |                | Bias voltage generating circuit is enabled.      |

| 1               | 10             | The single external power is applied to LV5,     |

|                 |                | and internal bias circuit will generate the      |

|                 |                | LV4~LV1 voltages.                                |

|                 |                | Internal voltage multiplier and Bias voltage     |

| 1               | 11             | generating circuit are disabled, and the         |

| 1               |                | external power sources are applied to            |

|                 |                | LV5~LV1.                                         |

| 0               | 00             | The lcd power system is disable,but the LV5~     |

| 0               | 00             | LV1 is applied to VDD.                           |

|                 |                | The lcd power system is disable,but the LV5      |

| 0               | 01             | is applied to VDD and LV4~LV1 is applied to      |

|                 |                | hight impedance.                                 |

|                 |                | The lcd power system is disable, LV5 is          |

| 0               | 10             | applied to hight impedance, and the LV4~LV1      |

|                 |                | Applied to LV5.                                  |

|                 | 11             | The lcd power system is disable, LV5~LV1 is      |

| 0               | 11             | applied to hight impedance.                      |

|                 |                |                                                  |

when the internal LCD power system is used by internal voltage multiplier. The input voltage is regulated to LVREG using the internally by resistor between LGS1 and LVREG generated LVAG as reference voltage. LVREG can be adjusted

**LVREG adjustment guideline**: First, the level of VDD must be 0.3 volt higher than LVREG even at the end of battery life for the regulator to function properly. For example, if the VDD is expected to drop to 2.2 volts when battery is low, then the level of LVREG can only be set at 1.9 volts max. Secondly, the higher the level of LVREG, the less multiples it requires pumping LV5 to same level. For example, to pump the 2.25 volts to 9 volts requires 4 times multiplier; to pump the 3 volts to 9 volts requires only 3 time multiplier which consumes less power. So it is advisable not to adjust the LVREG to an unnecessary low level.

**Voltage multiplication:** The LVREG is then multiplied by 3, 4, or 5 times, depending on external capacitors configurations as shown below, to generate LV5. Please note that LV5 must be lower than 8.5 volts to prevent chip from breaking down.

Different duties require different bias settings. There is some theoretical correspondence between the Duty and Bias Setting. However, it is better to use it as starting point and adjust it with real LCD panel connected to it to determine the final setting. The theoretic relationship between the duty and bias setting as following:

| <b>Duty Cycle</b> | <b>Normal Bias</b> | <b>Alternative Bias</b> |

|-------------------|--------------------|-------------------------|

| 32 duty           | 1/7                | 1/7.5                   |

| 48 duty           | 1/8                | 1/7.5, 1/8.5            |

| 64 duty           | 1/9                | 1/8.5, 1/9.5            |

| 80 duty           | 1/10               | 1/9.5, 1/10.5           |

The bias setting is made by mask option MO LBSR[2..0].

| MO_LBSR[20] | <b>Bias Setting</b> |

|-------------|---------------------|

| 000         | 1/7                 |

| 001         | 1/7.5               |

| 010         | 1/8                 |

| 011         | 1/8.5               |

| 100         | 1/9                 |

| 101         | 1/9.5               |

| 110         | 1/10                |

| 111         | 1/5                 |

# 9. LCDC Control register

LCD Control Register LCDC controls the functions of LCD driver.

| LCDC  | bit 7 | bit 6 | bit 5  | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|--------|-------|-------|-------|-------|-------|

| Field | -     | -     | CLR_GP |       | GRAY  |       | BLANK | LCDE  |

| Mode  | -     | -     | W      |       | W     |       | W     | W     |

| Reset | -     | -     | 1      |       | XXX   |       | 1     | 0     |

| Field  | Value                                                           | Function                                    |

|--------|-----------------------------------------------------------------|---------------------------------------------|

| CLR GP | Reset GRAY palette register pointer by write '0' to CLR_GP bit. |                                             |

| CLK_GF | 1                                                               | No effect on GRAY palette register pointer. |

|        | 000                                                             | LCD is darkest.                             |

| GRAY   |                                                                 | LCD display contrast adjustment.            |

|        | 111                                                             | LCD is lightest.                            |

| Field | Value | Function                                                                                                                                    |

|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------|

|       | 0     | Normal display.                                                                                                                             |

| BLANK | 1     | LCD display blanked. The COM signals of LCD driver output inactive levels (LVL4 and LVL1) while SEG signals output normal display patterns. |

| LCDE  | 0     | LCD driver disabled, LCD driver has no output signal and applied to VDD                                                                     |

| LCDE  | 1     | LCD driver Enabled.                                                                                                                         |

Please note that LCD driver must be turned off before the system goes into "sleep" mode. That means user must clear the bit 0 of LCDC to turn off LCD driving circuit before setting bit6 of OP1 to enter sleep mode. Large current might happen if the procedure is not followed.

Please note that LCD driver uses slow clock as clock source. The LCD display will not display normally if it works in Fast clock only mode because the LCD refresh action is too fast.

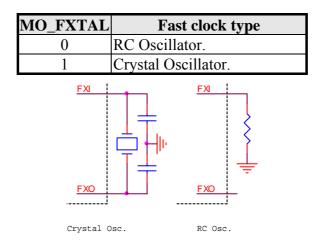

# 10. Oscillators

The MCU is equipped with two clock sources with a variety of selections on the types of oscillators to choose from. The system designer can select oscillator types based on the cost target, timing accuracy requirements etc. Crystal, Resonator or the RC oscillator can be used as fast clock source, components should be placed as close to the pins as possible. The type of oscillator used is selected by mask option MO FXTAL.

The RC oscillator has a built-in capacitor. An external resistor is needed to connect from FXI to GND to determine the oscillation frequency. The capacitance of internal RC oscillator is selected by mask option MO\_RCAP[2..0].

| MO_RCAP[2:0] | Internal RC Cap. (pF) |

|--------------|-----------------------|

| 000          | 2                     |

| 001          | 4                     |

| 010          | 7                     |

| 011          | 14                    |

| 100          | 20                    |

| 101          | 40                    |

| 110 | 50 |

|-----|----|

| 111 | 60 |

The following table shows the combinations of R and C, and the resulting frequency. Please note that oscillation frequency in the table only represents oscillation frequencies of certain samples. The actual oscillation frequency may vary up to  $\pm 15\%$  from lot to lot due to process parameter variations. User must take this into consideration when using this chip in applications.

**Ring Oscillator Frequency Table**

| $R(K\Omega)$ | 40  | 20  | 14  | 7   | 4   | 2    |     |

|--------------|-----|-----|-----|-----|-----|------|-----|

| 30.20        | 0.8 | 1.5 | 2.0 | 3.0 | 4.0 | 5.0  | MHz |

| 19.92        | 1.2 | 2.2 | 2.8 | 4.4 | 5.6 | 7.0  | MHz |

| 9.98         | 2.3 | 4.0 | 5.1 | 7.5 | 9.4 | 11.4 | MHz |

Two types of oscillator, crystal and RC, can be used as slow clock selectable by mask option MO\_SXTAL. If used time keeping function or other applications that required the accurate timing, crystal oscillator is recommended. If the timing accuracy is not important, then RC type oscillator can be used to reduce cost.

With two clock sources available, the system can switch among operation modes of Normal, Slow, Idle, and Sleep modes by the setting of OP1 and OP2 registers as shown in tables below to suit the needs of application such as high speed or low power, etc.

| OP1   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Field | DRDY  | STOP  | SLOW  | INTE  | T2E   | T1E   | Z     | C     |

| Mode  | R/W   |

| Reset | 1     | 0     | 0     | 0     | 0     | 0     | -     | -     |

| OP2   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Field | IDLE  | PNWK  | TCWK  | TBE   |       | TBS   |       |       |

| Mode  | R/W   | R     | R     | R/W   | W     | W     | W     | W     |

| Reset | 0 | _ | _ | 0 | _ | _ | _ | _ |

|-------|---|---|---|---|---|---|---|---|

|       |   |   |   | - |   |   |   |   |

If the dual clock mode is used, the LCD display, Timer1 and Timer Base will derive its clock source from slow clock while the other blocks will operate with the fast clock.

# 11. General Purpose I/O

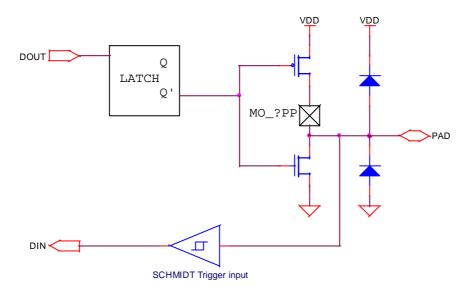

There are three dedicated general purpose I/O port, PRTC, PRTD and PRT10, while PRT15[1..0] and PRT17 are multiplexed with LCD segment driver pins. All the I/O Ports are bi-directional and of non-tri-state output structure. The output has weak sourcing (50  $\mu$ A) and stronger sinking (1 mA) capability and each can be configured as push-pull or open-drain output structure individually by mask option.

When the I/O port is used as input, the weakly high sourcing can be used as weakly pull-up. Open drain can be used if the pull-up is not required and let the external driver to drive the pin. Please note that a floating pad could cause more power consumption since the noise could interfere with the circuit and cause the input to toggle. A '1' needs to be written to port first before reading the input data from the I/O pin. If the PMOS is used as pull-up, care should be taken to avoid the constant power drain by DC path between pull-up and external circuit.

The input port has built-in Schmidt trigger to prevent it from chattering. The hysteresis level of Schmidt trigger is 1/3 VDD.

As pads of PRT15 and PRT17 are shared with LCD segment driver, the function of the pad is determined by mask options. Following table is the setting for MO\_LIO?[...] and MO\_?PP[...] and others related to LCD display setting and pin assignment features.

| MO_LIO?[] | MO_?PP[] | I/O Port          | LCD Pin     |

|-----------|----------|-------------------|-------------|

| 0         | 0        | Open-drain output |             |

| 0         | 1        | Push-pull output  |             |

| 1         | 0        |                   | XX          |

| 1         | 1        |                   | LCD Display |

--: Function not available.

xx: Display enable, but may have abnormal leakage current, do not use.

# 12. Timer1

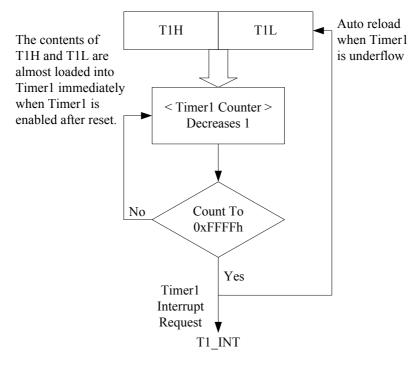

The Timer1 consists of two 8-bit write-only preload registers T1H and T1L and 16-bit down counter. If Timer1 is enabled, the counter will decrement by one with each incoming clock pulse. Timer1 interrupt will be generated when the counter underflows - counts down to FFFFH. And the counter will be automatically reloaded with the value of T1H and T1L.

The clock source of Timer1 is derived from slow clock "SCK" at dual clock or slow clock only mode. And it comes from the fast clock "FCK" at fast clock only mode.

Please note that the interrupt is generated when counter counts from 0000H to FFFFH. If the value of T1H and T1L is N, and count down to FFFFH, the total count is N+1. The content of counter is zero when system resets. Once it is enabled to count at this moment, interrupt will be generated immediately and value of T1H and T1L will be loaded since it counts to FFFFH. So the T1H and T1L value should be set before enabling Timer1.

The Timer1 related control registers are list as below:

| _        |         |          |                     |      |                                                                      |

|----------|---------|----------|---------------------|------|----------------------------------------------------------------------|

| Register | Address | Field    | <b>Bit position</b> | Mode | Description                                                          |

| IER      | 0x02    | TC1_IER  | 2                   | R/W  | 0: TC1 interrupt is disabled. (default) 1: TC1 interrupt is enabled. |

| T1L      | 0x03    | T1L[7:0] | 7~0                 | W    | Low byte of TC1 pre-load value                                       |

| T1H      | 0x04    | T1H[7:0] | 7~0                 | W    | High byte of TC1 pre-load value                                      |

| OP1      | 0x09    | TC1E     | 2                   | R/W  | 0: TC1 is disabled. (default) 1: TC1 is enabled.                     |

# 13. Timer2

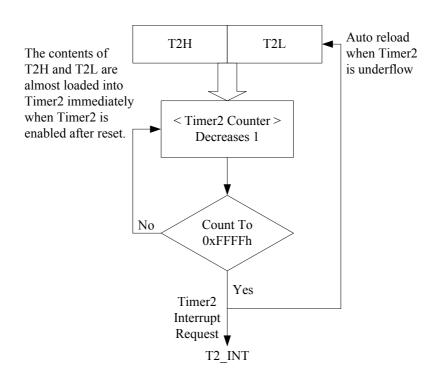

Timer2 is similar in structure to Timer1 except that clock source of Timer2 comes from the system clock "Fsys"/1.5. The system clock "Fsys" varies depending on the operation modes of the MCU.

The Timer2 consists of two 8-bit write-only preload registers T2H and T2L and 16-bit down counter. If Timer2 is enabled, counter will decrement by one with each incoming clock pulse. Timer2 interrupt will be generated when the counter underflows - counts down to FFFFH. And it will be automatically reloaded with the value of T2H and T2L.

Please note that the interrupt signal is generated when counter counts from 0000H to FFFFH. If the value of counter is N, and count down to FFFFH, the total count is N+1. The content of counter is zero when system resets. Once it is enabled to count at this time, the interrupt will be generated immediately and value of T2H and T2L will be loaded since the counter counts to FFFFH. So the T2H and T2L value should be set before enabling Timer2.

The Timer2 related control registers are list as below:

| Register | Address | Field    | Bit position | Mode   | Description                             |

|----------|---------|----------|--------------|--------|-----------------------------------------|

| IER      | 0x02    | TC2 IER  | 1            | R/W    | 0: TC2 interrupt is disabled. (default) |

| ILK      | 0X02    | TC2_IER  | 1            | IX/ VV | 1: TC2 interrupt is enabled.            |

| T2L      | 0x05    | T2L[7:0] | 7~0          | W      | Low byte of TC2 pre-load value          |

| T2H      | 0x06    | T2H[7:0] | 7~0          | W      | High byte of TC2 pre-load value         |

| OD1      | 000     | TC2E     | 2            | D/W/   | 0: TC2 is disabled. (default)           |

| OP1      | 0x09    | TC2E     | 3            | R/W    | 1: TC2 is enabled.                      |

# 14. Time Base

The TB timer is used to generate time-out interrupt at fixed period. The time-out frequency of TB is determined by dividing slow clock with a factor selected in OP2[3..0]. TBE (Time Base Enable) bit controls enable or disable of the circuit.

| OP2   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Field | IDLE  | PNWK  | TCWK  | TBE   |       | TBS   | [30]  |       |

| Mode  | R/W   | R     | R     | R/W   | R/W   | R/W   | R/W   | R/W   |

| Reset | 0     | -     | -     | 0     | -     | -     | -     | -     |

| TBE | Function          |

|-----|-------------------|

| 0   | Disable Time Base |

| 1   | Enable Time Base  |

For example, if the slow clock is 32768 Hz, then the interrupt frequency is as shown in following table.

| TBS[30] | Interrupt Frequency |

|---------|---------------------|

| 0000    | 16.384 KHz          |

| 0001    | 8.192 KHz           |

| 0010    | 4.096 KHz           |

| 0011    | 2.048 KHz           |

| 0100    | 1.024 KHz           |

| 0101    | 512 Hz              |

| 0110    | 256 Hz              |

| 0111    | 128 Hz              |

| 1000    | 64 Hz               |

| TBS[30] | Interrupt Frequency |

|---------|---------------------|

| 1001    | 32 Hz               |

| 1010    | 16 Hz               |

| 1011    | 8 Hz                |

| 1100    | 4 Hz                |

| 1101    | 2 Hz                |

| 1110    | 1 Hz                |

| 1111    | 0.5 Hz              |

# 15. Watch Dog Timer

Watch Dog Timer (WDT) is designed to reset system automatically and prevents system dead lock caused by abnormal hardware activities or program execution. The WDT needs to be enabled in Mask Option.

| MO_WDTE | Function    |

|---------|-------------|

| 0       | WDT disable |

| 1       | WDT enable  |

Using the WDT function, the "CLRWDT" instruction needs to be executed in every possible program path when the program runs normally in order to clears the WDT counter before it overflows, so that the program can operate normally. When abnormal conditions happen to cause the MCU to divert from normal path, the WDT counter will not be cleared and reset signal will be generated to reset the system.

The WDT clock source is the same as TC1 (Timer1 clock), and the WDT reset signal is generated when the counter had counted 32768 clock. The WDT can function in Normal, Slow and Idle Mode. However, WDT will not function during Sleep Mode (as the TC1 clock has stopped.)

# 16. Voice Output

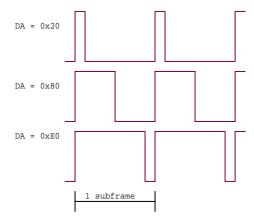

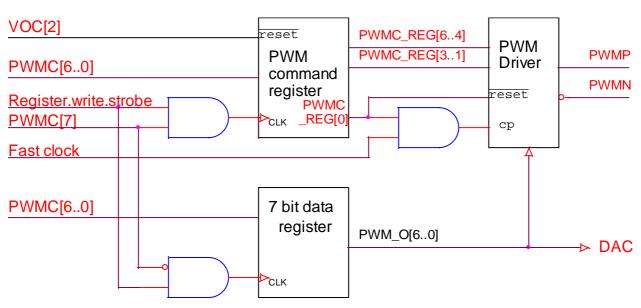

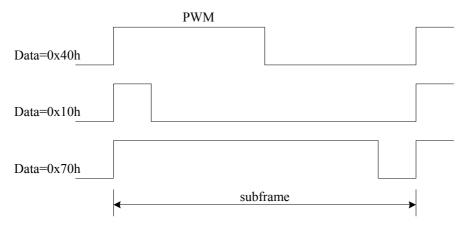

There are 7 or 8 bits DAC/PWM voice output available for user. The 7 bits DAC/PWM output format and configuration are the same as the previous IC of HE80000 series. The 8 bits DAC/PWM format and configuration are new designed and controlled by the VOC and PWMC registers. The selection of 7/8 bits DAC/PWM output is by mask option **MO\_8BVOC.**

| MO_8BVOC | Function             |

|----------|----------------------|

| 0        | 7-bit DAC/PWM output |

| 1        | 8-bit DAC/PWM output |

#### 8-Bit DAC/PWM Output:

The Digital-to-Analog converter converts the 8-bit unsigned speech data which is written into PWMC data register to proportional current output.

| PWMC  | address | Reset | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Field | 0x0E    |       | DA7   | DA6   | DA5   | DA4   | DA3   | DA2   | DA1   | DA0   |

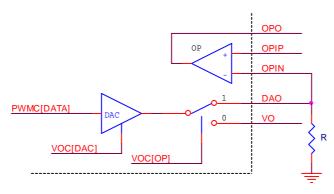

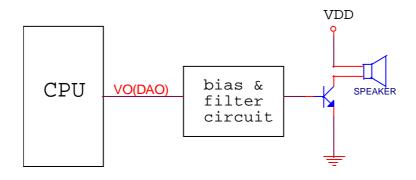

There are two output paths for the DAC. Either VO or DAO can be selected as output port of DAC by VOC register when it is enabled. The VO output is primarily intended for speech generation, although it is not necessary so, while the DAO output path can be used in conjunction with built-in OP comparator to function as an Analog-to-Digital Converter as required in applications such as speech recording, speech recognition or sensor interfaces.

The DAC is enabled by DAC bit of VOC register. When DAC is enabled, the DAC output path can be selected to output to DAO or VO pin by OP bit of VOC register.