SBOS054A - JANUARY 1995 - REVISED JUNE 2004

# High-Speed FET-INPUT OPERATIONAL AMPLIFIERS

#### **FEATURES**

FET INPUT: I<sub>B</sub> = 50pA max

WIDE BANDWIDTH: 8MHz

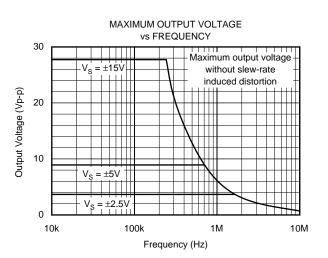

HIGH SLEW RATE: 20V/µs

LOW NOISE: 8nV/√Hz (1kHz)

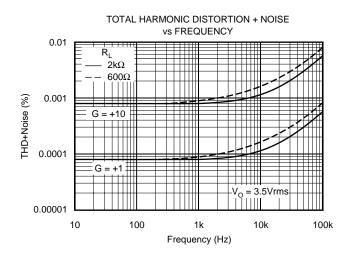

LOW DISTORTION: 0.00008%

● HIGH OPEN-LOOP GAIN: 130dB (600Ω load)

WIDE SUPPLY RANGE: ±2.5 to ±18V

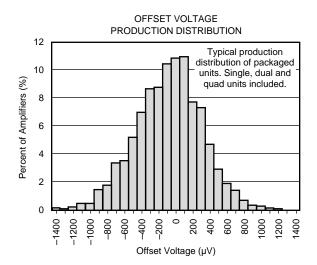

LOW OFFSET VOLTAGE: 500μV max

SINGLE, DUAL, AND QUAD VERSIONS

#### **DESCRIPTION**

The OPA132 series of FET-input op amps provides highspeed and excellent dc performance. The combination of high slew rate and wide bandwidth provide fast settling time. Single, dual, and quad versions have identical specifications for maximum design flexibility. High performance grades are available in the single and dual versions. All are ideal for general-purpose, audio, data acquisition and communications applications, especially where high source impedance is encountered.

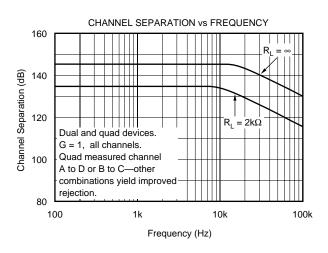

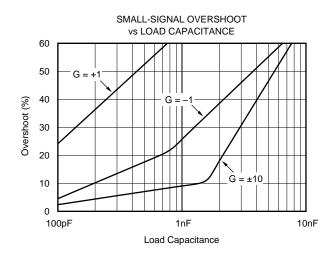

OPA132 op amps are easy to use and free from phase inversion and overload problems often found in common FET-input op amps. Input cascode circuitry provides excellent common-mode rejection and maintains low input bias current over its wide input voltage range. OPA132 series op amps are stable in unity gain and provide excellent dynamic behavior over a wide range of load conditions, including high load capacitance. Dual and quad versions feature completely independent circuitry for lowest crosstalk and freedom from interaction, even when overdriven or overloaded.

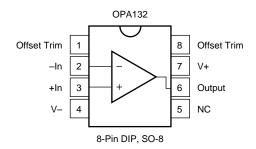

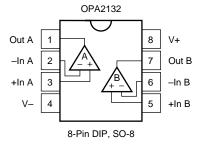

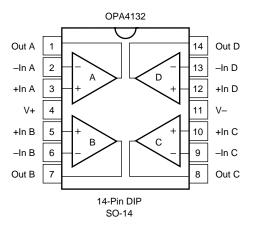

Single and dual versions are available in 8-pin DIP and SO-8 surface-mount packages. Quad is available in 14-pin DIP and SO-14 surface-mount packages. All are specified for -40°C to +85°C operation.

testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, V+ to V             | 36V            |

|-------------------------------------|----------------|

| Input Voltage                       |                |

| Output Short-Circuit <sup>(1)</sup> | Continuous     |

| Operating Temperature               |                |

| Storage Temperature                 | 55°C to +125°C |

| Junction Temperature                | 150°C          |

| Lead Temperature (soldering, 10s)   | 300°C          |

NOTE: (1) Short-circuit to ground, one amplifier per package.

#### PACKAGE/ORDERING INFORMATION

For the most current package and ordering information, see the Package Option Addendum located at the end of this data sheet.

## ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## **SPECIFICATIONS**

At  $T_A$  = +25°C,  $V_S$  = ±15V, unless otherwise noted.

|                                                                                                                                                                                       |                                                                                                                                                                      | OPA132P, U<br>OPA2132P, U |                                                |                      | OPA132PA, UA<br>OPA2132PA, UA<br>OPA4132PA, UA |                     |               |                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------------------------------|----------------------|------------------------------------------------|---------------------|---------------|------------------------------------------------|

| PARAMETER                                                                                                                                                                             | CONDITION                                                                                                                                                            | MIN                       | TYP                                            | MAX                  | MIN                                            | TYP                 | MAX           | UNITS                                          |

| OFFSET VOLTAGE Input Offset Voltage vs Temperature <sup>(1)</sup> vs Power Supply Channel Separation (dual and quad)                                                                  | Operating Temperature Range $V_S = \pm 2.5 V \text{ to } \pm 18 V$ $R_L = 2 k \Omega$                                                                                |                           | ±0.25<br>±2<br>5<br>0.2                        | ±0.5<br>±10<br>15    |                                                | ±0.5<br>*<br>*<br>* | ±2<br>*<br>30 | mV<br>μV/°C<br>μV/V<br>μV/V                    |

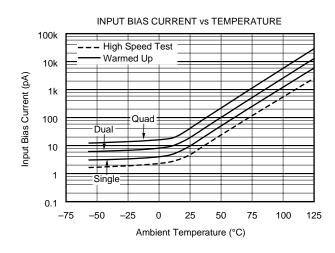

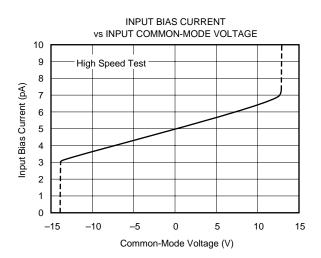

| INPUT BIAS CURRENT Input Bias Current <sup>(2)</sup> vs Temperature Input Offset Current <sup>(2)</sup>                                                                               | $V_{CM} = 0V$ $V_{CM} = 0V$                                                                                                                                          | See                       | +5 E Typical Cu                                | ±50<br>urve<br>= ±50 |                                                | *<br>*<br>*         | *             | pA<br>pA                                       |

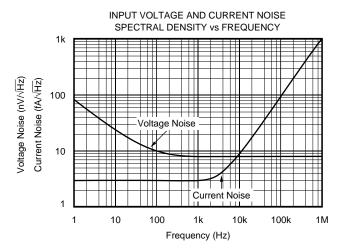

| NOISE Input Voltage Noise Noise Density, f = 10Hz f = 100Hz f = 1kHz f = 10kHz Current Noise Density, f = 1kHz                                                                        |                                                                                                                                                                      |                           | 23<br>10<br>8<br>8<br>3                        |                      |                                                | *<br>*<br>*<br>*    |               | nV/√Hz<br>nV/√Hz<br>nV/√Hz<br>nV/√Hz<br>fA/√Hz |

| INPUT VOLTAGE RANGE<br>Common-Mode Voltage Range<br>Common-Mode Rejection                                                                                                             | $V_{CM} = -12.5V \text{ to } +12.5V$                                                                                                                                 | (V–)+2.5<br>96            | ±13<br>100                                     | (V+)-2.5             | *<br>86                                        | *<br>94             | *             | V<br>dB                                        |

| INPUT IMPEDANCE Differential Common-Mode                                                                                                                                              | V <sub>CM</sub> = -12.5V to +12.5V                                                                                                                                   |                           | 10 <sup>13</sup>    2<br>10 <sup>13</sup>    6 |                      |                                                | *                   |               | $\Omega \parallel pF$ $\Omega \parallel pF$    |

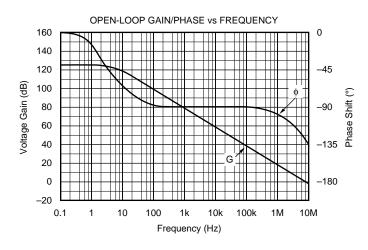

| OPEN-LOOP GAIN Open-Loop Voltage Gain                                                                                                                                                 | $R_L = 10k\Omega, \ V_O = -14.5V \ to \ +13.8V$ $R_L = 2k\Omega, \ V_O = -13.8V \ to \ +13.5V$ $R_L = 600\Omega, \ V_O = -12.8V \ to \ +12.5V$                       | 110<br>110<br>110         | 120<br>126<br>130                              |                      | 104<br>104<br>104                              | *<br>120<br>120     |               | dB<br>dB<br>dB                                 |

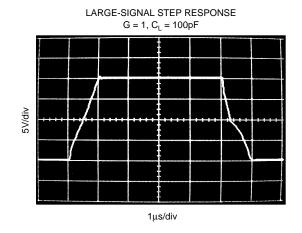

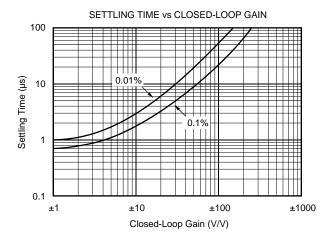

| FREQUENCY RESPONSE Gain-Bandwidth Product Slew Rate Settling Time: 0.1% 0.01% Overload Recovery Time Total Harmonic Distortion + Noise                                                | $G = -1$ , 10V Step, $C_L = 100pF$<br>$G = -1$ , 10V Step, $C_L = 100pF$<br>$G = \pm 1$<br>1kHz, $G = 1$ , $V_O = 3.5$ Vrms<br>$R_L = 2k\Omega$<br>$R_L = 600\Omega$ |                           | 8<br>±20<br>0.7<br>1<br>0.5                    |                      |                                                | ***                 |               | MHz<br>V/µs<br>µs<br>µs<br>µs<br>%             |

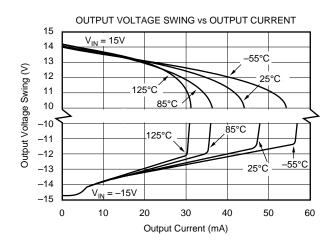

| OUTPUT  Voltage Output, Positive     Negative     Positive     Negative     Positive     Negative     Positive     Negative Short-Circuit Current Capacitive Load Drive (Stable Opera | $R_L = 10k\Omega$ $R_L = 2k\Omega$ $R_L = 600\Omega$                                                                                                                 |                           | (V-)+0.3<br>(V+)-1.2<br>(V-)+0.9               | ırve                 | * * * * * *                                    | * * * * * * * *     |               | V<br>V<br>V<br>V<br>V<br>mA                    |

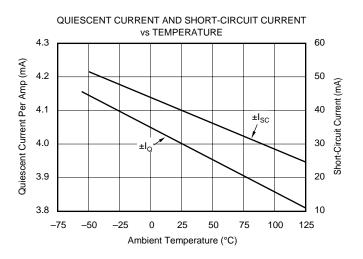

| POWER SUPPLY Specified Operating Voltage Operating Voltage Range Quiescent Current (per amplifier)                                                                                    | I <sub>O</sub> = 0                                                                                                                                                   | ±2.5                      | ±15                                            | ±18<br>±4.8          | *                                              | *                   | *             | V<br>V<br>mA                                   |

| TEMPERATURE RANGE Operating Range Storage Thermal Resistance, $θ$ <sub>JA</sub> 8-Pin DIP SO-8 Surface-Mount 14-Pin DIP SO-14 Surface-Mount                                           |                                                                                                                                                                      | -40<br>-40                | 100<br>150<br>80<br>110                        | +85<br>+125          | *                                              | *<br>*<br>*         | *             | °C<br>°C<br>°C/W<br>°C/W<br>°C/W<br>°C/W       |

<sup>\*</sup> Specifications same as OPA132P, OPA132U.

NOTES: (1) Guaranteed by wafer test. (2) High-speed test at  $T_J$  = 25°C.

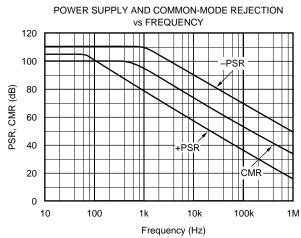

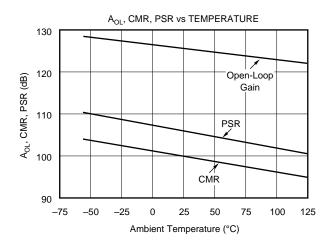

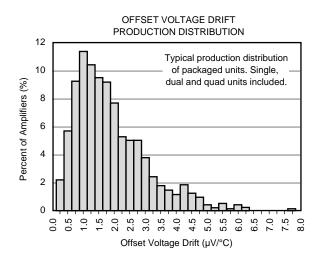

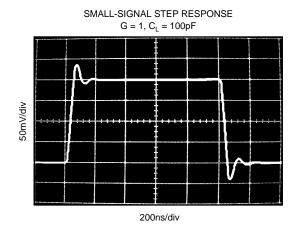

## TYPICAL PERFORMANCE CURVES

At  $T_A$  = +25°C,  $V_S$  = ±15V,  $R_L$  = 2k $\Omega$ , unless otherwise noted.

## TYPICAL PERFORMANCE CURVES (Cont.)

At  $T_A$  = +25°C,  $V_S$  = ±15V,  $R_L$  = 2k $\Omega$ , unless otherwise noted.

## **TYPICAL PERFORMANCE CURVES (Cont.)**

At  $T_A$  = +25°C,  $V_S$  = ±15V,  $R_L$  = 2k $\Omega$ , unless otherwise noted.

#### APPLICATIONS INFORMATION

OPA132 series op amps are unity-gain stable and suitable for a wide range of general-purpose applications. Power supply pins should be bypassed with 10nF ceramic capacitors or larger.

OPA132 op amps are free from unexpected output phasereversal common with FET op amps. Many FET-input op amps exhibit phase-reversal of the output when the input common-mode voltage range is exceeded. This can occur in voltage-follower circuits, causing serious problems in control loop applications. OPA132 series op amps are free from this undesirable behavior. All circuitry is completely independent in dual and quad versions, assuring normal behavior when one amplifier in a package is overdriven or short-circuited.

#### **OPERATING VOLTAGE**

OPA132 series op amps operate with power supplies from  $\pm 2.5 \text{V}$  to  $\pm 18 \text{V}$  with excellent performance. Although specifications are production tested with  $\pm 15 \text{V}$  supplies, most behavior remains unchanged throughout the full operating voltage range. Parameters which vary significantly with operating voltage are shown in the typical performance curves.

#### **OFFSET VOLTAGE TRIM**

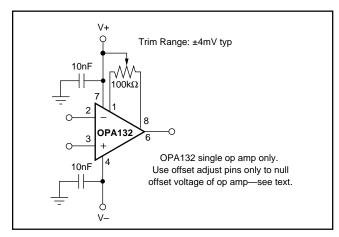

Offset voltage of OPA132 series amplifiers is laser trimmed and usually requires no user adjustment. The OPA132 (single op amp version) provides offset voltage trim connections on pins 1 and 8. Offset voltage can be adjusted by connecting a potentiometer as shown in Figure 1. This adjustment should be used only to null the offset of the op amp, not to adjust system offset or offset produced by the signal source. Nulling offset could degrade the offset voltage drift behavior of the op amp. While it is not possible to predict the exact change in drift, the effect is usually small.

FIGURE 1. OPA132 Offset Voltage Trim Circuit.

#### **INPUT BIAS CURRENT**

The FET-inputs of the OPA132 series provide very low input bias current and cause negligible errors in most applications. For applications where low input bias current is crucial, junction temperature rise should be minimized. The input bias current of FET-input op amps increases with temperature as shown in the typical performance curve "Input Bias Current vs Temperature."

The OPA132 series may be operated at reduced power supply voltage to minimize power dissipation and temperature rise. Using  $\pm 3V$  supplies reduces power dissipation to one-fifth that at  $\pm 15V$ .

The dual and quad versions have higher total power dissipation than the single, leading to higher junction temperature. Thus, a warmed-up quad will have higher input bias current than a warmed-up single. Furthermore, an SOIC will generally have higher junction temperature than a DIP at the same ambient temperature because of a larger  $\theta_{JA}$ . Refer to the specifications table.

Circuit board layout can also help minimize junction temperature rise. Temperature rise can be minimized by soldering the devices to the circuit board rather than using a socket. Wide copper traces will also help dissipate the heat by acting as an additional heat sink.

Input stage cascode circuitry assures that the input bias current remains virtually unchanged throughout the full input common-mode range of the OPA132 series. See the typical performance curve "Input Bias Current vs Common-Mode Voltage."

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp (3)   |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|---------------------|

| OPA132P          | OBSOLETE              | PDIP            | Р                  | 8    |                | TBD                       | Call TI          | Call TI             |

| OPA132P1         | OBSOLETE              | PDIP            | Р                  | 8    |                | TBD                       | Call TI          | Call TI             |

| OPA132PA         | OBSOLETE              | PDIP            | Р                  | 8    |                | TBD                       | Call TI          | Call TI             |

| OPA132PA2        | OBSOLETE              | PDIP            | Р                  | 8    |                | TBD                       | Call TI          | Call TI             |

| OPA132U          | ACTIVE                | SOIC            | D                  | 8    | 100            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR |

| OPA132U/2K5      | ACTIVE                | SOIC            | D                  | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR |

| OPA132U/2K5G4    | ACTIVE                | SOIC            | D                  | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR |

| OPA132U1         | OBSOLETE              | PDIP            | Р                  | 8    |                | TBD                       | Call TI          | Call TI             |

| OPA132UA         | ACTIVE                | SOIC            | D                  | 8    | 100            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR |

| OPA132UA/2K5     | ACTIVE                | SOIC            | D                  | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR |

| OPA132UA/2K5E4   | ACTIVE                | SOIC            | D                  | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR |

| OPA132UA/2K5G4   | ACTIVE                | SOIC            | D                  | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR |

| OPA132UA2        | OBSOLETE              | PDIP            | Р                  | 8    |                | TBD                       | Call TI          | Call TI             |

| OPA132UAE4       | ACTIVE                | SOIC            | D                  | 8    | 100            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR |

| OPA132UAG4       | ACTIVE                | SOIC            | D                  | 8    | 100            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR |

| OPA132UG4        | ACTIVE                | SOIC            | D                  | 8    | 100            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR |

| OPA2132P         | ACTIVE                | PDIP            | Р                  | 8    | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type  |

| OPA2132PA        | ACTIVE                | PDIP            | Р                  | 8    | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type  |

| OPA2132U         | ACTIVE                | SOIC            | D                  | 8    | 100            | Pb-Free<br>(RoHS)         | CU NIPDAU        | Level-3-260C-168 HR |

| OPA2132U/2K5     | ACTIVE                | SOIC            | D                  | 8    | 2500           | Pb-Free<br>(RoHS)         | CU NIPDAU        | Level-3-260C-168 HR |

| OPA2132U/2K5E4   | ACTIVE                | SOIC            | D                  | 8    | 2500           | Pb-Free<br>(RoHS)         | CU NIPDAU        | Level-3-260C-168 HR |

| OPA2132UA        | ACTIVE                | SOIC            | D                  | 8    | 100            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR |

| OPA2132UA/2K5    | ACTIVE                | SOIC            | D                  | 8    | 2500           | Pb-Free<br>(RoHS)         | CU NIPDAU        | Level-3-260C-168 HR |

| OPA2132UA/2K5E4  | ACTIVE                | SOIC            | D                  | 8    | 2500           | Pb-Free<br>(RoHS)         | CU NIPDAU        | Level-3-260C-168 HR |

| OPA2132UAE4      | ACTIVE                | SOIC            | D                  | 8    | 100            | Pb-Free<br>(RoHS)         | CU NIPDAU        | Level-3-260C-168 HR |

| OPA2132UAG4      | ACTIVE                | SOIC            | D                  | 8    | 100            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR |

| OPA2132UE4       | ACTIVE                | SOIC            | D                  | 8    | 100            | Pb-Free<br>(RoHS)         | CU NIPDAU        | Level-3-260C-168 HR |

#### PACKAGE OPTION ADDENDUM

12-Feb-2007

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| OPA4132PA        | OBSOLETE              | PDIP            | N                  | 14   |                | TBD                       | Call TI          | Call TI                      |

| OPA4132UA        | ACTIVE                | SOIC            | D                  | 14   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| OPA4132UA/2K5    | ACTIVE                | SOIC            | D                  | 14   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| OPA4132UA/2K5E4  | ACTIVE                | SOIC            | D                  | 14   | 2500           | Pb-Free<br>(RoHS)         | CU NIPDAU        | Level-3-260C-168 HR          |

| OPA4132UAE4      | ACTIVE                | SOIC            | D                  | 14   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

**Green (RoHS & no Sb/Br):** TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

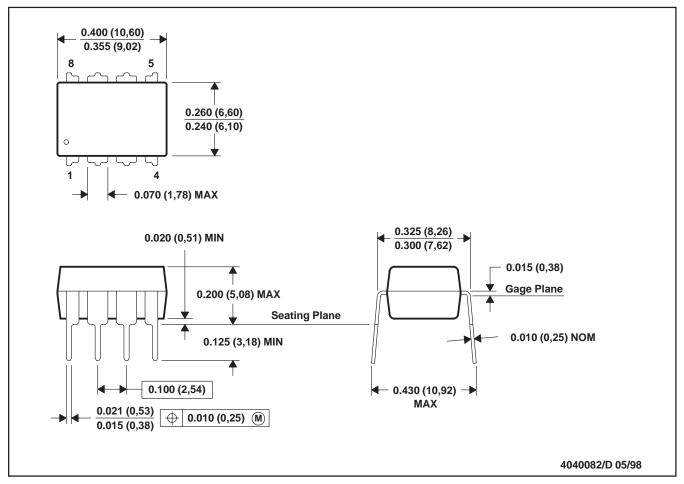

#### P (R-PDIP-T8)

#### PLASTIC DUAL-IN-LINE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-001

For the latest package information, go to http://www.ti.com/sc/docs/package/pkg\_info.htm

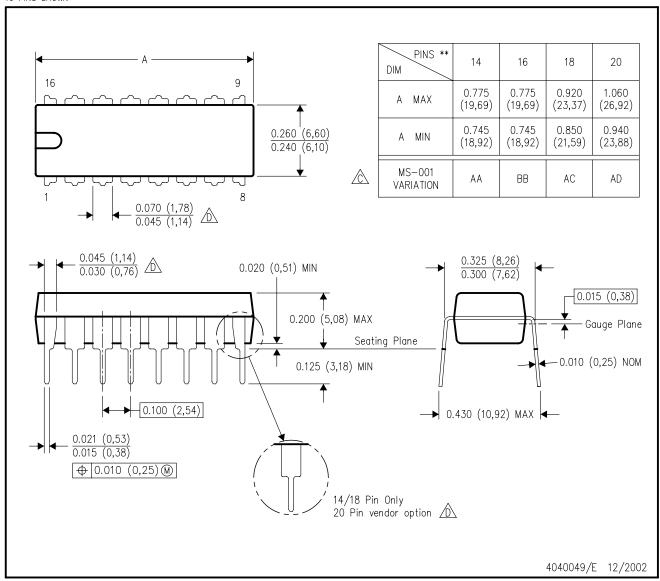

## N (R-PDIP-T\*\*)

### PLASTIC DUAL-IN-LINE PACKAGE

16 PINS SHOWN

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Falls within JEDEC MS-001, except 18 and 20 pin minimum body length (Dim A).

- The 20 pin end lead shoulder width is a vendor option, either half or full width.

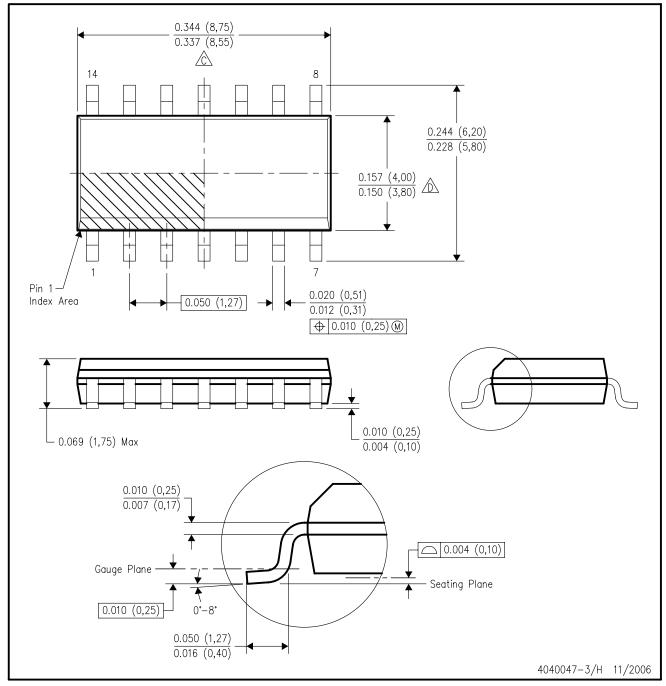

## D (R-PDSO-G14)

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 (0,15) per end.

- Body width does not include interlead flash. Interlead flash shall not exceed .017 (0,43) per side.

- E. Reference JEDEC MS-012 variation AB.

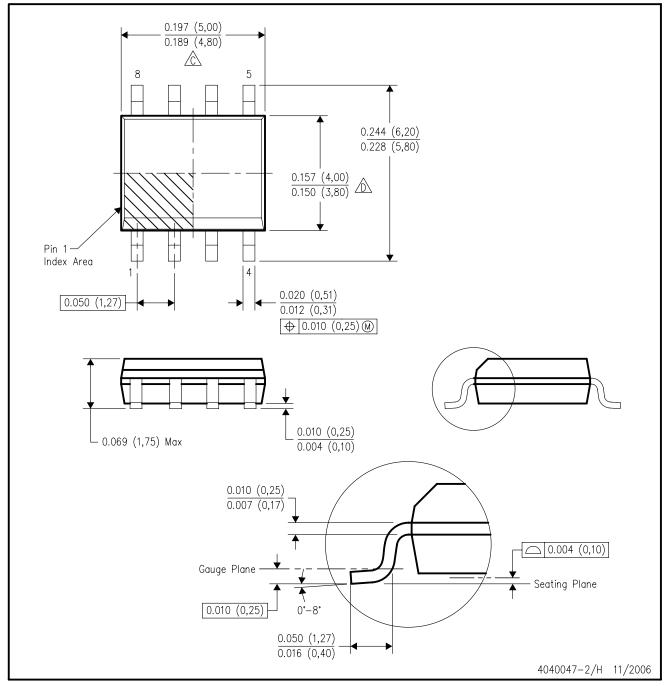

## D (R-PDSO-G8)

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 (0,15) per end.

- Body width does not include interlead flash. Interlead flash shall not exceed .017 (0,43) per side.

- E. Reference JEDEC MS-012 variation AA.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products           |                        | Applications       |                           |

|--------------------|------------------------|--------------------|---------------------------|

| Amplifiers         | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters    | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface          | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic              | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt         | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers   | microcontroller.ti.com | Security           | www.ti.com/security       |

| Low Power Wireless | www.ti.com/lpw         | Telephony          | www.ti.com/telephony      |

|                    |                        | Video & Imaging    | www.ti.com/video          |

|                    |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265