www.nanoamp.com

# 512K × 16 Bits × 2 Banks Low Power Synchronous DRAM

#### DESCRIPTION

These N16D1633LPA are low power 16,777,216 bits CMOS Synchronous DRAM organized as 2 banks of 524,288 words x 16 bits. These products are offering fully synchronous operation and are referenced to a positive edge of the clock. All inputs and outputs are synchronized with the rising edge of the clock input. The data paths are internally pipelined to achieve very high bandwidth. All input and output voltage levels are compatible with LVTTL.

#### **Features**

- · JEDEC standard 3.0V/3.3V power supply.

- · Auto refresh and self refresh.

- All pins are compatible with LVTTL interface.

- · 4K refresh cycle / 64ms.

- · Programmable Burst Length and Burst Type.

- 1, 2, 4, 8 or Full Page for Sequential Burst.

- 4 or 8 for Interleave Burst.

- Programmable CAS Latency: 2,3 clocks.

- · Programmable Driver Strength Control.

- Full Strength or 1/2, 1/4 of Full Strength

- Deep Power Down Mode

- · All inputs and outputs referenced to the positive edge of the system clock.

- · Data mask function by DQM.

- Internal dual banks operation.

- · Burst Read Single Write operation.

- · Special Function Support.

- -PASR (Partial Array Self Refresh)

- -Auto TCSR(Temperature Compensated Self Refresh)

- Automatic precharge, includes CONCURRENT **Auto Precharge Mode and controlled Precharge**

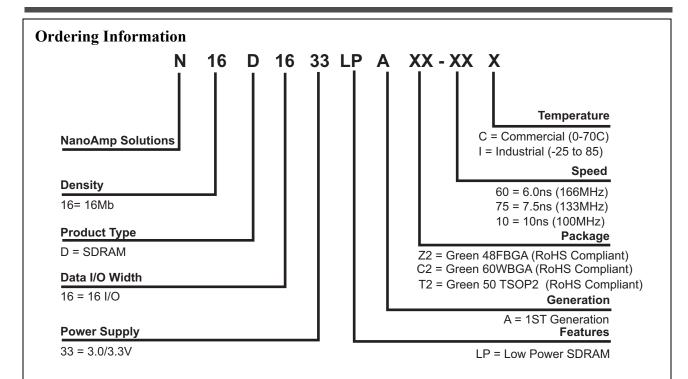

## **Table 1: Ordering Information**

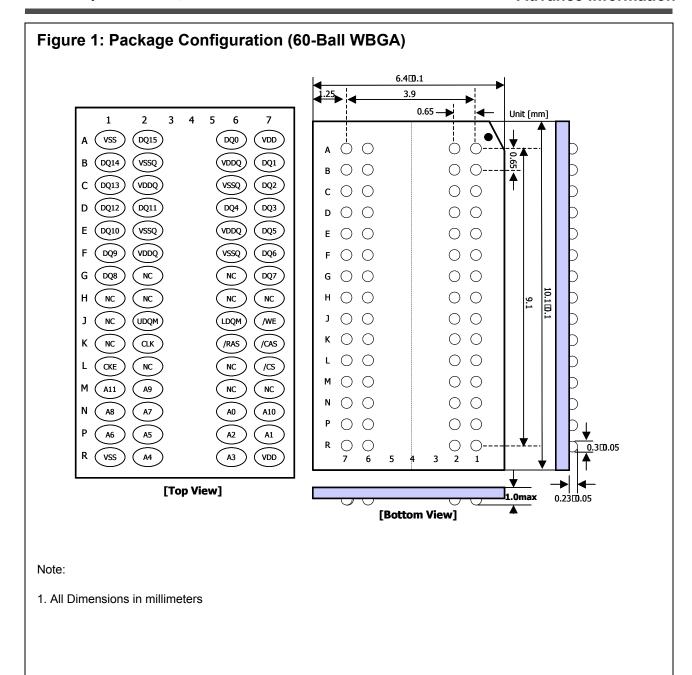

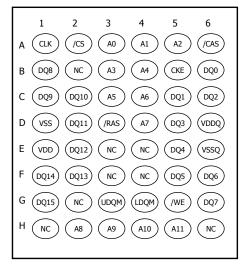

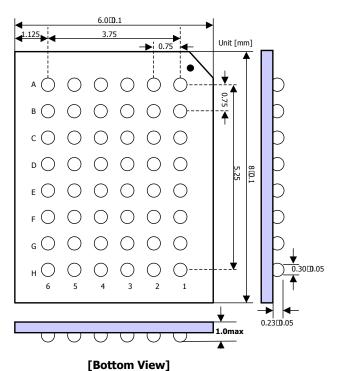

| PART NO.          | CLOCK Freq. | Temperature | VDD/VDDQ        | INTERLEAVE | PACKAGE                 |

|-------------------|-------------|-------------|-----------------|------------|-------------------------|

| N16D1633LPAZ2-75I | 133MHz      |             |                 |            | 48-Ball Green           |

| N16D1633LPAZ2-10I | 100MHz      |             |                 |            | FBGA                    |

| N16D1633LPAC2-60I | 166MHz      | -25° C to   |                 |            | 00 Dall O               |

| N16D1633LPAC2-75I | 133MHz      | 85° C       | 3.0V/3.0V<br>or | IVTTI      | 60-Ball Green<br>WBGA   |

| N16D1633LPAC2-10I | 100MHz      |             | 3.3V/3.3V       | LVIIL      | W.56/ (                 |

| N16D1633LPAT2-60I | 166MHz      |             |                 |            | 50 Dia 0                |

| N16D1633LPAT2-75I | 133MHz      |             |                 |            | 50-Pin Green<br>TSOP II |

| N16D1633LPAT2-10I | 100MHz      |             |                 |            |                         |

[Top View]

Note:

1. All Dimensions in millimeters

## **Table 2: Pin Descriptions**

| PIN             | PIN NAME                                                      | DESCRIPTIONS                                                                                                                        |

|-----------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| CLK             | System Clock                                                  | The system clock input. All other inputs are registered to the SDRAM on the rising edge of the CLK                                  |

| CKE             | Clock Enable                                                  | Controls internal clock signal and when deactivated, the SDRAM will be one of the states among power down, suspend or self refresh. |

| /CS             | Chip Select                                                   | Enable or disable all inputs except CLK, CKE and DQM                                                                                |

| A11             | Bank Address                                                  | Selects bank to be activated during /RAS activity Selects bank to be read/written during /CAS activity                              |

| A0~A10          | Address                                                       | Row Address : RA0~RA10 Column Address: CA0~CA7 Auto Precharge : A10                                                                 |

| /RAS, /CAS, /WE | Row Address Strobe,<br>Column Address Strobe,<br>Write Enable | /RAS, /CAS and /WE define the operation<br>Refer function truth table for details                                                   |

| LDQM/UDQM       | Data Input/Output Mask                                        | Controls output buffers in read mode and masks input data in write mode                                                             |

| DQ0~DQ15        | Data Input/Output                                             | Multiplexed data input/output pin                                                                                                   |

| VDD/VSS         | Power Supply/Ground                                           | Power supply for internal circuits and input buffers                                                                                |

| VDDQ/VSSQ       | Data Output Power/Ground                                      | Power Supply for output buffers                                                                                                     |

| NC              | No Connection                                                 | No Connection                                                                                                                       |

Note: M11(A11) must be sest to "0" to select mode Register (vs. the Extend Mode Register)

#### **Burst Type**

Accesses within a given burst may be programmed to be either sequential or interleaved; this is referred to as the burst type and is selected via bit M3. The ordering of accesses within a burst is determined by the burst length, the burst type and the starting column address, as shown in Table 3.

**Table 3: Burst Definition**

| Burst<br>Length |                            | ing Co<br>ddres |    | Order of Access Within a Burst                                          |                 |  |  |  |

|-----------------|----------------------------|-----------------|----|-------------------------------------------------------------------------|-----------------|--|--|--|

| Length          | A2                         | A1              | A0 | Sequential                                                              | Interleave      |  |  |  |

| 2               |                            |                 | 0  | 0-1                                                                     | 0-1             |  |  |  |

| _               |                            |                 | 1  | 1-0                                                                     | 1-0             |  |  |  |

|                 |                            | 0               | 0  | 0-1-2-3                                                                 | 0-1-2-3         |  |  |  |

| 4               |                            | 0               | 1  | 1-2-3-0                                                                 | 1-0-3-2         |  |  |  |

| -               |                            | 1               | 0  | 2-3-0-1                                                                 | 2-3-0-1         |  |  |  |

|                 |                            | 1               | 1  | 3-0-1-2                                                                 | 3-2-1-0         |  |  |  |

|                 | 0                          | 0               | 0  | 0-1-2-3-4-5-6-7                                                         | 0-1-2-3-4-5-6-7 |  |  |  |

|                 | 0                          | 0               | 1  | 1-2-3-4-5-6-7-0                                                         | 1-0-3-2-5-4-7-6 |  |  |  |

|                 | 0                          | 1               | 0  | 2-3-4-5-6-7-0-1                                                         | 2-3-0-1-6-7-4-5 |  |  |  |

| 8               | 0                          | 1               | 1  | 3-4-5-6-7-0-1-2                                                         | 3-2-1-0-7-6-5-4 |  |  |  |

| 0               | 1                          | 0               | 0  | 4-5-6-7-0-1-2-3                                                         | 4-5-6-7-0-1-2-3 |  |  |  |

|                 | 1                          | 0               | 1  | 5-6-7-0-1-2-3-4                                                         | 5-4-7-6-1-0-3-2 |  |  |  |

|                 | 1                          | 1               | 0  | 6-7-0-1-2-3-4-5                                                         | 6-7-4-5-2-3-0-1 |  |  |  |

|                 | 1                          | 1               | 1  | 7-0-1-2-3-4-5-6                                                         | 7-6-5-4-3-2-1-0 |  |  |  |

| Full<br>Page    | N=A0~7<br>(Location 0-256) |                 |    | $C_n$ , $C_{n+1}$ . $C_{n+2}$ , $C_{n+3}$ , $C_{n+4}$ $C_{n-1}$ , $C_n$ | Not Supported   |  |  |  |

#### Note:

- 1. For full-page accesses: y = 256

- 2. For a burst length of two, A1-A7 select the block-of-two burst; A0 selects the starting column within the block.

- 3. For a burst length of four, A2-A7 select the block-offour burst; A0-A1 select the starting column within the block.

- 4. For a burst length of eight, A3-A7 select the block-ofeight burst; A0-A2 select the starting column within the block.

- 5. For a full-page burst, the full row is selected and A0-A7 select the starting column.

- 6. Whenever a boundary of the block is reached within a given sequence above, the following access wraps within the block.

- 7. For a burst length of one, A0-A7 select the unique column to be accessed, and mode register bit M3 is ignored.

#### **FUNCTIONAL DESCRIPTION**

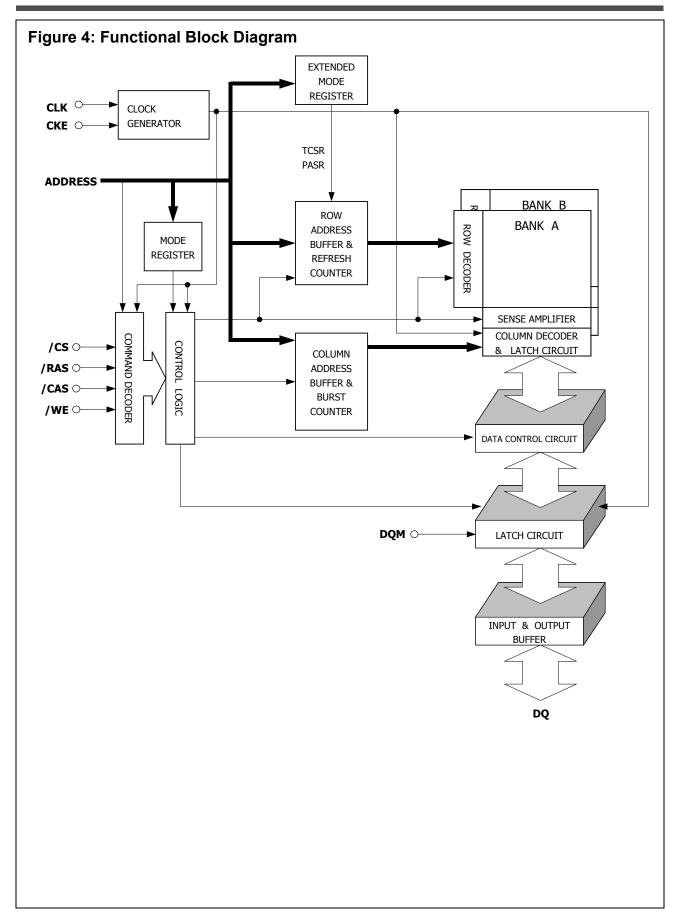

In general, this 16Mb SDRAM (512K x 16Bits x 2banks) is a dual-bank DRAM that operates at 3.3V and includes a synchronous interface (all signals are registered on the positive edge of the clock signal, CLK). Each of the 8,388,608-bit banks is organized as 2,048 rows by 256 columns by 16-bits. Read and write accesses to the SDRAM are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an ACTIVE command, which is then followed by a READ or WRITE command. The address bits registered coincident with the ACTIVE command are used to select the bank and row to be accessed (A11 select the bank, A0-A10 select the row). The address bits (A11 select the bank, A0-A7 select the column) registered coincident with the READ or WRITE command are used to select the starting column location for the burst access. Prior to normal operation, the SDRAM must be initialized. The following sections provide detailed information covering device initialization, register definition, command descriptions and device operation.

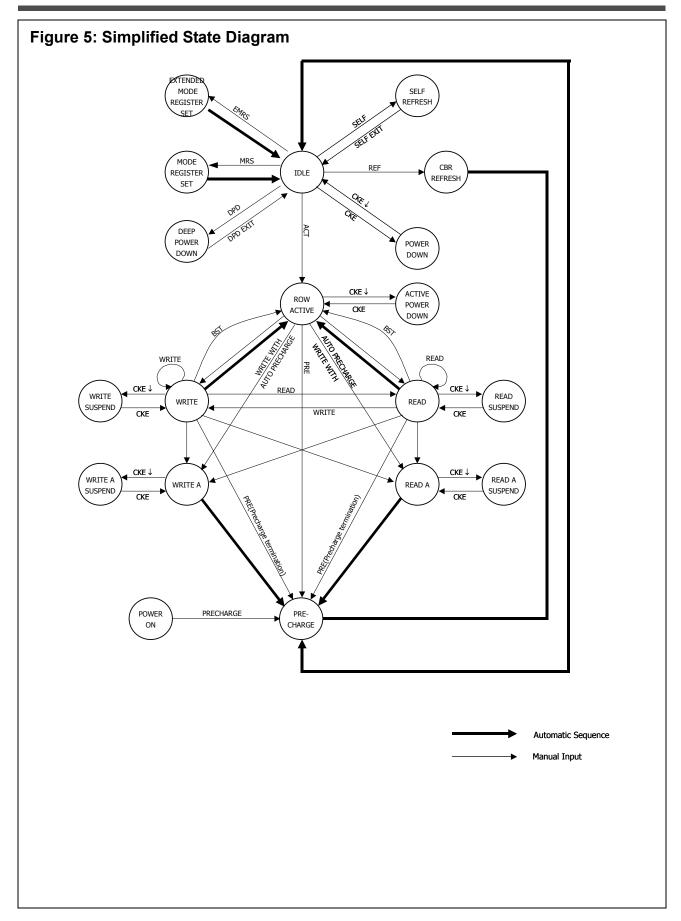

### Power up and Initialization

SDRAMs must be powered up and initialized in a predefined manner. Operational procedures other than those specified may result in undefined operation. Once power is applied to VDD and VDDQ(simultaneously) and the clock is stable(stable clock is defined as a signal cycling within timing constraints specified for the clock pin), the SDRAM requires a 100µs delay prior to issuing any command other than a COMMAND INHIBIT or NOP. CKE must be held high during the entire initialization period until the RECHARGE command has been issued. Starting at some point during this 100µs period and continuing at least through the end of this period, COMMAND INHIBIT or NOP commands should be applied. Once the 100µs delay has been satisfied with at least one COMMAND INHIBIT or NOP command having been applied, a PRECHARGE command should be applied. All banks must then be precharged, thereby placing the device in the all banks idle state.

Once in the idle state, two AUTO REFRESH cycles must be performed. After the AUTO REFRESH cycles are complete, the SDRAM is ready for mode register programming. Because the mode register will power up in an unknown state, it should be loaded prior to applying any operational command. And a extended mode register set command will be issued to program specific mode of self refresh operation(PASR). The following these cycles, the Low Power SDRAM is ready for normal operation.

#### REGISTER DEFINITION

#### **Mode Register**

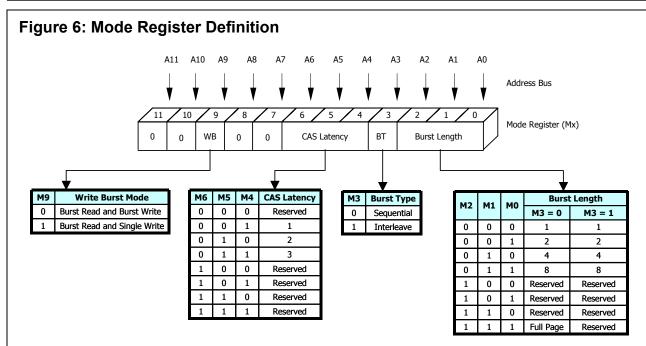

The mode register is used to define the specific mode of operation of the SDRAM. This definition includes the selection of a burst length, a burst type, a CAS latency, an operating mode and a write burst mode. The mode register is programmed via the LOAD MODE REGISTER command and will retain the stored information until it is programmed again or the device loses power. Mode register bits M0-M2 specify the burst length, M3 specifies the type of burst (sequential or interleaved), M4-M6 specify the CAS latency, M7 and M8 specify the operating mode, M9 specifies the write burst mode, and M10 should be set to zero. M11 should be set to zero to prevent extended mode register. The mode register must be loaded when all banks are idle, and the controller must wait the specified time before initiating the subsequent operation. Violating either of these requirements will result in unspecified operation.

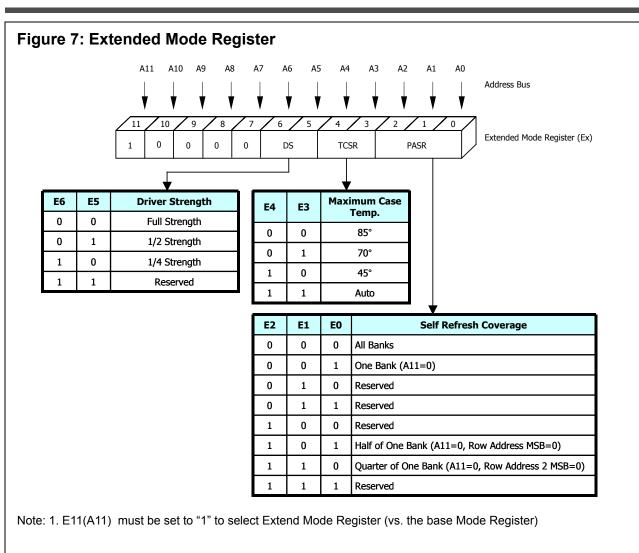

#### EXTENDED MODE REGISTER

The Extended Mode Register controls the functions beyond those controlled by the Mode Register. These additional functions are special features of the BATRAM device. They include Temperature Compensated Self Refresh (TCSR) Control, and Partial Array Self Refresh (PASR) and Driver Strength (DS). The Extended Mode Register is programmed via the Mode Register Set command (A11=1) and retains the stored information until it is programmed again or the device loses power. The Extended Mode Register must be programmed with E7 through E10 set to "0". The Extended Mode Register must be loaded when all banks are idle and no bursts are in progress, and the controller must wait the specified time before before initiating any subsequent operation. Violating either of these requirements results in unspecified operation.

### **Burst Length**

Read and write accesses to the SDRAM are burst oriented, with the burst length being programmable, as shown in Figure 1. The burst length determines the maximum number of column locations that can be accessed for a given READ or WRITE command. Burst lengths of 1, 2, 4 or 8 locations are available for both the sequential and the interleaved burst types, and a full-page burst is available for the sequential type. The full-page burst is used in conjunction with the BURST TERMINATE command to generate arbitrary burst lengths.

Reserved states should not be used, as unknown operation or incompatibility with future versions may result. When a READ or WRITE command is issued, a block of columns equal to the burst length is effectively selected. All accesses for that burst take place within this block, meaning that the burst will wrap within the block if a boundary is reached. The block is uniquely selected by A1-A7 when the burst length is set to two; by A2-A7 when the burst length is set to four; and by A3-A7 when the burst length is set to eight. The remaining (least significant) address bit(s) is (are) used to select the starting location within the block. Full-page bursts wrap within the page if the boundary is reached.

## Bank(Row) Active

The Bank Active command is used to activate a row in a specified bank of the device. This command is initiated by activating /CS, /RAS and deasserting /CAS, /WE at the positive edge of the clock. The value on the A11 selects the bank, and the value on the A0-A10 selects the row. This row remains active for column access until a precharge command is issued to that bank. Read and write operations can only be initiated on this activated bank after the minimum tRCD time is passed from the activate command.

#### Read

The READ command is used to initiate the burst read of data. This command is initiated by activating /CS, /CAS, and deasserting /WE, /RAS at the positive edge of the clock. A11 input select the bank, A0-A7 address inputs select the starting column location. The value on input A10 determines whether or not Auto Precharge is used. If Auto Precharge is selected the row being accessed will be precharged at the end of the READ burst; if Auto Precharge is not selected, the row will remain active for subsequent accesses. The length of burst and the CAS latency will be determined by the values programmed during the MRS command.

#### Write

The WRITE command is used to initiate the burst write of data. This command is initiated by activating /CS, /CAS, /WE and deasserting /RAS at the positive edge of the clock. A11 input select the bank, A0-A7 address inputs select the starting column location. The value on input A10 determines whether or not Auto Precharge is used. If Auto Precharge is selected the row being accessed will be precharged at the end of the WRITE burst; if Auto Precharge is not selected, the row will remain active for subsequent accesses.

## **CAS Latency**

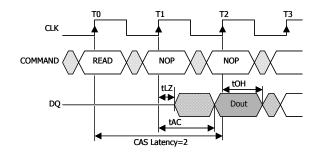

The CAS latency is the delay, in clock cycles, between the registration of a READ command and the availability of the first piece of output data. The latency can be set to two or three clocks. If a READ command is registered at clock edge n, and the latency is m clocks, the data will be available by clock edge n + m. The DQs will start driving as a result of the clock edge one cycle earlier (n + m - 1), and provided that the relevant access times are met, the data will be valid by clock edge n + m. For example, assuming that the clock cycle time is such that all relevant access times are met, if a READ command is registered at T0 and the latency is programmed to two clocks, the DQs will start driving after T1 and the data will be valid by T2, as shown in Figure 2. Reserved states should not be used as unknown operation or incompatibility with future versions may result.

## Figure 8: CAS Latency

### **Operating Mode**

The normal operating mode is selected by setting M7 and M8 to zero; the other combinations of values for M7 and M8 are reserved for future use and/or test modes. The programmed burst length applies to both READ and WRITE bursts. Test modes and reserved states should not be used because unknown operation or incompatibility with future versions may result.

#### **Write Burst Mode**

When M9 = 0, the burst length programmed via M0-M2 applies to both READ and WRITE bursts; when M9 = 1, the programmed burst length applies to READ bursts, but write accesses are single-location (nonburst) accesses.

**Table 4: Command Truth Table**

| COMMAND                               | CKEn-1   | CKEn | cs | RAS | CAS | WE | DQM | ADDR     | A10 | Note |

|---------------------------------------|----------|------|----|-----|-----|----|-----|----------|-----|------|

| Command Inhibit (NOP)                 | Н        | Х    | Н  | Х   | Х   | Х  | Χ   | Х        |     |      |

| No Operation (NOP)                    | Н        | Х    | L  | Н   | Н   | Н  | Х   | Х        |     |      |

| Mode Register Set                     | Н        | Х    | L  | L   | L   | L  | Х   | OP-CODE  |     | 4    |

| Extended Mode Register Set            | Н        | Х    | L  | L   | L   | L  | Х   | OP-CO    | DE  | 4    |

| Active (select bank and activate row) | Н        | Х    | L  | L   | Н   | Н  | Х   | Bank/R   | ow  |      |

| Read                                  | Н        | Х    | L  | Н   | L   | Н  | L/H | Bank/Col | L   | 5    |

| Read with Autoprecharge               | Н        | Х    | L  | Н   | L   | Н  | L/H | Bank/Col | Н   | 5    |

| Write                                 | Н        | Х    | L  | Н   | L   | L  | L/H | Bank/Col | L   | 5    |

| Write with Autoprecharge              | Н        | Х    | L  | Н   | L   | L  | L/H | Bank/Col | Н   | 5    |

| Precharge All Banks                   | Н        | Х    | L  | L   | Н   | L  | Х   | Х        | Н   |      |

| Precharge Selected Bank               | Н        | Х    | L  | L   | Н   | L  | Х   | Bank L   |     |      |

| Burst stop                            | Н        | Н    | L  | Н   | Н   | L  | Х   | Х        |     |      |

| Auto Refresh                          | Н        | Н    | L  | L   | L   | Н  | Х   | X        |     | 3    |

| Self Refresh Entry                    | Н        | L    | L  | L   | L   | Н  | Х   | Х        |     | 3    |

| Self Refresh Exit                     | L        | Н    | Н  | Х   | Х   | Х  | Х   | Х        |     | 2    |

| Sell Reliesh Exit                     | <u> </u> |      | L  | Н   | Н   | Н  | ^   | ^        |     |      |

| Precharge Power Down Entry            | Н        | L    | Н  | Х   | Х   | Х  | Х   | Х        |     |      |

| Frecharge Fower Down Entry            |          | _    | L  | Н   | Н   | Н  | ^   | ^        |     |      |

| Brookerge Down Evit                   | L        | Н    | Н  | Х   | Х   | Х  | Х   | Х        |     |      |

| Precharge Down Exit                   | <u> </u> |      | L  | Н   | Н   | Н  | ^   | ^        |     |      |

| Clock Suspend Entry                   | Н        | L    | Н  | Х   | Х   | Х  | Х   | Х        |     |      |

| Clock Suspend Linky                   |          | -    | L  | V   | V   | V  | _ ^ | , A      |     |      |

| Clock Suspend Exit                    | L        | Н    |    | 2   | X   |    | Х   | Х        |     |      |

| Deep Power Down Entry                 | Н        | L    | L  | Н   | Н   | L  | Х   | Х        |     | 6    |

| Deep Power Down Exit                  | L        | Н    |    | 2   | X   |    | Х   | Х        |     |      |

#### Note:

- 1. CKEn is the logic state of CKE at clock edge n; CKEn-1 was the state of CKE at the previous clock edge. H: High Level, L: Low Level, X: Don't Care, V: Valid

- 2. Exiting Self Refresh occurs by asynchronously bringing CKE from low to high and will put the device in the all banks idle state once tXSR is met. Command Inhibit or NOP commands should be issued on any clock edges occuring during the tXSR period. A mimum of two NOP commands must be provided during tXSR period.

- 3. During refresh operation, internal refresh counter controls row addressing; all inputs and I/Os are "Don't Care" except for CKE.

- 4. A0-A10 define OP CODE written to the mode register, and BA must be issued 0 in the mode register set, and 1 in the extended mode register set.

- 5. DQM "L" means the data Write/Ouput Enable and "H" means the Write inhibit/Output High-Z. Write DQM Latency is 0 CLK and Read DQM Latency is 2 CLK.

- 6. Standard SDRAM parts assign this command sequence as Burst Terminate. For Bat Ram parts, the Burst Terminate command is assigned to the Deep Power Down function.

**Table 5: Function Truth Table**

| Current       |     |      |      |     | Com  | mand         |                      | Action                                     | Note  |

|---------------|-----|------|------|-----|------|--------------|----------------------|--------------------------------------------|-------|

| State         | /CS | /RAS | /CAS | /WE | A11  | A0-A10       | Description          | Action                                     | NOLE  |

|               | L   | L    | L    | L   | OP C | ODE          | Mode Register Set    | Set the Mode Register                      | 14    |

|               | L   | L    | L    | Н   | Χ    | Х            | Auto or Self Refresh | Start Auto or Self Refresh                 | 5     |

|               | L   | L    | Н    | L   | ВА   | Х            | Precharge            | No Operation                               |       |

| IDLE          | L   | L    | Н    | Н   | ВА   | Row Addr     | Bank Active          | Activate the Specific Bank and Row         |       |

|               | L   | Н    | L    | L   | ВА   | Col Addr/A10 | Write/Write AP       | ILLEGAL                                    | 4     |

|               | L   | Н    | L    | Н   | ВА   | Col Addr/A10 | Read/Read AP         | ILLEGAL                                    | 4     |

|               | L   | Н    | Н    | Н   | Χ    | Х            | NOP                  | NOP                                        | 3     |

|               | Н   | Х    | Х    | Х   | Х    | Х            | Device Deselect      | NOP or Power Down                          | 3     |

|               | L   | L    | L    | L   | OP C | ODE          | Mode Register Set    | ILLEGAL                                    | 13,14 |

|               | L   | L    | L    | Н   | Χ    | Х            | Auto or Self Refresh | ILLEGAL                                    | 13    |

|               | L   | L    | Н    | L   | ВА   | Х            | Precharge            | Precharge                                  | 7     |

|               | L   | L    | Н    | Н   | ВА   | Row Addr     | Bank Active          | ILLEGAL                                    | 4     |

| ROW<br>ACTIVE | L   | Н    | L    | L   | ВА   | Col Addr/A10 | Write/Write AP       | Start Write : Optional<br>AP(A10 = H)      | 6     |

|               | L   | Н    | L    | Н   | ВА   | Col Addr/A10 | Read/Read AP         | Start Read: Optional<br>AP(A10 = H)        | 6     |

|               | L   | Н    | Н    | Н   | Х    | Х            | NOP                  | NOP                                        |       |

|               | Н   | Х    | Х    | Х   | Х    | Х            | Device Deselect      | NOP                                        |       |

|               | L   | L    | L    | L   | OP C | ODE          | Mode Register Set    | ILLEGAL                                    | 13,14 |

|               | L   | L    | L    | Н   | Х    | Х            | Auto or Self Refresh | ILLEGAL                                    | 13    |

|               | L   | L    | Н    | L   | ВА   | Х            | Precharge            | Termination Burst :<br>Start the Precharge |       |

|               | L   | L    | Н    | Н   | ВА   | Row Addr     | Bank Active          | ILLEGAL                                    | 4     |

| READ          | L   | Н    | L    | L   | ВА   | Col Addr/A10 | Write/Write AP       | Termination Burst:<br>Start Write(AP)      | 8,9   |

|               | L   | Н    | L    | Н   | ВА   | Col Addr/A10 | Read/Read AP         | Termination Burst:<br>Start Read(AP)       | 8     |

|               | L   | Н    | Н    | Н   | Х    | Х            | NOP                  | Continue the Burst                         |       |

|               | Н   | Х    | Х    | Х   | Х    | Х            | Device Deselect      | Continue the Burst                         |       |

|               | L   | L    | L    | L   | OP C | ODE          | Mode Register Set    | ILLEGAL                                    | 13,1  |

|               | L   | L    | L    | Н   | Х    | Х            | Auto or Self Refresh | ILLEGAL                                    | 13    |

|               | L   | L    | Н    | L   | ВА   | Х            | Precharge            | Termination Burst :<br>Start the Precharge |       |

|               | L   | L    | Н    | Н   | ВА   | Row Addr     | Bank Active          | ILLEGAL                                    | 4     |

| WRITE         | L   | Н    | L    | L   | ВА   | Col Addr/A10 | Write/Write AP       | Termination Burst:<br>Start Write(AP)      | 8,9   |

|               | L   | Н    | L    | Н   | ВА   | Col Addr/A10 | Read/Read AP         | Termination Burst:<br>Start Read(AP)       | 8     |

|               | L   | Н    | Н    | Н   | Х    | Х            | NOP                  | Continue the Burst                         |       |

|               | Н   | Х    | Х    | Х   | Х    | Х            | Device Deselect      | Continue the Burst                         |       |

**Table 5: Function Truth Table**

| Current      |     |      |      |     | Com  | mand         |                      | Action                                 | Note        |

|--------------|-----|------|------|-----|------|--------------|----------------------|----------------------------------------|-------------|

| State        | /CS | /RAS | /CAS | /WE | A11  | A0-A10       | Description          | Action                                 | Note        |

|              | L   | L    | L    | L   | OP C | ODE          | Mode Register Set    | ILLEGAL                                | 13,14       |

|              | L   | L    | L    | Н   | Х    | Х            | Auto or Self Refresh | ILLEGAL                                | 13          |

| READ         | L   | L    | Н    | L   | ВА   | Х            | Precharge            | ILLEGAL                                | 4,12        |

| with         | L   | L    | Н    | Н   | ВА   | Row Addr     | Bank Active          | ILLEGAL                                | 4,12        |

| AUTO<br>PRE- | L   | Н    | L    | L   | ВА   | Col Addr/A10 | Write/Write AP       | ILLEGAL                                | 12          |

| CHARGE       | L   | Н    | L    | Н   | ВА   | Col Addr/A10 | Read/Read AP         | ILLEGAL                                | 12          |

|              | L   | Н    | Н    | Н   | Х    | Х            | NOP                  | Continue the Burst                     |             |

|              | Н   | Х    | Х    | Х   | Х    | Х            | Device Deselect      | Continue the Burst                     |             |

|              | L   | L    | L    | L   | OP C | ODE          | Mode Register Set    | ILLEGAL                                | 13,14       |

|              | L   | L    | L    | Н   | Χ    | Х            | Auto or Self Refresh | ILLEGAL                                | 13          |

| WRITE        | L   | L    | Н    | L   | ВА   | Х            | Precharge            | ILLEGAL                                | 4,12        |

| with         | L   | L    | Н    | Н   | ВА   | Row Addr     | Bank Active          | ILLEGAL                                | 4,12        |

| AUTO<br>PRE- | L   | Н    | L    | L   | ВА   | Col Addr/A10 | Write/Write AP       | ILLEGAL                                | 12          |

| CHARGE       | L   | Н    | L    | Н   | ВА   | Col Addr/A10 | Read/Read AP         | ILLEGAL                                | 12          |

|              | L   | Н    | Н    | Н   | Х    | Х            | NOP                  | Continue the Burst                     |             |

|              | Н   | Х    | Х    | Х   | Х    | Х            | Device Deselect      | Continue the Burst                     |             |

|              | L   | L    | L    | L   | OP C | ODE          | Mode Register Set    | ILLEGAL                                | 13,14       |

|              | L   | L    | L    | Н   | Х    | Х            | Auto or Self Refresh | ILLEGAL                                | 13          |

|              | L   | L    | Н    | L   | ВА   | х            | Precharge            | No Operation: Bank(s) Idle after tRP   |             |

| PRE-         | L   | L    | Н    | Н   | ВА   | Row Addr     | Bank Active          | ILLEGAL                                | 4,12        |

| CHARG-       | L   | Н    | L    | L   | ВА   | Col Addr/A10 | Write/Write AP       | ILLEGAL                                | 4,12        |

| ING          | L   | Н    | L    | Н   | ВА   | Col Addr/A10 | Read/Read AP         | ILLEGAL                                | 4,12        |

|              | L   | Н    | Н    | Н   | Х    | х            | NOP                  | No Operation: Bank(s) Idle after tRP   |             |

|              | Н   | Х    | Х    | х   | х    | х            | Device Deselect      | No Operation: Bank(s) Idle after tRP   |             |

|              | L   | L    | L    | L   | OP C | ODE          | Mode Register Set    | ILLEGAL                                | 13,14       |

|              | L   | L    | L    | Н   | Χ    | Х            | Auto or Self Refresh | ILLEGAL                                | 13          |

|              | L   | L    | Н    | L   | ВА   | Х            | Precharge            | ILLEGAL                                | 4,12        |

| ROW          | L   | L    | Н    | Н   | ВА   | Row Addr     | Bank Active          | ILLEGAL                                | 4, 11<br>12 |

| ACTIVAT-     | L   | Н    | L    | L   | ВА   | Col Addr/A10 | Write/Write AP       | ILLEGAL                                | 4,12        |

| ING          | L   | Н    | L    | Н   | ВА   | Col Addr/A10 | Read/Read AP         | ILLEGAL                                | 4,12        |

|              | L   | Н    | Н    | Н   | х    | х            | NOP                  | No Operation: Row Activated after tRCD |             |

|              | Н   | Х    | Х    | Х   | х    | х            | Device Deselect      | No Operation: Row Activated after tRCD |             |

**Table 5: Function Truth Table**

| Current                                              |     |      |      |     | Com  | mand         |                      | Action                                     | Note       |

|------------------------------------------------------|-----|------|------|-----|------|--------------|----------------------|--------------------------------------------|------------|

| State                                                | /CS | /RAS | /CAS | /WE | A11  | A0-A10       | Description          | Action                                     | Note       |

|                                                      | L   | L    | L    | L   | OP C | ODE          | Mode Register Set    | ILLEGAL                                    | 13,1       |

|                                                      | L   | L    | L    | Н   | Χ    | Х            | Auto or Self Refresh | ILLEGAL                                    | 13         |

|                                                      | L   | L    | Н    | L   | BA   | Х            | Precharge            | ILLEGAL                                    | 4,13       |

|                                                      | L   | L    | Н    | Н   | BA   | Row Addr     | Bank Active          | ILLEGAL                                    | 4,12       |

| WRITE<br>RECOV-                                      | L   | Н    | L    | L   | ВА   | Col Addr/A10 | Write/Write AP       | Start Write : Optional<br>AP(A10 = H)      |            |

| ERING                                                | L   | Н    | L    | Н   | ВА   | Col Addr/A10 | Read/Read AP         | Start Write : Optional<br>AP(A10 = H)      | 9          |

|                                                      | L   | Н    | Н    | Н   | Х    | Х            | NOP                  | No Operation : Row Active after tDPL       |            |

|                                                      | Н   | Х    | Х    | Х   | Х    | х            | Device Deselect      | No Operation : Row Active after tDPL       |            |

|                                                      | L   | L    | L    | L   | OP C | ODE          | Mode Register Set    | ILLEGAL                                    | 13,1       |

|                                                      | L   | L    | L    | Н   | Х    | Х            | Auto or Self Refresh | ILLEGAL                                    | 13         |

|                                                      | L   | L    | Н    | L   | ВА   | Х            | Precharge            | ILLEGAL                                    | 4,13       |

| Write<br>Recover-<br>ing with<br>Auto Pre-<br>charge | L   | L    | Н    | Н   | BA   | Row Addr     | Bank Active          | ILLEGAL                                    | 4,12       |

|                                                      | L   | Н    | L    | L   | BA   | Col Addr/A10 | Write/Write AP       | ILLEGAL                                    | 4,12       |

|                                                      | L   | Н    | L    | Н   | ВА   | Col Addr/A10 | Read/Read AP         | ILLEGAL                                    | 4,9,<br>12 |

|                                                      | L   | Н    | Н    | Н   | Х    | Х            | NOP                  | No Operation : Precharge after tDPL        |            |

|                                                      | Н   | Х    | Х    | Х   | Х    | Х            | Device Deselect      | No Operation : Precharge after tDPL        |            |

|                                                      | L   | L    | L    | L   | OP C | ODE          | Mode Register Set    | ILLEGAL                                    | 13,1       |

|                                                      | L   | L    | L    | Н   | Х    | Х            | Auto or Self Refresh | ILLEGAL                                    | 13         |

|                                                      | L   | L    | Н    | L   | ВА   | Х            | Precharge            | ILLEGAL                                    | 13         |

| DEEDEO                                               | L   | L    | Н    | Н   | BA   | Row Addr     | Bank Active          | ILLEGAL                                    | 13         |

| REFRES<br>HING                                       | L   | Н    | L    | L   | BA   | Col Addr/A10 | Write/Write AP       | ILLEGAL                                    | 13         |

|                                                      | L   | Н    | L    | Н   | BA   | Col Addr/A10 | Read/Read AP         | ILLEGAL                                    | 13         |

|                                                      | L   | Н    | Н    | Н   | Х    | X            | NOP                  | No Operation : Idle after tRC              |            |

|                                                      | Н   | Х    | Х    | Х   | Х    | Х            | Device Deselect      | No Operation : Idle after tRC              |            |

|                                                      | L   | L    | L    | L   | OP C | ODE          | Mode Register Set    | ILLEGAL                                    | 13,1       |

|                                                      | L   | L    | L    | Н   | Х    | Х            | Auto or Self Refresh | ILLEGAL                                    | 13         |

|                                                      | L   | L    | Н    | L   | BA   | Х            | Precharge            | ILLEGAL                                    | 13         |

| Mada                                                 | L   | L    | Н    | Н   | BA   | Row Addr     | Bank Active          | ILLEGAL                                    | 13         |

| Mode<br>Register                                     | L   | Н    | L    | L   | BA   | Col Addr/A10 | Write/Write AP       | ILLEGAL                                    | 13         |

| Accessing                                            | L   | Н    | L    | Н   | BA   | Col Addr/A10 | Read/Read AP         | ILLEGAL                                    | 13         |

|                                                      | L   | Н    | Н    | Н   | Х    | Х            | NOP                  | No Operation : Idle after 2<br>Clock Cycle |            |

|                                                      | Н   | Х    | Х    | Х   | Х    | Х            | Device Deselect      | No Operation : Idle after 2<br>Clock Cycle |            |

## NanoAmp Solutions, Inc.

**Advance Information**

#### Note:

- 1. H: Logic High, L: Logic Low, X: Don't care, BA: Bank Address, AP: Auto Precharge.

- 2. All entries assume that CKE was active during the preceding clock cycle.

- 3. If both banks are idle and CKE is inactive, then in power down cycle

- 4. Illegal to bank in specified states. Function may be legal in the bank indicated by Bank Address, depending on the state of that bank.

- 5. If both banks are idle and CKE is inactive, then Self Refresh mode.

- 6. Illegal if tRCD is not satisfied.

- 7. Illegal if tRAS is not satisfied.

- 8. Must satisfy burst interrupt condition.

- 9. Must satisfy bus contention, bus turn around, and/or write recovery requirements.

- 10. Must mask preceding data which don't satisfy tDPL.

- 11. Illegal if tRRD is not satisfied

- 12. Illegal for single bank, but legal for other banks in multi-bank devices.

- 13. Illegal for all banks.

- 14. Mode Register Set and Extended Mode Register Set is same command truth table except A11.

**Table 6: CKE Truth Table**

| Current                     | С             | KE               |     |      | С    | omman | d   |         |                                                            | Note |

|-----------------------------|---------------|------------------|-----|------|------|-------|-----|---------|------------------------------------------------------------|------|

| Current<br>State            | Prev<br>Cycle | Current<br>Cycle | /CS | /RAS | /CAS | /WE   | A11 | A0-A10  | Action                                                     |      |

|                             | Н             | Х                | Х   | Х    | Х    | Х     | Х   | Х       | INVALID                                                    | 2    |

| -                           | L             | Н                | Н   | Х    | Х    | Х     | Х   | Х       | Exit Self Refresh with<br>Device Deselect                  | 3    |

| Self                        | L             | Н                | L   | Н    | Н    | Н     | Х   | х       | Exit Self Refresh with No Operation                        | 3    |

| Refresh                     | L             | Н                | L   | Н    | Н    | L     | Х   | Х       | ILLEGAL                                                    | 3    |

| •                           | L             | Н                | L   | Н    | L    | Х     | Х   | Х       | ILLEGAL<br>ILLEGAL                                         | 3    |

| -                           | L             | Н                | L   | L    | Х    | Х     | Х   | Х       |                                                            | 3    |

| -                           | L             | L                | Х   | Х    | Х    | Х     | Х   | Х       | Maintain Self Refresh                                      |      |

|                             | Н             | Х                | Х   | Х    | Х    | Х     | Х   | Х       | INVALID                                                    | 2    |

| =                           |               |                  | Н   | Х    | Х    | Х     | Х   | Х       | Power Down Mode                                            |      |

|                             | L             | Н                | L   | Н    | Н    | Н     | Х   | Х       | Exit, All Banks Idle                                       | 3    |

| Power                       |               |                  |     | L    | Х    | Х     | Х   | Х       |                                                            |      |

| Down                        | L             | Н                | L   | Х    | L    | Х     | Х   | Х       | ILLEGAL                                                    | 3    |

|                             |               |                  |     | Х    | Х    | L     | Х   | Х       |                                                            |      |

|                             | L             | L                | Х   | Х    | Х    | Х     | Х   | х       | Maintain Power Down<br>Mode                                |      |

|                             | Н             | Х                | Х   | Х    | Х    | Х     | Х   | Х       | INVALID                                                    | 2    |

| Deep<br>Power               | L             | Н                | Х   | Х    | Х    | Х     | Х   | х       | Deep Power Down<br>Mode Set                                | 6    |

| Down                        | L             | L                | Х   | Х    | Х    | Х     | Х   | х       | Maintain Deep Power<br>Down Mode                           |      |

|                             | Н             | Н                | Н   | Х    | Х    | Х     |     |         | Refer to the Idle State                                    | 4    |

| =                           | Н             | Н                | L   | Н    | Х    | Х     |     |         | section of the Current                                     | 4    |

| =                           | Н             | Н                | L   | L    | Н    | Х     |     |         | State Truth Table                                          | 4    |

| =                           | Н             | Н                | L   | L    | L    | Н     | Х   | Х       | Auto Refresh                                               |      |

| -                           | Н             | Н                | L   | L    | L    | L     |     | Op-Code | Mode Register Set                                          | 5    |

| All Bank<br>Idle            | Н             | L                | Н   | Х    | Х    | Х     |     |         | Refer to the Idle State                                    | 4    |

| 0                           | Н             | L                | L   | Н    | Х    | Х     |     |         | section of the Current                                     | 4    |

|                             | Н             | L                | L   | L    | Н    | Х     |     |         | State Truth Table                                          | 4    |

| -                           | Н             | L                | L   | L    | L    | Н     | Х   | Х       | Entry Self Refresh                                         | 5    |

| -                           | Н             | L                | L   | L    | L    | L     |     | Op-Code | Mode Register Set                                          |      |

| =                           | L             | Х                | Х   | Х    | Х    | Х     | Х   | Х       | Power Down                                                 | 5    |

|                             | Н             | Н                | х   | х    | х    | х     | х   | х       | Refer to Operations of<br>the Current State<br>Truth Table |      |

| Any State other than listed | Н             | L                | х   | Х    | Х    | х     | х   | ×       | Begin Clock Suspend next cycle                             |      |

| above                       | L             | Н                | х   | Х    | Х    | х     | х   | ×       | Exit Clock Suspend next cycle                              |      |

|                             | L             | L                | Х   | Х    | Х    | Х     | Х   | х       | Maintain Clock Suspend                                     |      |

## NanoAmp Solutions, Inc.

**Advance Information**

## Note :

- 1. H: Logic High, L: Logic Low, X: Don't care

- 2. For the given current state CKE must be low in the previous cycle.

- 3. When CKE has a low to high transition, the clock and other inputs are re-enabled asynchronously. When exiting power down mode, a NOP (or Device Deselect) command is required on the first positive edge of clock after CKE goes high.

- 4. The address inputs depend on the command that is issued.

- 5. The Precharge Power Down mode, the Self Refresh mode, and the Mode Register Set can only be entered from the all banks idle state.

- 6. When CKE has a low to high transition, the clock and other inputs are re-enabled asynchronously. When exiting deep power down mode, a NOP (or Device Deselect) command is required on the first positive edge of clock after CKE goes high and is maintained for a minimum 100usec.

**Table 7: ABSOLUTE MAXIMUM RATING**

| PARAMETER                          | SYMBOL    | RATING   | UNIT |

|------------------------------------|-----------|----------|------|

| Ambient Temperature (Industrial)   | TA        | -25 ~ 85 | °C   |

| Ambient Temperature (Commerical)   | IA        | 0 ~ 70   |      |

| Storage Temperature                | TSTG      | -55~150  | °C   |

| Voltage on Any Pin Relative to VSS | VIN, VOUT | -1.0~4.6 | V    |

| Voltage on VDD Relative to VSS     | VDD, VDDQ | -1.0~4.6 | V    |

| Short Circuit Output Current       | IOS       | 50       | mA   |

| Power Dissipation                  | PD        | 1        | W    |

#### Note:

Table 8: Capacitance (TA = 25°C, f = 1MHz, VDD = 3.0V or 3.3V)

| PARAMETER                          | PIN                                          | SYMBOL | MIN | MAX | UNIT |

|------------------------------------|----------------------------------------------|--------|-----|-----|------|

|                                    | CLK                                          | CI1    | 2   | 4   | pF   |

| Input Capacitance                  | A0~A11, CKE, /CS<br>/RAS, /CAS, /WE, L(U)DQM | Cl2    | 2   | 4   | pF   |

| Data Input / Output<br>Capacitance | DQ0~DQ15                                     | CIO    | 3   | 5   | pF   |

Table 9: DC CHARACTERISTIC & OPERATION CONDITION (TA = -25 to 85°C)

| PARAMETER                 | SYMBOL | MIN  | TYP | MAX      | UNIT | NOTE         |

|---------------------------|--------|------|-----|----------|------|--------------|

| Power Supply Voltage      | VDD    | 2.7  | 3.0 | 3.6      | V    |              |

| Power Supply Voltage      | VDDQ   | 2.7  | 3.0 | 3.6      | V    | 1            |

| Input High Voltage        | VIH    | 2.2  |     | VDDQ+0.3 | V    | 2            |

| Input Low Voltage         | VIL    | -0.3 | 0   | 0.5      | V    | 3            |

| Output Logic High Current | VOH    | 2.4  |     |          | V    | IOH = -0.1mA |

| Output Logic Low Current  | VOL    |      |     | 0.4      | V    | IOL = +0.1mA |

| Input Leakage Current     | ILI    | -1   |     | 1        | μA   | 4            |

| Output Leakage Current    | ILO    | -1.5 |     | 1.5      | μΑ   | 5            |

#### Note:

- 1. VDDQ must not exceed the level of VDD

- 2. VIH(max) = 5.3V AC. The overshoot voltage duration is  $\leq 3$ ns

- 3. VIL(min) = -2.0V AC. The overshoot voltage duration is  $\leq$  3ns.

- 4. Any input  $0V \le VIN \le VDDQ$ .

Input leakage currents include Hi-Z output leakage for all bi-directional buffers with tri-state outputs

5. DOUT is disabled,  $0V \le VOUT \le VDDQ$ .

<sup>1.</sup> Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

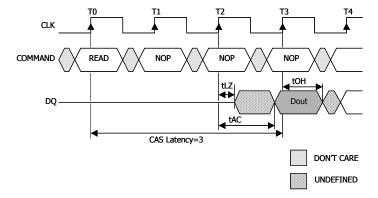

Table 10: AC OPERATNG CONDITION (TA = -25 to 85°C, VDD=3.0V or 3.3V ± 0.3V, VSS = 0V)

| PARAMETER                                           | SYMBOL    | TYP        | UNIT |

|-----------------------------------------------------|-----------|------------|------|

| AC Input High / Low Level Voltage                   | VIH / VIL | 2.4/0.4    | V    |

| Input Timing Measurement Reference Level Voltage    | Vtrip     | 0.5 × VDDQ | V    |

| Input Rise / Fall Time                              | tR / tF   | 1/1        | ns   |

| Output Timing Measurement Reference Level           | Voutref   | 0.5 × VDDQ | V    |

| Output Load Capacitance for Access Time Measurement | CL        | 30         | pF   |

Table 11: DC CHARACTERISTIC (DC Operating Conditions Unless Otherwise Noted)

| PARAMETER                                        |                              |                   | CVM                                                                      | TEST COMPITION                                                                                 | SPEED               |     | LINUT | NOTE |      |

|--------------------------------------------------|------------------------------|-------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------|-----|-------|------|------|

|                                                  |                              |                   | SYM                                                                      | TEST CONDITION                                                                                 | 60                  | 75  | 10    | UNIT | NOTE |

| Operating Current                                |                              |                   | ICC1                                                                     | Burst Length=1, One Bank Active tRC ≥ tRC (min) IOL=0mA                                        |                     | 30  |       | mA   | 1    |

| Precharge St                                     | tandby C                     | urrent in         | ICC2P                                                                    | CKE ≤ VIL (max), tCK=10ns                                                                      |                     | 60  |       | uA   |      |

| Power Down                                       |                              |                   | ICC2PS                                                                   | CKE & CLK ≤VIL(max), tCK=∞                                                                     |                     | 60  | uA    | -    |      |

| _                                                | Precharge Standby Current in |                   |                                                                          | CKE≥VIH (min), /CS≥VIH(min),<br>tCK=10ns<br>Input Signal are changed one time<br>during 2clks. |                     | 6   | mA    | 1    |      |

| Non Power Down Mode                              |                              |                   | ICC2NS                                                                   | CKE≥VIH (min), /CS≥VIH(min)<br>tCK=∞<br>Input signals are stable                               |                     | 1   | mA    |      |      |

| Active Standt                                    | by Currer                    | nt in Power-      | ICC3P                                                                    | CKE≤VIL(max), tCK=10ns                                                                         |                     | 0.5 | mA    |      |      |

| Down Mode                                        |                              |                   | ICC3PS                                                                   | CKE & CLK ≤VIL(max), tCK=∞                                                                     | 0.5                 |     |       | mA   | -    |

| Active Standby Current in Non<br>Power-Down Mode |                              |                   | ICC3N                                                                    | CKE≥VIH(min), /CS≥VIH(min),<br>tCK=10ns<br>Input Signals are changed one time<br>during 2clks  | 12                  |     |       | mA   |      |

|                                                  |                              |                   | ICC3NS                                                                   | CKE≥VIH(min), CLK ≤ VIL(max)<br>tCK=∞<br>Input Signals are stable                              |                     | 6   | mA    |      |      |

| Operating Current<br>(Burst Mode)                |                              | ICC4              | tCK≥tCK(min), IOL=0mA, Page<br>Burst<br>All Banks Activated, tCCD = 1clk | 55                                                                                             | 45                  | 35  | mA    | 1    |      |

| Auto Refresh Current                             |                              | ICC5              | tRC ≥ tRFC (min) All banks active                                        | 30                                                                                             |                     |     | mA    | 2    |      |

|                                                  | PASR                         | TCSR              |                                                                          |                                                                                                | 85 ~ 100<br>70 ~ 85 |     |       | uA   |      |

|                                                  | 2Bank                        | 45~85C            | 1000                                                                     | CKE < 0.2W                                                                                     |                     |     |       |      |      |

| Refresh<br>Current                               | 1Bank                        | -25~45C<br>45~85C | ICC6                                                                     | CKE ≤ 0.2V                                                                                     | 70 ~ 85<br>80 ~ 95  |     |       |      |      |

|                                                  |                              | -25~45C           |                                                                          |                                                                                                | 65 ~ 80             |     |       |      |      |

| Deep Power Down Mode Current                     |                              |                   | ICC7                                                                     |                                                                                                |                     | 2   | uA    |      |      |

#### Note:

- 1. Measured with outputs open.

- 2. Refresh period is 64ms.

Table 12: AC CHARACTERISTIC (AC Operating Conditions Unless Otherwise Noted)

|                                                                   | SYM   |       | 60         | -7   | -75        |      | -10        |      | NOTE |      |

|-------------------------------------------------------------------|-------|-------|------------|------|------------|------|------------|------|------|------|

| PARAMETER                                                         |       | SYIVI | MIN        | MAX  | MIN        | MAX  | MIN        | MAX  | UNIT | NOTE |

| CLK Cycle Time                                                    |       | tCK3  | 6.0        | 1000 | 7.5        | 1000 | 10         | 1000 |      | 1    |

| CLK Cycle Time  CL=2                                              |       | tCK2  | 10         | 1000 | 10         | 1000 | 10         | 1000 | _    | '    |

| Access time from CLK (pos. edge)                                  |       | tAC3  |            | 5.5  |            | 6    |            | 8    |      | 2    |

| " 3 ,                                                             | CL=2  | tAC2  |            | 8    |            | 8    |            | 8    |      |      |

| CLK High-Level Width                                              |       | tCH   | 2.5        |      | 2.5        |      | 2.5        |      |      | 3    |

| CLK Low-Level Width                                               |       | tCL   | 2.5        |      | 2.5        |      | 2.5        |      |      | 3    |

| CKE Used Time                                                     |       | tCKS  | 1.5        |      | 2.0        |      | 2.0        |      |      |      |

| CKE Hold Time                                                     | Timo  | tCKH  | 1.0<br>1.5 |      | 1.0<br>2.0 |      | 1.0<br>2.0 |      |      |      |

| /CS, /RAS, /CAS, /WE, DQM Setup / CS, /RAS, /CAS, /WE, DQM Hold T |       | tCMS  | 1.0        |      | 1.0        |      | 1.0        |      |      |      |

| Address Setup Time                                                | iiie  | tAS   | 1.5        |      | 2.0        |      | 2.0        |      |      |      |

| Address Hold Time                                                 |       | tAH   | 1.0        |      | 1.0        |      | 1.0        |      |      |      |

| Data-In Setup Time                                                |       | tDS   | 1.5        |      | 2.0        |      | 2.0        |      |      |      |

| Data-In Hold Time                                                 |       | tDH   | 1.0        |      | 1.0        |      | 1.0        |      | ns   |      |

| Data-Out High-Impedance Time                                      | CL=3  | tHZ3  |            | 5.5  |            | 6    |            | 8    |      |      |

| from CLK (pos.edge)                                               | CL=2  | tHZ2  |            | 8    |            | 8    |            | 8    |      | 4    |

| Data-Out Low-Impedance Time                                       |       | tLZ   | 1.0        |      | 1.0        |      | 1.0        |      | -    |      |

| Data-Out Hold Time (load)                                         |       | tOH   | 2.5        |      | 2.5        |      | 2.5        |      |      |      |

| Data-Out Hold Time (no load)                                      | ` ,   |       |            |      | 1.8        |      | 1.8        |      | -    |      |

| ACTIVE to PRECHARGE command                                       |       | tRAS  | 42         | 100K | 45         | 100K | 40         | 100K |      |      |

| PRECHARGE command period                                          |       | tRP   | 18         |      | 22.5       |      | 20         |      |      |      |

| ACTIVE bank a to ACTIVE bank a comand                             | tRC   | 60    |            | 67.5 |            | 60   |            |      | 5    |      |

| ACTIVE bank a to ACTIVE bank b comand                             | om-   | tRRD  | 12         |      | 15         |      | 20         |      |      |      |

| ACTIVE to READ or WRITE delay                                     |       | tRCD  | 18         |      | 22.5       |      | 20         |      |      |      |

| READ/WRITE command to READ/WRITE command                          |       | tCCD  | 1          |      | 1          |      | 1          |      | CLK  | 6    |

| WRITE command to input data delay                                 |       | tDWD  | 0          |      | 0          |      | 0          |      | CLK  | 6    |

| Data-in to PRECHARGE command                                      |       | tDPL  | 12         |      | 15         |      | 20         |      | ns   | 7    |

| Data-in to ACTIVE command                                         |       | tDAL  | 30         |      | 37.5       |      | 40         |      | 113  | 7    |

| DQM to data high-impedance during READs                           |       | tDQZ  | 2          |      | 2          |      | 2          |      |      | 6    |

| DQM to data mask during WRITES                                    |       | tDQM  | 0          |      | 0          |      | 0          |      |      | 6    |

| LOAD MODE REGISTER command to ACTIVE or REFRESH command           |       | tMRD  | 2          |      | 2          |      | 2          |      |      | 8    |

| Data-out to high-impedance from                                   | CL=3  | tROH3 | 3          |      | 3          |      | 3          |      | CLK  | 6    |

| PRECHARGE command                                                 | CL=2  | tROH2 | 2          |      | 2          |      | 2          |      |      | U    |

| Last data-in to burst STOP command                                | d     | tBDL  | 1          |      | 1          |      | 1          |      |      | 6    |

| Last data-in to new READ/WRITE com-<br>mand                       |       | tCDL  | 1          |      | 1          |      | 1          |      | -    | 6    |

| CKE to clock disable or power-down mode                           | tCKED | 1     |            | 1    |            | 1    |            | 9    |      |      |

| CKE to clock enable or power-down setup mode                      | tPED  | 1     |            | 1    |            | 1    |            | 9    |      |      |

| Self Refresh Exit Time                                            |       | tSRE  | 1          |      | 1          |      | 1          |      |      | 10   |

## Table 12: AC CHARACTERISTIC (AC Operating Conditions Unless Otherwise Noted)

| PARAMETER                           | SYM   | -60 |     | -75  |     | -10 |     | UNIT | NOTE |

|-------------------------------------|-------|-----|-----|------|-----|-----|-----|------|------|

| PARAMETER                           | 31111 | MIN | MAX | MIN  | MAX | MIN | MAX |      | NOTE |

| Refresh Period (4,096 rows)         | tREF  |     | 64  |      | 64  |     | 64  | ms   |      |

| AUTO REFRESH period                 | tRFC  | 66  |     | 67.5 |     | 70  |     |      | 5    |

| Exit SELF REFRESH to ACTIVE command | tXSR  | 66  |     | 67.5 |     | 70  |     | ns   | 5    |

| Transition time                     | tT    | 0.5 | 1.2 | 0.5  | 1.2 | 0.5 | 1.2 |      |      |

#### Note:

- 1. The clock frequency must remain constant (stable clock is defined as a signal cycling within timing constraints specified for the clock pin) during access or precharge states (READ, WRITE, including tDPL, and PRECHARGE commands). CKE may be used to reduce the data rate.

- 2. tAC at CL = 3 with no load is 5.5ns and is guaranteed by design. Access time to be measured with input signals of 1V/ns edge rate, from 0.8V to 0.2V. If tR > 1ns, then (tR/2-0.5)ns should be added to the parameter.

- 3. AC characteristics assume tT = 1ns. If tR & tF > 1ns, then [(tR+tF)/2-1]ns should be added to the parameter.

- 4. tHZ defines the time at which the output achieves the open circuit condition; it is not a reference to VOH or VOL. The last valid data element will meet tOH before going High-Z.

- 5. Parameter guaranteed by design.

- A. Target values listed with alternative values in parentheses.

- B. tRFC must be less than or equal to tRC+1CLK tXSR must be less than or equal to tRC+1CLK

- 6. Required clocks are specified by JEDEC functionality and are not dependent on any timing parameter.

- 7. Timing actually specified by tDPL plus tRP; clock(s) specified as a reference only at minimum cycle rate

- 8. JEDEC and PC100 specify three clocks.

- 9. Timing actually specified by tCKs; clock(s) specified as a reference only at minimum cycle rate.

- 10. A new command can be given tRC after self refresh exit.

**Advance Information**

#### SPECIAL OPERATION FOR LOW POWER CONSUMPTION

#### **TEMPERATURE COMPENSATED SELF REFRESH**

Temperature Compensated Self Refresh allows the controller to program the Refresh interval during SELF REFRESH mode, according to the case temperature of the Low Power SDRAM device. This allows great power savings during SELF REFRESH during most operating temperature ranges. Only during extreme temperatures would the controller have to select a TCSR level that will guarantee data during SELF REFRESH. Every cell in the DRAM requires refreshing due to the capacitor losing its charge over time. The refresh rate is dependent on temperature. At higher temperatures a capacitor loses charge quicker than at lower temperatures, requiring the cells to be refreshed more often. Historically, during Self Refresh, the refresh rate has been set to accommodate the worst case, or highest temperature range expected.

Thus, during ambient temperatures, the power consumed during refresh was unnecessarily high, because the refresh rate was set to accommodate the higher temperatures. Setting E4 and E3, allow the DRAM to accommodate more specific temperature regions during SELF REFRESH. There are four temperature settings, which will vary the SELF REFRESH current according to the selected temperature. This selectable refresh rate will save power when the DRAM is operating at normal temperatures.

#### PARTIAL ARRAY SELF REFRESH

For further power savings during SELF REFRESH, the PASR feature allows the controller to select the amount of memory that will be refreshed during SELF REFRESH. The refresh options are Two Bank; all two banks, One Bank; bank a. WRITE and READ commands can still occur during standard operation, but only the selected banks will be refreshed during SELF REFRESH. Data in banks that are disabled will be lost.

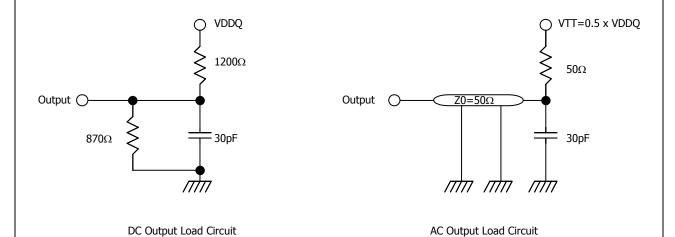

#### **DEEP POWER DOWN**

Deep Power Down is an operating mode to achieve maximum power reduction by eliminating the power of the whole memory array of the devices. Data will not be retained once the device enters Deep Power Down Mode. This mode is entered by having all banks idle then /CS and /WE held low with /RAS and /CAS held high at the rising edge of the clock, while CKE is low. This mode is exited by asserting CKE high.

## **Revision History**

| Revision | Date              | Change Description                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

|----------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Α        | November 18 2004  | Initial ADVANCE Release                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| В        | November 30 2004  | Changed Refresh Time to 4K / 64ms                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| С        | December 15 2004  | General Update. Added BGA package option                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| D        | February 16, 2005 | Changed Driver Strength control EMRS Table                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| E        | February 23, 2005 | Changed Pin Ordering (Page 2)<br>Changed Pin Name BA to A11                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| F        | March 1, 2005     | Removed 2/3 Reg Drive Strength (Page 1) Updated Extend Mode Register Diagram (Page 8) Modifed Pin Name Description (Page 10) Updated Command Truth Table (Burst Stop). Changed CKEn "X" to "H" (Page 12) Updated Partial Array Description. Changed Bank 0 to Bank a (Page 24) |  |  |  |  |  |  |  |  |

| G        | March 3, 2005     | Updated Mode Register and Extended Mode Register Diagram (Page 7, 8, 9, 24) Fixed Typo in Table 3 (Page 7) Updated Footnote #14(Page 16) Deleted tSRE from AC Timing Table and Footnote #10 (Page 22, 23)                                                                      |  |  |  |  |  |  |  |  |

| Н        | May 3, 2005       | Changed 48FBGA and 60WBGA package thickness to 1.0mm Max Added Pb-Free ordering option for 48FBGA package and 60WBGA package                                                                                                                                                   |  |  |  |  |  |  |  |  |

| I        | May 11, 2005      | Changed 48FBGA ordering option to Green instead of Pb-Free                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| J        | July 19, 2005     | Added 50-pin TSOP II package option                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| K        | August 15, 2005   | Updated AC/DC characteristics and added green TSOP II                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| L        | January 2006      | Designated green package to be RoHS Compliant                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

<sup>© 2004-2005</sup> Nanoamp Solutions, Inc. All rights reserved.

NanoAmp Solutions, Inc. ("NanoAmp") reserves the right to change or modify the information contained in this data sheet and the products described therein, without prior notice. NanoAmp does not convey any license under its patent rights nor the rights of others. Charts, drawings and schedules contained in this data sheet are provided for illustration purposes only and they vary depending upon specific applications.

NanoAmp makes no warranty or guarantee regarding suitability of these products for any particular purpose, nor does NanoAmp assume any liability arising out of the application or use of any product or circuit described herein. NanoAmp does not authorize use of its products as critical components in any application in which the failure of the NanoAmp product may be expected to result in significant injury or death, including life support systems and critical medical instrument.