Austin Semiconductor, Inc.

## 128K x 8 EEPROM

**Radiation Tolerant**

## AVAILABLE AS MILITARY SPECIFICATIONS

- Austin Semiconductor Space Level

- Austin Semiconductor Class 'B'

### FEATURES

- High speed: 250ns and 300ns

- Data Retention: 10 Years

- Low power dissipation, active current (20mW/MHz (TYP)), standby current (100µW(MAX))

- Single  $+3.3V \pm .3V$  power supply

- Data Polling and Ready/Busy Signals

- Erase/Write Endurance (10,000 cycles in a page mode)

- Software Data protection Algorithm

- Data Protection Circuitry during power on/off

- Hardware Data Protection with RES pin

- Automatic Programming: Automatic Page Write: 15ms (MAX) 128 Byte page size

### OPTIONS

### MARKINGS

| • Timing                       |       |         |

|--------------------------------|-------|---------|

| 250ns access                   | -25   | i       |

| 300ns access                   | -30   | )       |

| Packages                       |       |         |

| Ceramic Flat Pack              | F     | No. 306 |

| Radiation Shielded Ceramic FP* | SF    | No. 305 |

| Ceramic SOJ                    | DCJ   | No. 508 |

| Plastic SOP                    | DG    |         |

| Operating Temperature Ranges   |       |         |

| -Military (-55°C to +125°C)    |       | XT      |

| -Industrial (-40°C to +85°C)   |       | IT      |

|                                | 1 /17 |         |

**\*NOTE:** Package lid is connected to ground (Vss).

| PIN | ASS | SIGN | IME | INT |

|-----|-----|------|-----|-----|

|     |     |      |     |     |

(Top View)

#### 32-Pin CFP (F & SF), 32-Pin CSOJ (DCJ), 32-Pin SOP (DG)

|           | •  |    |       |

|-----------|----|----|-------|

| RDY/BUSY\ | 1  | 32 | Vcc   |

| A16       | 2  | 31 | A15   |

| A14       | 3  | 30 | RES\  |

| A12       | 4  | 29 | WE\   |

| A7        | 5  | 28 | A13   |

| A6        | 6  | 27 | A8    |

| A5        | 7  | 26 | A9    |

| A4        | 8  | 25 | A11   |

| A3        | 9  | 24 | OE\   |

| A2        | 10 | 23 | A10   |

| A1        | 11 | 22 | CE\   |

| A0        | 12 | 21 | I/O 7 |

| I/O 0     | 13 | 20 | I/O 6 |

| I/O 1     | 14 | 19 | I/O 5 |

| I/O 2     | 15 | 18 | I/O 4 |

| Vss       | 16 | 17 | I/O 3 |

|           |    |    |       |

|           |    |    |       |

### **GENERAL DESCRIPTION**

The Austin Semiconductor, Inc. AS58LC1001 is a 1 Megabit CMOS Electrically Erasable Programmable Read Only Memory (EEPROM) organized as 131, 072 x 8 bits. The AS58LC1001 is capable or in system electrical Byte and Page reprogrammability.

The AS58LC1001 achieves high speed access, low power consumption, and a high level of reliability by employing advanced MNOS memory technology and CMOS process and circuitry technology.

This device has a 128-Byte Page Programming function to make its erase and write operations faster. The AS58LC1001 features Data Polling and a Ready/Busy signal to indicate completion of erase and programming operations.

This EEPROM provides several levels of data protection. Hardware data protection is provided with the RES pin, in addition to noise protection on the WE signal and write inhibit during power on and off. Software data protection is implemented using JEDEC Optional Standard algorithm.

The AS58LC1001 is designed for high reliability in the most demanding applications. Data retention is specified for 10 years and erase/write endurance is guaranteed to a minimum of 10,000 cycles in the Page Mode.

For more products and information please visit our web site at www.austinsemiconductor.com

Austin Semiconductor, Inc.

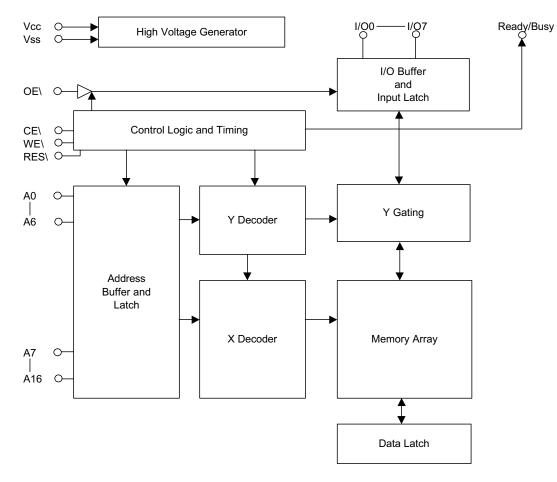

## FUNCTIONAL BLOCK DIAGRAM

### **MODE SELECTION**

| MODE            | CE/             | OE\             | WE\             | RES\            | RDY/BUSY\       | I/O                |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|--------------------|

| READ            | V <sub>IL</sub> | $V_{IL}$        | $V_{\rm IH}$    | V <sub>H</sub>  | High-Z          | D <sub>OUT</sub>   |

| STANDBY         | V <sub>IH</sub> | Х               | Х               | Х               | High-Z          | High-Z             |

| WRITE           | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>H</sub>  | High-Z          | D <sub>IN</sub>    |

| DESELECT        | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>H</sub>  | High-Z          | High-Z             |

| WRITE           | х               | Х               | V <sub>IH</sub> | х               |                 |                    |

| INHIBIT         | Х               | V <sub>IL</sub> | Х               | Х               |                 |                    |

| DATA<br>POLLING | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>H</sub>  | V <sub>OL</sub> | Data Out<br>(I/O7) |

| PROGRAM         | Х               | Х               | Х               | V <sub>IL</sub> | High-Z          | High-Z             |

### FUNCTIONAL DESCRIPTION

USTIN

#### AUTOMATIC PAGE WRITE

The Page Write feature allows 1 to 128 Bytes of data to be written into the EEPROM in a single cycle and allows the undefined data within 128 Bytes to be written corresponding to the undefined address ( $A_0$  to  $A_6$ ). Loading the first Byte of data, the data load window of 30µs opens for the second. In the same manner each additional Byte of data can be loaded within 30µs. In case CE\ and WE\ are kept high for 100µs after data input, the EEPROM enters erase and write automatically and only the input data can be written into the EEPROM. In Page mode the data can be written and accessed 10<sup>4</sup> times per page, and in Byte mode 10<sup>3</sup> times per Byte.

### **DATA\ POLLING**

Data\Polling allows the status of the EEPROM to be determined. If the EEPROM is set to Read mode during a Write cycle, and inversion of the last Byte of data to be loaded outputs from I/O, to indicate that the EEPROM is performing a Write operation.

### WRITE PROTECTION

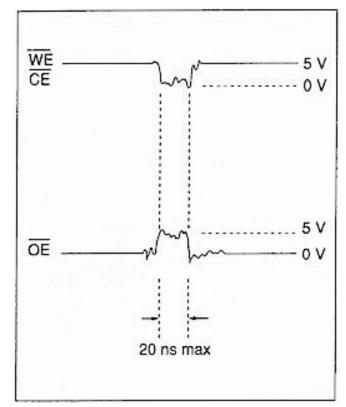

- (1) Noise protection: Noise on a write cycle will not act as a trigger with a WE\ pulse of less than 20ns.

- (2) Write inhibit: Holding OE\low, WE\high or CE\high, inhibits a write cycle during power on/off.

### WE\ AND CE\ PIN OPERATION

During a write cycle, addresses are latched by the falling edge of WE\ or CE\, and data is latched by the rising edge of WE\ or CE\.

## WRITE/ERASE ENDURANCE AND DATA RETENTION

The endurance with page programming is  $10^4$  cycles (1% cumulative failure rate) and the data retention time is more than 10 years when a device is programmed less than  $10^4$  cycles.

### DATA PROTECTION

To protect the data during operation and power on/off, the AS58C1001 has:

1. Data protection against Noise on Control Pins (CE\, OE\, WE\) during Operation. During readout or standby, noise on the control pins may act as a trigger and turn the EEPROM to programming mode by mistake. To prevent this phenomenon, the AS58LC1001 has a noise cancellation function that cuts noise if its width is 20ns or less in programming mode. Be careful not to allow noise of a width of more than 20ns on the control pins.

Austin Semiconductor, Inc.

### **FUNCTIONAL DESCRIPTION (continued)**

### **DATA PROTECTION (continued)**

USTIN

Semiconductor

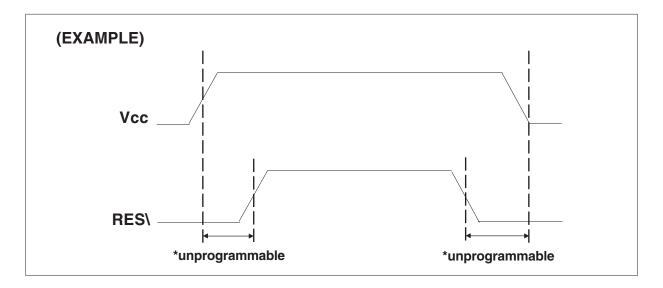

2. Data protection at Vcc on/off.

When RES\ is low, the EEPROM cannot be erased and programmed. Therefore, data can be protected by keeping RES\ low when Vcc is switched. RES\ should be high during programming because it does not provide a latch function. When Vcc is turned on or off, noise on the control pins generated by external circuits (CPU, etc.) may turn the EEPROM to programming mode by mistake. To prevent this unintentional programming, the EEPROM must be kept in an unprogrammable, standby or readout state by using a CPU reset signal to RES\ pin.

In addition, when RES\ is kept high at Vcc on/off timing, the input level of control pins (CE\, OE\, WE\) must be held as CE\=Vcc or OE\=LOW or WE\=Vcc level.

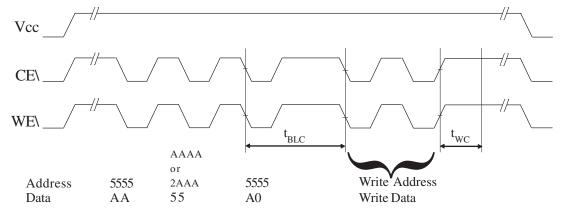

#### 3. Software Data Protection

To protect against unintentional programming caused by noise generated by external circuits, AS58LC1001 has a Software data protection function. To initate Software data protection mode, 3 bytes of data must be input, followed by a dummy write cycle of any address and any data byte. This exact sequence switches the device into protection mode.

| Write Address    | Write Data<br>(Normal Data Input) |

|------------------|-----------------------------------|

| 5555             | AA                                |

| <b>↓</b><br>2AAA | <b>★</b><br>55                    |

| ↓                | ¥                                 |

| 5555             | A0                                |

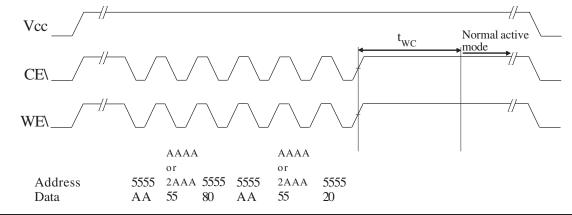

The Software data protection mode can be cancelled by inputting the following 6 Bytes. This changes the AS58LC1001 to the Non-Protection mode, for normal operation.

| Address | Data |

|---------|------|

| 5555    | AA   |

| ¥       | ¥    |

| 2AAA    | 55   |

| ¥       | ¥    |

| 5555    | 80   |

| ¥       | ↓    |

| 5555    | AA   |

| ¥       | ↓    |

| 2AAA    | 55   |

| ¥       | ¥    |

| 5555    | 20   |

### Austin Semiconductor, Inc.

### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on Vcc Supply Relative to Vss | $0.5V$ to $+7.0V^{1}$            |

|---------------------------------------|----------------------------------|

| Voltage on any pin Relative to Vss    | 0.6V to +7.0V <sup>1</sup>       |

| Storage Temperature                   | $65^{\circ}C$ to $+150^{\circ}C$ |

| Operating Temperature Range           | -55°C to +125°C                  |

| Soldering Temperature Range           |                                  |

| Maximum Junction Temperature**        | +150°C                           |

| Power Dissipation                     | 1.0W                             |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

\*\* Junction temperature depends upon package type, cycle time, loading, ambient temperature and airflow.

## ELECTRICAL CHARACTERISTICS AND RECOMMENDED DC OPERATING CONDITIONS (-55°C $\leq T_{a} \leq 125$ °C; Vcc = 3.3V ±.3V)

| PARAMETER                                | CONDITION                                      | SYMBOL          | MIN     | MAX                    | UNITS | NOTES |

|------------------------------------------|------------------------------------------------|-----------------|---------|------------------------|-------|-------|

| Input High (Logic 1) Voltage             |                                                | V <sub>IH</sub> | 2.2     | V <sub>CC</sub> + 0.3V | V     | 9     |

| Input Low (Logic 0) Voltage <sup>3</sup> |                                                | VIL             | -0.3    | 0.8                    | V     | 2     |

| Input Voltage (RES\ Pin)                 |                                                | V <sub>H</sub>  | Vcc-0.5 | V <sub>CC</sub> +1.0   | V     |       |

| Input Leakage Current <sup>4</sup>       | OV <u>&lt;</u> V <sub>IN</sub> <u>&lt;</u> Vcc | I <sub>LI</sub> | -2      | 2                      | μΑ    | 4     |

| Output Leakage Current                   | Output(s) disabled, $OV \leq V_{OUT} \leq Vcc$ | I <sub>LO</sub> | -2      | 2                      | μΑ    |       |

| Output High Voltage                      | I <sub>OH</sub> = -400 μA                      | V <sub>OH</sub> | 2.4     |                        | V     |       |

| Output Low Voltage                       | I <sub>OL</sub> = 2.1 mA                       | V <sub>OL</sub> |         | 0.5                    | V     |       |

|                                                                                                                                        |                                  |                  |     | MAX |     | 1     |       |

|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------|-----|-----|-----|-------|-------|

| PARAMETER                                                                                                                              | CONDITIONS                       | SYM              | -25 | -30 | -35 | UNITS | NOTES |

| Power Supply Current:<br>Operating $I_{OUT}=OmA, Vcc = 3.6V$ Cycle=1 $\mu$ S, Duty=100% $I_{OUT}=OmA, Vcc = 3.6V$ Cycle=MIN, Duty=100% |                                  | 8                | 8   | 8   | mA  |       |       |

|                                                                                                                                        |                                  | ICC3             | 20  | 20  | 20  | mA    |       |

| Power Supply Current:                                                                                                                  | CE\=Vcc, Vcc = 3.6V              | I <sub>CC1</sub> | 100 | 100 | 100 | μA    |       |

| Standby                                                                                                                                | CE\=V <sub>IH</sub> , Vcc = 3.6V | I <sub>CC2</sub> | 1.5 | 1.5 | 1.5 | mA    |       |

### CAPACITANCE

| PARAMETER          | CONDITIONS                      | SYMBOL          | MAX | UNITS | NOTES |

|--------------------|---------------------------------|-----------------|-----|-------|-------|

| Input Capacitance  | T <sub>A</sub> = 25°C, f = 1MHz | C <sub>IN</sub> | 6   | pF    |       |

| Output Capactiance | $V_{IN} = 0$                    | Co              | 12  | pF    |       |

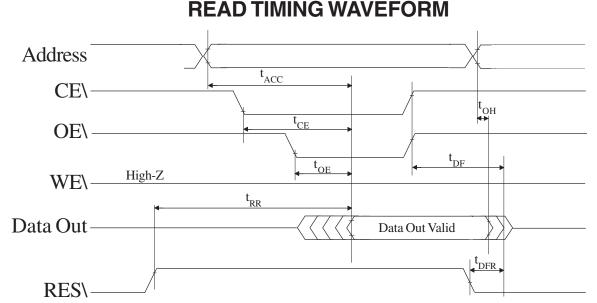

# AC ELECTRICAL CHARACTERISTICS FOR READ OPERATION (-55°C $\leq T_c \leq 125$ °C; Vcc = 5V $\pm$ .3V)

**Test Conditions**

- Input Pulse Levels: 0.0V to

- 0.0V to 3.0V < 20ns

1.5V, 1.5V

- Input rise and fall times:

- Output Load:

- Reference levels for measuring timing:

| ITEM DESCRIPTION              | TEST CONDITION                              | SYMBOL           | -25 |     | -30 |     | UNITS |

|-------------------------------|---------------------------------------------|------------------|-----|-----|-----|-----|-------|

| TIEW DESCRIPTION              | TEST CONDITION                              | STWBOL           | MIN | MAX | MIN | MAX | UNITS |

| Address Access Time           | CE\=OE\=V <sub>IL</sub> WE\=V <sub>IH</sub> | t <sub>ACC</sub> |     | 250 |     | 300 | ns    |

| Chip Enable Access Time       | OE\=V <sub>IL</sub> WE\=V <sub>IH</sub>     | t <sub>CE</sub>  |     | 250 |     | 300 | ns    |

| Output Enable Acess Time      | CE\=V <sub>IL</sub> WE\=V <sub>IH</sub>     | t <sub>OE</sub>  | 10  | 120 | 10  | 130 | ns    |

| Output Hold to Address Change | CE\=OE\=V <sub>IL</sub> WE\=V <sub>IH</sub> | t <sub>OH</sub>  | 0   |     | 0   |     | ns    |

|                               | CE\=V <sub>IL</sub> WE\=V <sub>IH</sub>     | t <sub>DF</sub>  | 0   | 75  | 0   | 75  | ns    |

| Output Disable to High-Z      | CE\=OE\=V <sub>IL</sub> WE\=V <sub>IH</sub> | t <sub>DFR</sub> | 0   | 350 | 0   | 350 | ns    |

| RES\ to Output Delay          | CE\=OE\=V <sub>IL</sub> WE\=V <sub>IH</sub> | t <sub>RR</sub>  | 0   | 600 | 0   | 600 | ns    |

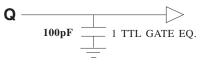

1 TTL Gate +100pF (including scope and jig)

## AC ELECTRICAL CHARACTERISTICS FOR SOFTWARE DATA PROTECTION CYCLE OPERATION

| PARAMETER            | SYMBOL           | MIN | MAX | UNITS |

|----------------------|------------------|-----|-----|-------|

| Byte Load Cycle Time | t <sub>BLC</sub> | 1.0 | 30  | μS    |

| Write Cycle Time     | t <sub>WC</sub>  | 15  |     | mS    |

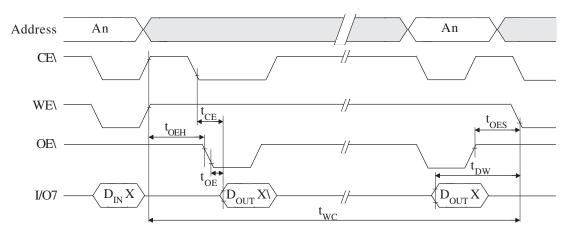

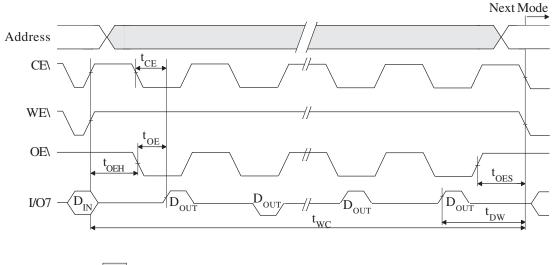

### AC ELECTRICAL CHARACTERISTICS FOR DATA\ POLLING OPERATION

| PARAMETER                         | SYMBOL           | MIN | MAX | UNITS |

|-----------------------------------|------------------|-----|-----|-------|

| Output Enable Hold Time           | t <sub>OEH</sub> | 0   |     | ns    |

| Output Enable to Write Setup Time | t <sub>OES</sub> | 0   |     | ns    |

| Write Start Time                  | t <sub>DW</sub>  | 250 |     | ns    |

| Write Cycle Time                  | t <sub>WC</sub>  |     | 15  | ms    |

EEPROM

AS58LC1001

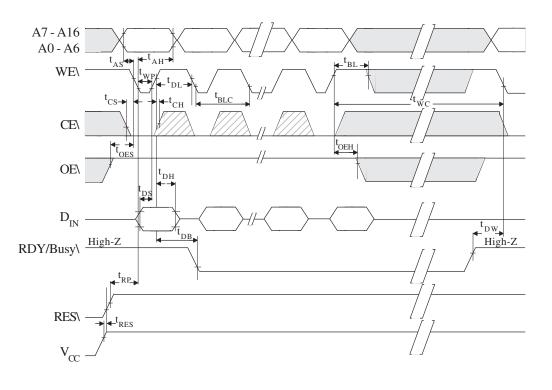

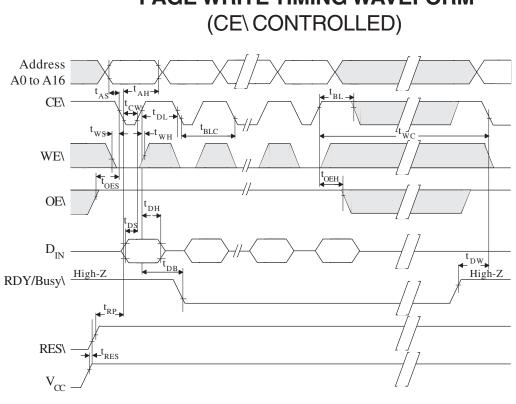

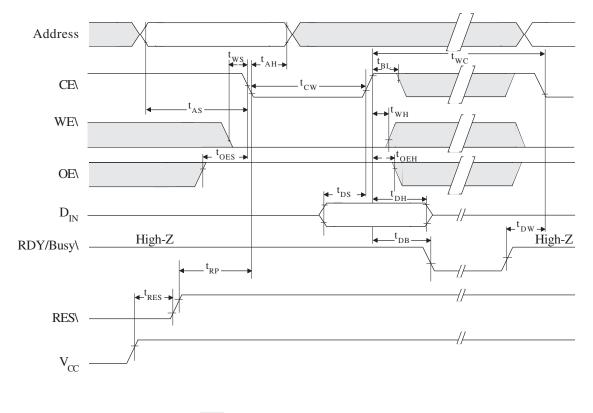

# AC ELECTRICAL CHARACTERISTICS FOR PAGE ERASE AND PAGE WRITE OPERATIONS

| PARAMETER                        | SYMBOL                         | MIN  | MAX | UNITS |

|----------------------------------|--------------------------------|------|-----|-------|

| Address Setup Time               | t <sub>AS</sub>                | 0    |     | ns    |

| Write Enable to Write Setup Time | t <sub>WS</sub> <sup>8</sup>   | 0    |     | ns    |

| Chip Enable to Write Setup Time  | t <sub>cs</sub> <sup>7</sup>   | 0    |     | ns    |

| Write Pulse Width                | t <sub>WP</sub> <sup>7</sup>   | 250  |     | ns    |

|                                  | t <sub>CW</sub> 9              | 250  |     | ns    |

| Address Hold Time                | t <sub>AH</sub>                | 150  |     | ns    |

| Data Setup Time                  | t <sub>DS</sub>                | 100  |     | ns    |

| Data Hold Time                   | t <sub>DH</sub>                | 10   |     | ns    |

| Write Enable Hold Time           | t <sub>WH</sub> <sup>8</sup>   | 0    |     | ns    |

| Chip Enable Hold Time            | t <sub>CH</sub> <sup>7</sup>   | 0    |     | ns    |

| Out Enable to Write Setup Time   | t <sub>OES</sub>               | 0    |     | ns    |

| Output Enable Hold Time          | t <sub>OEH</sub>               | 0    |     | ns    |

| Data Latch Time                  | t <sub>DL</sub>                | 200  |     | ns    |

| Write Cycle Time                 | t <sub>WC</sub>                | 10   |     | ms    |

| Byte Load Window                 | t <sub>BL</sub>                | 100  |     | μs    |

| Byte Load Cycle                  | t <sub>BLC</sub>               | 0.55 | 30  | μs    |

| Time to Device Busy              | t <sub>DB</sub>                | 120  |     | ns    |

| RES\ to Write Setup Time         | t <sub>RP</sub>                | 100  |     | μs    |

| Vcc to RES\ Setup Time           | t <sub>RES</sub> <sup>11</sup> | 1    |     | μs    |

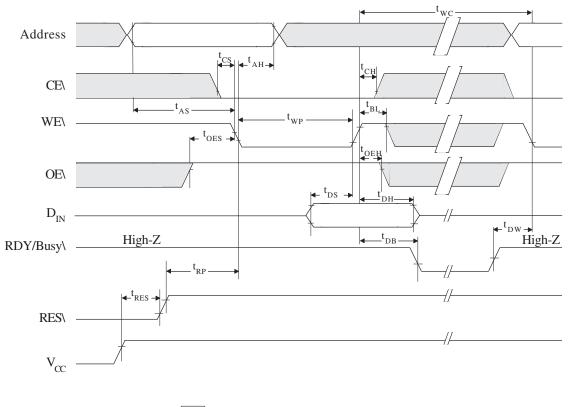

# AC ELECTRICAL CHARACTERISTICS FOR BYTE ERASE AND BYTE WRITE OPERATIONS

| PARAMETER                       | SYMBOL                         | MIN | MAX | UNITS |

|---------------------------------|--------------------------------|-----|-----|-------|

| Address Setup Time              | t <sub>AS</sub>                | 0   |     | ns    |

| Chip Enable to Write Setup Time | t <sub>CS</sub> <sup>7</sup>   | 0   |     | ns    |

| Write Pulse Width               | t <sub>CW</sub> <sup>8</sup>   | 250 |     | ns    |

|                                 | t <sub>WP</sub> <sup>7</sup>   | 250 |     | ns    |

| Address Hold Time               | t <sub>AH</sub>                | 150 |     | ns    |

| Data Setup Time                 | t <sub>DS</sub>                | 100 |     | ns    |

| Data Hold Time                  | t <sub>DH</sub>                | 10  |     | ns    |

| Chip Enable Hold Time           | t <sub>CH</sub> <sup>7</sup>   | 0   |     | ns    |

| Out Enable to Write Setup Time  | t <sub>OES</sub>               | 0   |     | ns    |

| Output Enable Hold Time         | t <sub>OEH</sub>               | 0   |     | ns    |

| Write Cycle Time                | t <sub>WC</sub>                | 10  |     | ms    |

| Byte Load Window                | t <sub>BL</sub>                | 100 |     | μs    |

| Time to Device Busy             | t <sub>DB</sub>                | 120 |     | ns    |

| RES\ to Write Setup Time        | t <sub>RP</sub>                | 100 |     | μs    |

| Vcc to RES\ Setup Time          | t <sub>RES</sub> <sup>10</sup> | 1   |     | μs    |

### **AC TEST CONDITIONS**

| Input Pulse Levels           | 0V to 3V     |

|------------------------------|--------------|

| Input Rise and Fall Times    | ≤20ns        |

| Input Timing Reference Level | 1.5V         |

| Output Reference Level       | 1.5V         |

| Output Load                  | See Figure 1 |

Figure 1 OUTPUT LOAD EQUIVALENT

### NOTES:

- 1. Relative to Vss

- 2.  $V_{IN} min = -3.0V$  for pulse widths  $\leq 50$ ns

- 3.  $V_{IL}$  min = -1.0V for pulse widths  $\leq$ 50ns

- 4.  $I_{II}$  on RES\ = 100ua MAX

- 5. t<sub>OF</sub> is defined as the time at which E the output becomes and open circuit and data is no longer driven.

- 6. Use this device in longer cycle than this value

- 7. WE\ controlled operation

- 8. CE\ controlled operation

- 9. RES\ pin  $V_{IH}$  is  $V_{H}$

- 10. Reference only, not tested

**READ TIMING WAVEFORM**

SOFTWARE DATA PROTECTION TIMING WAVEFORM (protection mode)

SOFTWARE DATA PROTECTION TIMING WAVEFORM (non-protection mode)

## DATA\ POLLING TIMING WAVEFORM

## **TOGGLE BIT WAVEFORM**

In transition from HI to LOW or LOW to HI.

**USTIN**

**SEMICONDUCTOR**

Austin Semiconductor, Inc.

## PAGE WRITE TIMING WAVEFORM (WE\CONTROLLED)

PAGE WRITE TIMING WAVEFORM

USTIN

**SEMICONDUCTOR**

## BYTE WRITE TIMING WAVEFORM (WE\CONTROLLED)

Austin Semiconductor, Inc.

## BYTE WRITE TIMING WAVEFORM (CE\CONTROLLED)

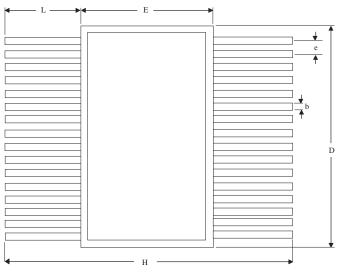

## **MECHANICAL DEFINITIONS\***

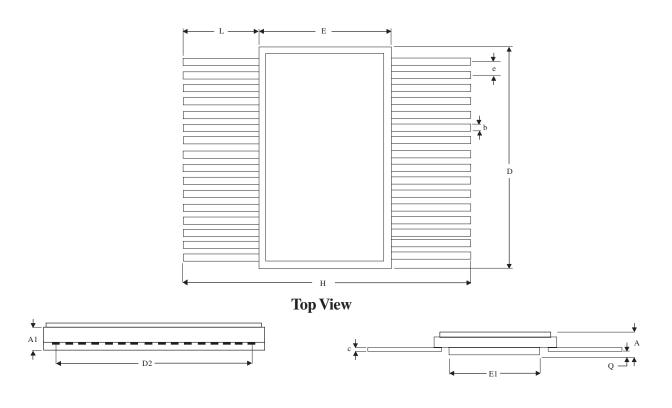

ASI Case #305 (Package Designator SF) SMD 5962-38267, Case Outline N

USTIN

**SEMICONDUCTOR**

|        | SMD SPECIFICATIONS |       |  |

|--------|--------------------|-------|--|

| SYMBOL | MIN                | MAX   |  |

| A      | 0.125              | 0.150 |  |

| A1     | 0.090              | 0.110 |  |

| b      | 0.015              | 0.019 |  |

| С      | 0.003              | 0.007 |  |

| D      | 0.810              | 0.830 |  |

| D1     | 0.775              | 0.785 |  |

| D2     | 0.745              | 0.755 |  |

| E      | 0.425              | 0.445 |  |

| E1     | 0.290              | 0.310 |  |

| е      | 0.045              | 0.055 |  |

| Н      | 1.000              | 1.100 |  |

| L      | 0.290              | 0.310 |  |

| Q      | 0.026              | 0.037 |  |

\*All measurements are in inches.

## **MECHANICAL DEFINITIONS\***

### ASI Case #306 (Package Designator F) SMD 5962-38267, Case Outline M

|        | SMD SPECIFICATIONS |       |  |

|--------|--------------------|-------|--|

| SYMBOL | MIN                | MAX   |  |

| A      | 0.097              | 0.123 |  |

| A1     | 0.090              | 0.110 |  |

| b      | 0.015              | 0.019 |  |

| С      | 0.003              | 0.007 |  |

| D      | 0.810              | 0.830 |  |

| D2     | 0.745              | 0.755 |  |

| E      | 0.425              | 0.445 |  |

| E1     | 0.330              | 0.356 |  |

| е      | 0.045              | 0.055 |  |

| Н      | 1.000              | 1.100 |  |

| L      | 0.290              | 0.310 |  |

| Q      | 0.026              | 0.037 |  |

**NOTE:** All drawings are per the SMD. ASI's package dimensional limits may differ, but they will be within the SMD limits.

**USTIN**

**SEMICONDUCTOR**

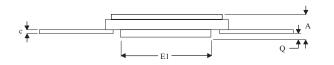

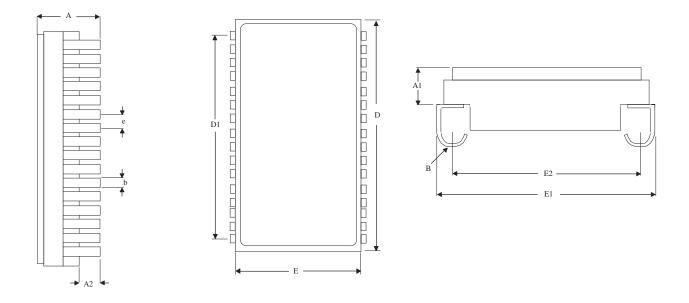

## **MECHANICAL DEFINITIONS\***

ASI Case #508 (Package Designator DCJ)

|        | ASI PACKAGE SPECIFICATIONS |       |  |

|--------|----------------------------|-------|--|

| SYMBOL | MIN                        | МАХ   |  |

| A      | 0.132                      | 0.142 |  |

| A1     | 0.076                      | 0.086 |  |

| A2     | 0.018                      | 0.028 |  |

| В      | 0.018                      | 0.032 |  |

| b      | 0.015                      | 0.019 |  |

| D      | 0.816                      | 0.834 |  |

| D1     | 0.745                      | 0.755 |  |

| E      | 0.430                      | 0.440 |  |

| E1     | 0.465                      | 0.485 |  |

| E2     | 0.415                      | 0.425 |  |

| е      | 0.045                      | 0.055 |  |

#### \*All measurements are in inches.

EEPROM AS58LC1001

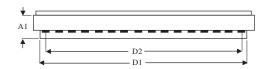

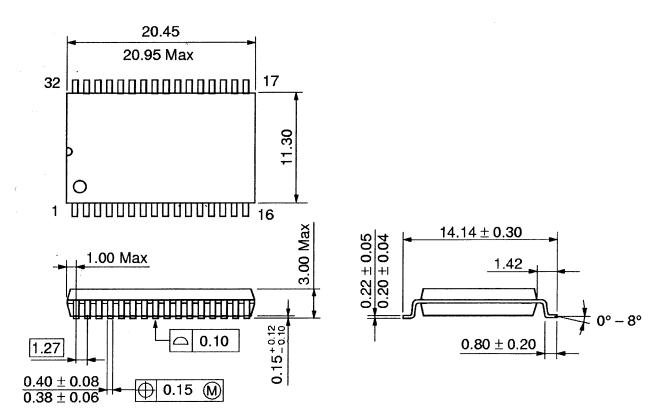

## **MECHANICAL DEFINITIONS\***

ASI Case (Package Designator DG)

**USTIN**

**SEMICONDUCTOR**

Austin Semiconductor, Inc.

## **ORDERING INFORMATION**

EXAMPLE: AS58LC1001SF-15/IT

USTIN

Semiconductor

| Device Number | Package<br>Type | Speed<br>ns | Process |

|---------------|-----------------|-------------|---------|

| AS58LC1001    | SF              | -25         | /*      |

| AS58LC1001    | SF              | -30         | /*      |

### EXAMPLE: AS58LC1001F-25/883C

| Device Number | Package<br>Type | Speed<br>ns | Process |

|---------------|-----------------|-------------|---------|

| AS58LC1001    | F               | -25         | /*      |

| AS58LC1001    | F               | -30         | /*      |

### EXAMPLE: AS58LC1001DG-15/XT \*\*

| Device Number | Package<br>Type | Speed<br>ns | Process |

|---------------|-----------------|-------------|---------|

| AS58LC1001    | DG              | -25         | /*      |

| AS58LC1001    | DG              | -30         | /*      |

### EXAMPLE: AS58LC1001DCJ-20/IT

| Device Number | Package<br>Type | Speed<br>ns | Process |

|---------------|-----------------|-------------|---------|

| AS58LC1001    | DCJ             | -25         | /*      |

| AS58LC1001    | DCJ             | -30         | /*      |

### **\*AVAILABLE PROCESSES**

| IT = Industrial Temperature Range | -40°C to +85°C  |

|-----------------------------------|-----------------|

| XT = Extended Temperature Range   | -55°C to +125°C |

| 883C = Full Military Processing   | -55°C to +125°C |

**\*\*NOTE:** DG package available as XT and IT only.

## **ASI TO DSCC PART NUMBER CROSS REFERENCE\***

**Package Designator F**

**ASI Part #**

SMD Part#

AS58C1001F-25/883C AS58C1001F-20/883C AS58C1001F-15/883C

USTIN

**Semiconductor**

5962-3826716QMA 5962-3826717QMA 5962-3826718QMA EEPROM

AS58LC1001

### **Package Designator SF**

ASI Part #

### SMD Part#

AS58C1001SF-25/883C AS58C1001SF-20/883C AS58C1001SF-15/883C

5962-3826716ONA 5962-3826717QNA 5962-3826718QNA

Package Designators DCJ and DG not currenly available on the SMD.

\* ASI part number is for reference only. Orders received referencing the SMD part number will be processed per the SMD.

### DOCUMENT TITLE

128K x 8 EEPROM Radiation Tolerant

### Rev # History

1.0 Removed ECA Package

Release Date December 2008 <u>Status</u> Release