#### AAT1164/AAT1164B/AAT1164C

Product information presented is current as of publication date. Details are subject to change without notice.

# TRIPLE-CHANNEL TFT LCD POWER SOLUTION WITH OPERATIONAL AMPLIFIERS

### **FEATURES**

- Built in 3A, 0.2Ω Switching NMOS

- Positive LDO Driver Up to 28V/5mA

- Negative LDO Driver Down to -14V/5mA

- 1 V<sub>COM</sub> and 4 V<sub>GAMMA</sub> Operational Amplifiers

- 28V High Voltage Switch for VGH

- Internal Soft-Start Function

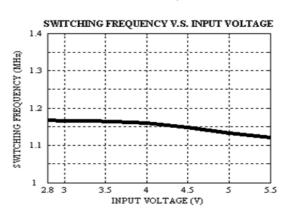

- 1.2MHz Fixed Switching Frequency

- 3 Channels Fault and Thermal Protection

- Low Dissipation Current

- QFN-32 Package Available

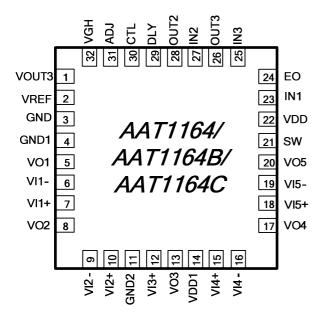

## **PIN CONFIGURATION**

### **GENERAL DESCRIPTION**

The AAT1164/AAT1164B/AAT1164C is a triple-channel TFT LCD power solution that provides a step-up PWM controller, two high voltage LDO drivers (one for positive voltage and one for negative voltage), five operational amplifiers, and one high voltage switch up to 28V for TFT LCD display.

The PWM controller consists of an on-chip voltage reference, oscillator, error amplifier, current sense circuit, comparator, under-voltage lockout protection and internal soft-start circuit. The thermal and power fault protection prevents internal circuit being damaged by excessive power.

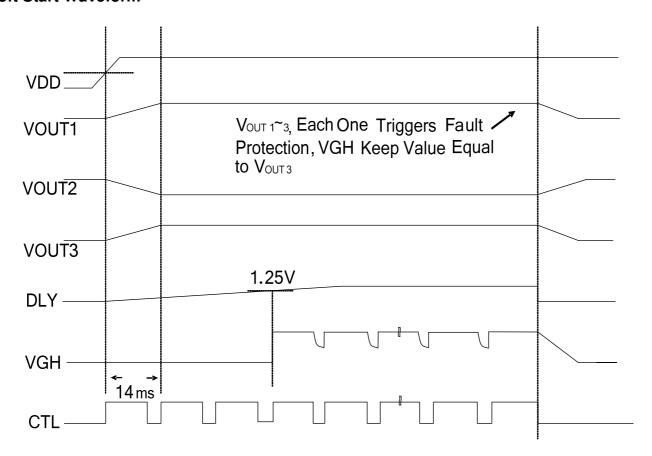

The high voltage LDO drivers generate two regulated output voltage ( $V_{\text{OUT2}}$  and  $V_{\text{OUT3}}$ ) set by external resistor dividers. VGH voltage does not activate until DLY voltage exceeds 1.25V.

The AAT1164/AAT1164B/AAT1164C contains 4+1 operational amplifiers. VO1, VO2, VO4, and VO5 are for gamma corrections and VO3 is for  $V_{\text{COM}}$ . In the short circuit condition, operational amplifiers are capable of sourcing  $\pm 100 \text{mA}$  current for  $V_{\text{GAMMA}}$ , and  $\pm 200 \text{mA}$  current for  $V_{\text{COM}}$ .

With the minimal external components, the AAT1164/AAT1164B/AAT1164C offers a simple and economical solution for TFT LCD power.

## **ORDERING INFORMATION**

| DEVICE<br>TYPE | PART NUMBER   | PACKAGE           | PACKING             | TEMP.<br>RANGE   | MARKING                   | MARKING<br>DESCRIPTION                                       |

|----------------|---------------|-------------------|---------------------|------------------|---------------------------|--------------------------------------------------------------|

| AAT1164        | AAT1164-Q5-T  | Q5:VQFN<br>32-5*5 | T: Tape<br>and Reel | –40 °C to +85 °C | AAT1164<br>XXXXX<br>XXXX  | 1. Part Name 2. Lot No. (6~9 Digits) 3. Date Code (4 Digits) |

| AAT1164B       | AAT1164B-Q5-T | Q5:VQFN<br>32-5*5 | T: Tape<br>and Reel | –40 °C to +85 °C | AAT1164B<br>XXXXX<br>XXXX | 1. Part Name 2. Lot No. (6~9 Digits) 3. Date Code (4 Digits) |

| AAT1164C       | AAT1164C-Q5-T | Q5:VQFN<br>32-5*5 | T: Tape<br>and Reel | –40 °C to +85 °C | AAT1164C<br>XXXXX<br>XXXX | 1. Part Name 2. Lot No. (6~9 Digits) 3. Date Code (4 Digits) |

NOTE: All AAT products are lead free and halogen free.

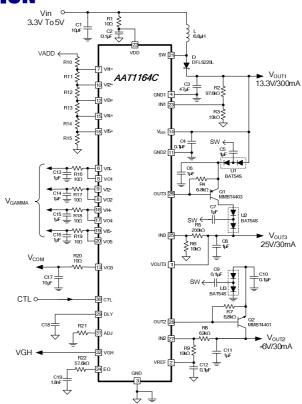

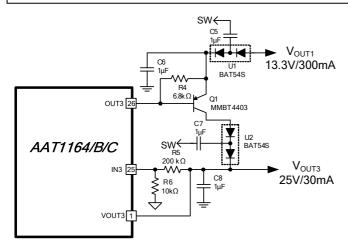

## **TYPICAL APPLICATION**

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 1.00

Page 2 of 24

April 2007

## **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                                                                    | SYMBOL               | VALUE                | UNIT |

|------------------------------------------------------------------------------|----------------------|----------------------|------|

| VDD to GND                                                                   | $V_{DD}$             | 7                    | V    |

| VDD1, SW to GND (for AAT1164/AAT1164B)                                       | V <sub>H1</sub>      | 13.5                 | V    |

| VDD1, SW to GND (for AAT1164C)                                               | V <sub>H1</sub>      | 14.5                 | V    |

| VOUT3, OUT3, VGH to GND                                                      | $V_{H2}$             | 30                   | V    |

| OUT2 to GND                                                                  | V <sub>H3</sub>      | -14                  | V    |

| Input Voltage 1 (IN1, IN2, IN3, DLY, CTL,)                                   | V <sub>I1</sub>      | V <sub>DD</sub> +0.3 | V    |

| Input Voltage 2 (VI1+, VI1-, VI2+, VI2-, VI3+, VI3-, VI4+, VI4-, VI5+, VI5-) | V <sub>I2</sub>      | V <sub>H1</sub> +0.3 | V    |

| Output Voltage 1 (EO, V <sub>REF</sub> )                                     | V <sub>O1</sub>      | V <sub>DD</sub> +0.3 | V    |

| Output Voltage 2 (ADJ, VO1, VO2, VO3, VO4, VO5)                              | V <sub>O2</sub>      | V <sub>H1</sub> +0.3 | V    |

| Operating Free-Air Temperature Range                                         | T <sub>C</sub>       | –40 °C to +85 °C     | °C   |

| Storage Temperature Range                                                    | T <sub>STORAGE</sub> | –45 °C to +125 °C    | °C   |

| Power Dissipation                                                            | $P_d$                | 1,600                | mW   |

Note: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended period of time may affect device reliability.

## **AAT1164/AAT1164B/AAT1164C**

## **ELECTRICAL CHARACTERISTICS**

$(V_{DD}=2.6V \text{ to } 5.5V, T_C=-40\,^{\circ}\text{C to } 85\,^{\circ}\text{C}$ , unless otherwise specified. Typical values are tested at 25  $^{\circ}\text{C}$  ambient temperature,  $V_{DD}=3.3V, V_{DD1}=10V.)$

| PARAMETER                 | SYMBOL            | TEST CONDITION                         | MIN | TYP  | MAX  | UNIT |

|---------------------------|-------------------|----------------------------------------|-----|------|------|------|

| VDD Input Voltage Range   | $V_{DD}$          |                                        | 2.6 |      | 5.5  | ٧    |

| VDD1 Input Voltage Range  | $V_{DD1}$         | AAT1164/AAT1164B                       | 8   |      | 13   | V    |

| VDD1 input voltage hange  | V DD1             | AAT1164C                               | 8   |      | 14   | V    |

| VDD Under Voltage Lockout | V                 | Falling                                | 2.1 | 2.2  | 2.3  | V    |

|                           | $V_{\text{UVLO}}$ | Rising                                 | 2.3 | 2.4  | 2.5  | V    |

| VDD Operating Current     | 1                 | V <sub>IN1</sub> = 1.5V, Not Switching |     | 0.56 | 0.80 | mA   |

| VDD Operating Current     | $I_{VDD}$         | V <sub>IN1</sub> = 1.0V, Switching     |     | 5.6  | 10.0 | mA   |

| VDD1 Operating Current    | I <sub>VDD1</sub> | $V_{V11+} \sim V_{V15+} = 4V$          |     | 7    | 10   | mA   |

| Thermal Shutdown          | T <sub>SHDN</sub> |                                        |     | 160  |      | °C   |

#### **Reference Voltage**

| <u>,</u>          |           |                                                           |       |       |       |      |

|-------------------|-----------|-----------------------------------------------------------|-------|-------|-------|------|

| PARAMETER         | SYMBOL    | TEST CONDITION                                            | MIN   | TYP   | MAX   | UNIT |

| Reference Voltage | $V_{REF}$ | $I_{V_{REF}} = 100 \mu A$                                 | 1.231 | 1.250 | 1.269 | V    |

| Line Regulation   |           | $I_{V_{REF}} = 100 \mu A,$<br>$V_{DD} = 2.6 V \sim 5.5 V$ | -     | 2     | 5     | %/mV |

| Load Regulation   |           | I <sub>VREF</sub> = 0~100μA                               | -     | 1     | 5     | %/mA |

#### **Oscillator**

| PARAMETER             | SYMBOL           | TEST CONDITION | MIN  | TYP  | MAX  | UNIT |

|-----------------------|------------------|----------------|------|------|------|------|

| Oscillation Frequency | f <sub>OSC</sub> |                | 1.05 | 1.20 | 1.35 | MHz  |

| Maximum Duty Cycle    | $D_{MAX}$        |                | 84   | 87   | 90   | %    |

## **AAT1164/AAT1164B/AAT1164C**

## **ELECTRICAL CHARACTERISTICS**

$(V_{DD}=2.6V \text{ to } 5.5V, T_C=-40\,^{\circ}\text{C to } 85\,^{\circ}\text{C}$ , unless otherwise specified. Typical values are tested at 25  $^{\circ}\text{C}$  ambient temperature,  $V_{DD}=3.3V, V_{DD1}=10V.)$

#### **Soft Start & Fault Detect**

| PARAMETER                         | SYMBOL           | TEST CONDITION | MIN  | TYP  | MAX  | UNIT |

|-----------------------------------|------------------|----------------|------|------|------|------|

| Channel 1 Soft Start Time         | t <sub>SS1</sub> |                |      | 14   |      | ms   |

| Channel 2 Soft Start Time         | t <sub>SS2</sub> |                |      | 14   |      | ms   |

| Channel 3 Soft Start Time         | t <sub>SS3</sub> |                |      | 14   |      | ms   |

| During Fault Protect Trigger Time | t <sub>FP</sub>  |                |      | 55   |      | ms   |

| IN1 Fault Protection Voltage      | $V_{F1}$         |                | 1.00 | 1.05 | 1.10 | ٧    |

| IN2 Fault Protection Voltage      | $V_{F2}$         |                | 0.40 | 0.45 | 0.50 | ٧    |

| IN3 Fault Protection Voltage      | V <sub>F3</sub>  |                | 1.00 | 1.05 | 1.10 | ٧    |

**Error Amplifier (Channel 1)**

| PARAMETER                        | SYMBOL           | TEST CONDITION                                            | MIN   | TYP   | MAX   | UNIT |  |  |  |

|----------------------------------|------------------|-----------------------------------------------------------|-------|-------|-------|------|--|--|--|

| Feedback Voltage                 | $V_{\text{IN1}}$ |                                                           | 1.221 | 1.233 | 1.245 | V    |  |  |  |

| Input Bias Current               | I <sub>B1</sub>  | V <sub>IN1</sub> = 1V to1.5V                              | -40   | 0     | 40    | nA   |  |  |  |

| Feedback-Voltage Line Regulation |                  | Level to Produce $V_{EO} = 1.233V$ $2.6V < V_{DD} < 5.5V$ |       | 0.05  | 0.15  | %/mV |  |  |  |

| Transconductance                 | G <sub>m</sub>   | $\Delta I = 5 \mu A$                                      |       | 105   |       | μS   |  |  |  |

| Voltage Gain                     | A <sub>V</sub>   |                                                           |       | 1,500 |       | V/V  |  |  |  |

#### N-MOS Switch (Channel 1)

| PARAMETER       | SYMBOL             | TEST CONDITION         | MIN | TYP  | MAX   | UNIT |

|-----------------|--------------------|------------------------|-----|------|-------|------|

| Current Limit   | I <sub>LIM</sub>   |                        |     | 3.0  |       | Α    |

| On-Resistance   | R <sub>ON</sub>    | I <sub>SW</sub> = 1.0A |     | 0.2  |       | Ω    |

| Leakage Current | I <sub>SWOFF</sub> | V <sub>SW</sub> = 12V  |     | 0.01 | 20.00 | μA   |

#### **AAT1164/AAT1164B/AAT1164C**

## **ELECTRICAL CHARACTERISTICS**

$(V_{DD}=2.6V \text{ to } 5.5V, T_C=-40\,^{\circ}\text{C to } 85\,^{\circ}\text{C}$ , unless otherwise specified. Typical values are tested at 25  $^{\circ}\text{C}$  ambient temperature,  $V_{DD}=3.3V, V_{DD1}=10V.)$

**Negative Charge Pump (Channel 2)**

| PARAMETER              | SYMBOL            | TEST CONDITIONS                       | MIN | TYP | MAX | UNIT |

|------------------------|-------------------|---------------------------------------|-----|-----|-----|------|

| IN2 Threshold Voltage  | $V_{IN2}$         | $I_{OUT2} = -100 \mu\text{A}$         | 235 | 250 | 265 | mV   |

| IN2 Input Bias Current | I <sub>B2</sub>   | $V_{IN2} = -0.25V$ to 0.25V           | -40 | 0   | 40  | nA   |

| OUT2 Leakage Current   | I <sub>OFF2</sub> | V <sub>IN2</sub> = 0V, OUT2 = -12V    |     | -20 | -50 | μΑ   |

| OUT2 Source Current    | I <sub>OUT2</sub> | V <sub>IN2</sub> = 0.35V, OUT2 = -10V | 1   | 4   |     | mA   |

**Positive Charge Pump (Channel 3)**

| PARAMETER              | SYMBOL            | TEST CONDITIONS                     | MIN  | TYP  | MAX  | UNIT |

|------------------------|-------------------|-------------------------------------|------|------|------|------|

| IN3 Threshold Voltage  | $V_{IN3}$         | I <sub>OUT3</sub> = 100 μA          | 1.22 | 1.25 | 1.28 | ٧    |

| IN3 Input Bias Current | I <sub>B3</sub>   | V <sub>IN3</sub> = 1V to 1.5V       | -40  | 0    | 40   | nA   |

| OUT3 Leakage Current   | I <sub>OFF3</sub> | V <sub>IN3</sub> = 1.4V, OUT3 = 28V |      | 40   | 80   | μΑ   |

| OUT3 Sink Current      | I <sub>OUT3</sub> | V <sub>IN3</sub> = 1.1V, OUT3 = 25V | 1    | 4    |      | mA   |

**High Voltage Switch Controller**

| PARAMETER                     | SYMBOL            | TEST CONDITIONS                    | MIN  | TYP  | MAX  | UNIT |

|-------------------------------|-------------------|------------------------------------|------|------|------|------|

| DLY Source Current            | I <sub>DLY</sub>  |                                    | -4   | -5   | -6   | μΑ   |

| DLY Threshold Voltage         | $V_{DLY}$         |                                    | 1.22 | 1.25 | 1.28 | V    |

| DLY Discharge R <sub>ON</sub> | R <sub>DLY</sub>  |                                    |      | 8    |      | Ω    |

| CTL Input Low Voltage         | V <sub>IL</sub>   |                                    |      |      | 0.5  | V    |

| CTL Input High Voltage        | V <sub>IH</sub>   |                                    | 2    |      |      | V    |

| CTL Input Bias Current        | I <sub>B4</sub>   | $V_{CTL} = 0$ to $V_{DD}$          | -40  | 0    | 40   | nA   |

| Propagation Delay CTL to VGH  | t <sub>PP</sub>   | OUT3 = 25V                         |      | 100  |      | ns   |

| VOUT3 to VGH Switch R-on      | R <sub>ONSC</sub> | $V_{DLY} = 1.5V, V_{CTL} = V_{DD}$ |      | 15   | 30   | Ω    |

| ADJ to VGH Switch R-on        | R <sub>ONDC</sub> | $V_{DLY} = 1.5V, V_{CTL} = GND$    |      | 30   | 60   | Ω    |

| VGH to GND1 Switch R-on       | R <sub>ONCG</sub> | $V_{DLY} = 1V$                     | 1.5  | 2.5  | 3.5  | kΩ   |

## AAT1164/AAT1164B/AAT1164C

## **ELECTRICAL CHARACTERISTICS**

$(V_{DD}=2.6V \text{ to } 5.5V, T_C=-40\,^{\circ}\text{C} \text{ to } 85\,^{\circ}\text{C}$ , unless otherwise specified. Typical values are tested at 25  $^{\circ}\text{C}$  ambient temperature,  $V_{DD}=3.3V, V_{DD1}=10V.)$

#### V<sub>COM</sub> and V<sub>GAMMA</sub> Buffer

| PARAMETER             | SYMBOL             | TEST CONDITIONS                                                                                                                           | MIN                       | TYP  | MAX                       | UNIT |

|-----------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|---------------------------|------|

| Input Offset Voltage  | V <sub>OS</sub>    | $V_{VI1+} \sim V_{VI5+} = 4V$                                                                                                             | -                         | 2    | 12                        | mV   |

| Input Bias Current    | I <sub>B5</sub>    | $V_{VI1+} \sim V_{VI5+} = 4V$                                                                                                             | -40                       | 0    | 40                        | nA   |

| Output Swing          | $V_{OL}$           |                                                                                                                                           | -                         | -    | V <sub>VI−</sub><br>+0.15 |      |

|                       |                    | I <sub>VO3</sub> = 50mA, V <sub>VI3</sub> = 4V                                                                                            | -                         | 4.03 | 4.06                      | V    |

|                       | V <sub>OH</sub>    | $ \begin{aligned} &I_{VO1},I_{VO2},I_{VO4},I_{VO5} = \\ &-50\text{mA},\\ &V_{VI1},V_{VI2},V_{VI4},V_{VI5} = 0V,\\ &4V,10V \end{aligned} $ | V <sub>VI-</sub><br>-0.15 |      | -                         |      |

|                       |                    | $I_{VO3} = -50 \text{mA}, \ V_{VI3} = 4 \text{V}$                                                                                         | 3.94                      | 3.97 | -                         |      |

| Chart Civarit Commant |                    | I <sub>VO1</sub> , I <sub>VO2</sub> , I <sub>VO4</sub> , I <sub>VO5</sub>                                                                 | -                         | ±100 | -                         | mA   |

| Short Circuit Current | I <sub>SHORT</sub> | I <sub>VO3</sub>                                                                                                                          | -                         | ±200 | -                         | mA   |

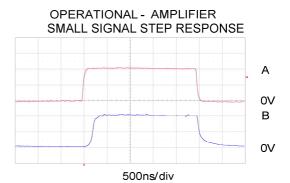

| Slew Rate             | SR                 | $V_{VI1+}, V_{VI3+} = 2V \text{ to } 8V,$<br>$V_{VI3+} \sim V_{VI5+} = 8V \text{ to } 2V,$<br>20% to 80%                                  | -                         | 12   | -                         | V/µs |

| Settling Time         | t <sub>S</sub>     | $V_{VI1+} \sim V_{VI5+} = 3.5V \text{ to } 4.5V,$ 90%                                                                                     | -                         | 5    |                           | μs   |

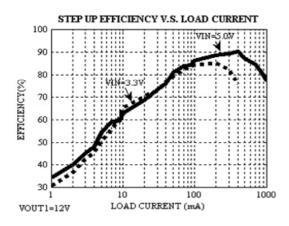

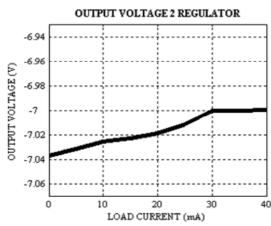

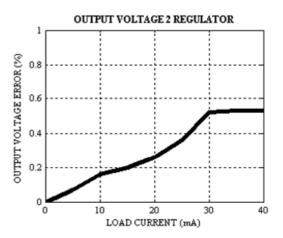

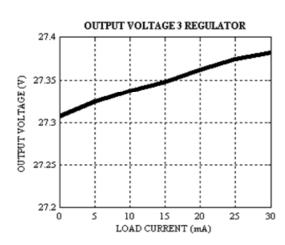

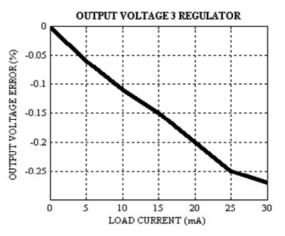

#### TYPICAL OPERATING CHARACTERISTICS

( $V_{IN}$  = 5V,  $V_{OUT1}$  = 12V,  $V_{OUT2}$  = -7V,  $V_{OUT3}$  = 27V,  $T_C$  = +25  $^{\circ}C$  , unless otherwise noted.)

## AAT1164/AAT1164B/AAT1164C

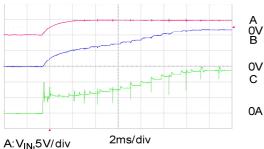

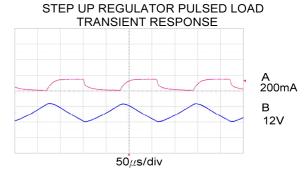

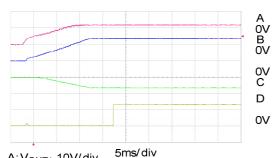

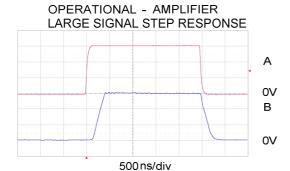

### **TYPICAL OPERATING CHARACTERISTICS (CONT.)**

$(V_{IN} = 5V, V_{OUT1} = 12V, V_{OUT2} = -7V, V_{OUT3} = 27V, T_C = +25$ °C, unless otherwise noted.)

B: V<sub>OUT1</sub>, 5V/div C: INDUCTOR CURRENT, 1A/div

A: LOAD CURRENT,100mA/div B: V<sub>OUT1</sub>, 200mV/div, AC-COUPLED

#### POWER ON SEQUENCE

A: V<sub>OUT1</sub>, 10V/div B: V<sub>OUT3</sub>, 20V/div C: V<sub>OUT2</sub>, 10V/div D: V<sub>O3</sub>, 20V/div

#### TIME DELAY LATCH RESPONSE TO

A: V<sub>OUT1</sub>,5 V/ div B: INDUCTOR CURRENT,1A/ div

A: INPUT SIGNAL,2V/div B: OUTPUT SINAL,2V/div V<sub>SUP</sub>= 6V

A: INPUT SIGNAL, 200 mV/div B: OUTPUT SINAL, 200 mV/div

Advanced Analog Technology, Inc. –

<sup>-</sup> 台灣類比科技股份有限公司 -

## AAT1164/AAT1164B/AAT1164C

## **PIN DESCRIPTION**

| PIN NO. | NAME  | I/O | DESCRIPTION                                           |  |

|---------|-------|-----|-------------------------------------------------------|--|

| QFN-32  |       |     |                                                       |  |

| 1       | VOUT3 | -   | Channel 3 Output Voltage (gate high voltage input)    |  |

| 2       | VERF  | 0   | Internal Reference Voltage Output                     |  |

| 3       | GND   | -   | Ground                                                |  |

| 4       | GND1  | -   | SW MOS Ground                                         |  |

| 5       | VO1   | 0   | Operational Amplifier 1 Output                        |  |

| 6       | VI1–  | I   | Operational Amplifier 1 Negative Input                |  |

| 7       | VI1+  | I   | Operational Amplifier 1 Positive Input                |  |

| 8       | VO2   | 0   | Operational Amplifier 2 Output                        |  |

| 9       | VI2-  | I   | Operational Amplifier 2 Negative Input                |  |

| 10      | VI2+  | I   | Operational Amplifier 2 Positive Input                |  |

| 11      | GND2  | -   | Ground for Operational Amplifiers                     |  |

| 12      | VI3+  | I   | V <sub>COM</sub> Operational Amplifier Positive Input |  |

| 13      | VO3   | I   | V <sub>COM</sub> Operational Amplifier Output         |  |

| 14      | VDD1  | -   | High Voltage Power Supply Input                       |  |

| 15      | VI4+  | I   | Operational Amplifier 4 Positive Input                |  |

| 16      | VI4–  | I   | Operational Amplifier 4 Negative Input                |  |

| 17      | VO4   | 0   | Operational Amplifier 4 Output                        |  |

| 18      | VI5+  | I   | Operational Amplifier 5 Positive Input                |  |

| 19      | VI5-  | I   | Operational Amplifier 5 Negative Input                |  |

| 20      | VO5   | 0   | Operational Amplifier 5 Output                        |  |

| 21      | SW    | -   | Main PWM Switching Pin                                |  |

| 22      | VDD   | -   | Power Supply Input                                    |  |

| 23      | IN1   | I   | Main PWM Feedback Pin                                 |  |

| 24      | EO    | 0   | Main PWM Error Amplifier Output                       |  |

| 25      | IN3   | I   | Positive Charge Pump Feedback Pin                     |  |

April 2007

## **AAT1164/AAT1164B/AAT1164C**

| PIN NO.<br>QFN-32 | NAME | I/O | DESCRIPTION                             |  |

|-------------------|------|-----|-----------------------------------------|--|

| 26                | OUT3 | 0   | Positive Charge Pump Output             |  |

| 27                | IN2  | I   | Negative Charge Pump Feedback Pin       |  |

| 28                | OUT2 | 0   | Negative Charge Pump Output             |  |

| 29                | DLY  | I   | High Voltage Switch Delay Control       |  |

| 30                | CTL  | I   | High Voltage Switch Control Pin         |  |

| 31                | ADJ  | 0   | Gate High Voltage Fall Time Setting Pin |  |

| 32                | VGH  | 0   | Switching Gate High Voltage for TFT     |  |

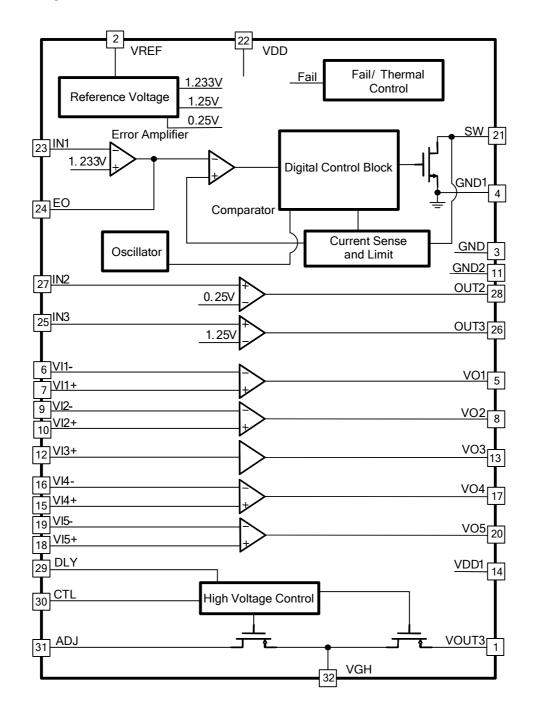

## **FUNCTION BLOCK DIAGRAM**

#### **AAT1164/AAT1164B**

<sup>-</sup> 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

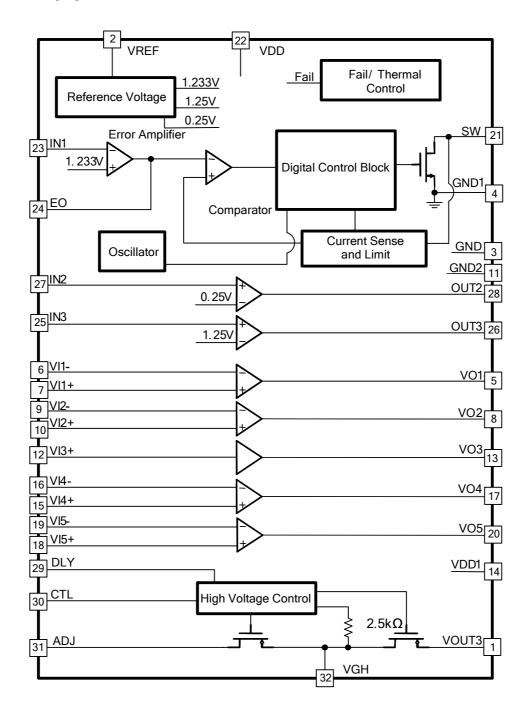

## **FUNCTION BLOCK DIAGRAM**

#### **AAT1164/AAT1164C**

<sup>-</sup> 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

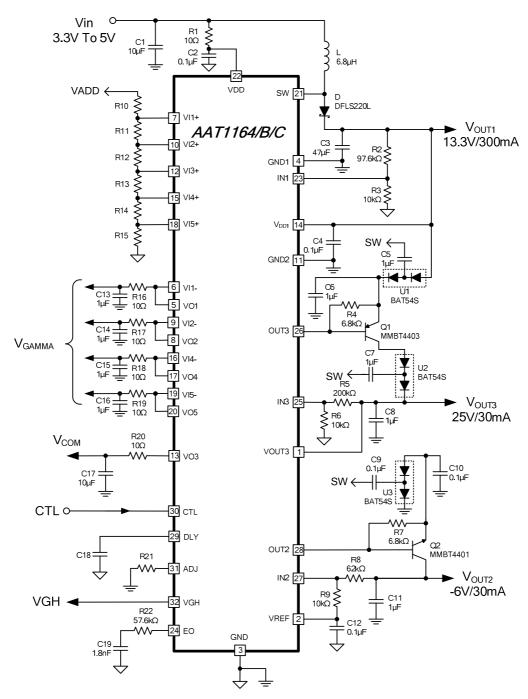

## **TYPICAL APPLICATION CIRCUIT**

Figure 1. Application Circuit

Advanced Analog Technology, Inc. –

Version 1.00

Page 14 of 24

<sup>-</sup> 台灣類比科技股份有限公司 -

#### AAT1164/AAT1164B/AAT1164C

### **DESIGN PROCEDURE**

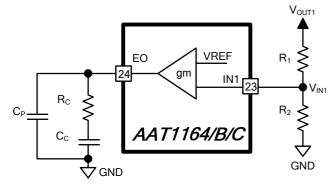

#### **Boost Converter Design** Setting the Output Voltage and Selecting the Lead Compensation Capacitor

The output voltage of boost converter is set by the resistor divider from the output (V<sub>OUT1</sub>) to GND with the center tap connected to IN1, where V<sub>IN1</sub>, the boost converter feedback regulation voltage is 1.233V, Choose  $R_2$  (Figure 2) between  $5.1k\Omega$  to  $51k\Omega$  and calculate R<sub>1</sub> to satisfy the following equation.

$$R_1 = R_2 \left( \frac{V_{OUT1}}{V_{IN1}} - 1 \right)$$

Figure 2. Feedback Circuit

#### **Inductor Selection**

The minimum inductance value is selected to make sure that the system operates in continuous conduction mode (CCM) for high efficiency and to prevent EMI. The equation of inductor uses a parameter k, which is the ratio of the inductor peak to peak ripple current to the input DC current. The best trade-off between voltage ripple of transient output current and permanent output current has a k between 0.4 and 0.5.

$$L \geq \frac{\eta V_O}{k I_O f_S} D (1-D)^2 \,,$$

$$D = 1 - \frac{V_{IN}}{V_{O}}$$

$$k = \frac{\Delta I_{Lpeak-peak}}{I_{IN}}$$

η: Boost converter efficiency

k: The ratio of the inductor peak to peak ripple current to the input DC current

V<sub>IN</sub>: Input voltage

Vo: Output voltage

Io: Output load current

fs: Switching frequency

D: Duty cycle

ΔI<sub>Lpeak-peak</sub>: Inductor peak to peak ripple current

I<sub>IN</sub>: Input DC current

The AAT1164 SW current limit (I<sub>LIM</sub>) and inductor's saturation current rating (I<sub>LSAT</sub>) should exceed I<sub>L(peak)</sub>, and the inductor's DC current rating should exceed I<sub>IN</sub>. For the best efficiency, choose an inductor with less DC series resistance (r1).

$$I_{LIM}$$

and  $I_{LSAT} > I_{L(peak)}$

$$I_{LDC} > I_{IN}$$

$$\begin{split} &I_{LDC} > I_{IN} \\ &I_{L(peak)} = I_{IN} + \frac{V_{IN}D}{2Lf_S} \,, \end{split}$$

$$I_{IN} = \frac{I_O}{\eta(1-D)} ,$$

$$P_{DCR} \approx \left(\frac{I_O}{\eta(1-D)}\right)^2 r_L$$

I<sub>LDC</sub>: DC current rating of inductor

P<sub>DCR</sub>: Power loss of inductor series resistance

**Table 1. Inductor Data List**

| C6-K1.8L                         | rL   | DC CURRENT RATING |  |  |

|----------------------------------|------|-------------------|--|--|

| 3.9µH                            | 41mΩ | 2.5A              |  |  |

| 6.8µH                            | 68mΩ | 2.2A              |  |  |

| 10µH                             | 81mΩ | 1.8A              |  |  |

| MITSUMI Product-Max Height:1.9mm |      |                   |  |  |

#### AAT1164/AAT1164B/AAT1164C

Example 1: In the typical application circuit (Figure 1) the output load current is 300mA with 13.3V output voltage and input voltage of 5V. Choose a k of 0.431 and efficiency of 90%.

$$\begin{split} L & \geq \frac{0.9 * 13.3}{0.431 * 0.3 * 1.2^6} \, 0.624 (0.376)^2 \approx 6.8 \, \mu H \\ I_{IN} & = \frac{I_O}{\eta (1-D)} = 0.886 A \\ I_{L(peak)} & = I_{IN} + \frac{V_{IN}D}{2Lf_S} = 1.0778 A \end{split}$$

$P_{DCR} = 0.0534W$  or 1.34% power loss

#### **Schottky Diode Selection**

Schottky has to be able to dissipate power. The dissipated power is the forward voltage and input DC current. To achieve the best efficiency, choose a Schottky diode with less recovery capacitor  $(C_T)$  for fast recovery time and low forward voltage  $(V_F)$ .

For boost converter, the reverse voltage rating  $(V_{\text{R}})$  should be higher than the maximum output voltage, and current rating should exceed the input DC current.

$$\begin{split} P_{\text{DIODE}} &= P_{\text{DSW}} + P_{\text{DCOM}} \\ P_{\text{DSW}} &= (1 - D) \ V_F Q_R f_S \\ Q_R &= V_R C_T Q_R \\ P_{\text{DCOM}} &= V_F I_O \ (1 - D) \end{split}$$

P<sub>DIODE</sub>: Total power loss of diode for boost converter P<sub>DSW</sub>: Switching loss of diode for boost converter P<sub>DCOM</sub>: Conduction loss of diode for boost converter

**Table 2. Schottky Data List**

| rabio 21 conotiny bata 21ct      |         |         |       |  |  |

|----------------------------------|---------|---------|-------|--|--|

| SMA                              | $V_{F}$ | $V_{R}$ | $C_T$ |  |  |

| B220A                            | 0.24V   | 14V     | 150pF |  |  |

| B240A                            | 0.24V   | 28V     | 150pF |  |  |

| DIODES Product-Max Height: 2.3mm |         |         |       |  |  |

For example,

$P_{DIODE} = P_{DSW} + P_{DCOM} = 0.0273W$  or 0.68% power loss.

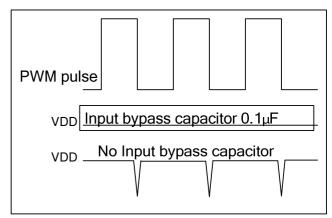

#### **Input Capacitor Selection**

The input capacitors have two important functions in PWM controller. First, an input capacitor provides the power for soft start procedure and supply the current for the gate-driving circuit. A 10  $\mu F$  ceramic capacitor is used in typical circuit. Second, an input bypass capacitor reduces the current peaks, the input voltage drop, and noise injection into the IC. A low ESR ceramics capacitor 0.1  $\mu F$  is used in typical circuit. To ensure the low noise supply at  $V_{DD},\,V_{DD}$  is decoupled from input capacitor using an RC low pass filter.

Figure 3. Input Bypass Capacitor Affects the  $V_{\text{DD}}$  Drop.

#### **Output Capacitor**

The output capacitor maintains the DC output voltage. A Low ESR ( $r_{\rm C}$ ) ceramic capacitor can reduce the output ripple and power loss. There are two parameters which can affect the output voltage ripple: 1. the voltage drops when the inductor current flows through the ESR of output capacitor; 2. charging and discharging of the output capacitor also affect the output voltage ripple.

$V_{RIPPLE} = V_{RIPPLE}(C_{OUT}) + V_{RIPPLE}(ESR)$

Advanced Analog Technology, Inc. –

#### AAT1164/AAT1164B/AAT1164C

$$V_{RIPPLE}(C_{OUT}) \approx \frac{I_{O}D}{f_{S}C_{OUT}}$$

$V_{RIPPLE}(ESR) \approx I_{L(peak)} r_{C}$

$$I_{C(rms)} = \frac{V_{O}}{R_{L}} \sqrt{\frac{D}{1-D} + \frac{D}{12} [\frac{(1-D)R_{L}}{Lf_{S}}]^{2}}$$

$$P_{ESR} = (I_{C(rms)})^2 r_{C}$$

ESR: Equivalent Series Resistance

Example 2:  $C_{OUT} = 38\mu F$ ,  $r_C = 20 \text{ m}\Omega$

$V_{RIPPLE}(C_{OUT}) = 4.1 \text{mV}$

$V_{RIPPIF}(ESR) = 21.5 \text{mV}$

$V_{RIPPLE} = 25.6 \text{mV}$

$I_{C(rms)} = 0.411A$

$P_{ESR} = 0.00338W$  or 0.08% power loss

#

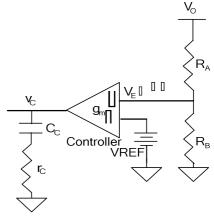

Figure 4. Closed-Current Loop for Boost with PCM

#### **Boost Converter Power loss**

The largest portions of power loss in the boost converter are the internal power MOSFET, the inductor, the Schottky diode, and the output capacitor. If the boost converter has 90% efficiency, there is approximately 7.89% power loss in the internal MOSFET, 1.34% power loss in the inductor, 0.68% power loss in the Schottky diode, and 0.08% power loss in the output capacitor.

# Vg Vg Nosfet CLK Rsii Vc Tc Ve SVc Vr Vr Vr Vr

Figure 5. Block Diagram of Boost Converter with Peak Current Mode (PCM)

#### **Loop Compensation Design**

The voltage-loop gain with current loop closed sets the stability of steady state response and dynamic performance of transient response. The loop compensation design is as follows:

#### **Power Stage Transfer Functions**

The duty to output voltage transfer function  $T_p$  is:

$$T_{p}(s) = \frac{V_{O}}{d} = T_{p0} \frac{(s + \omega_{esr})(s - \omega_{z2})}{s^{2} + 2\xi\omega_{n}s + \omega_{n}^{2}}$$

Where

$$T_{p0} = V_O \, \frac{-r_C}{\left(1-D\right)\left(R_L + r_C\right)}$$

,  $\omega_{esr} = \frac{1}{C_{OUT}r_C}$

And

$$\omega_{z2} = \frac{R_L \left(1-D\right)^2 - r}{L} \,, \\ \omega_n = \sqrt{\frac{\left(1-D\right)^2 R_L + r}{L C_{OUT} \left(R_L + r_C\right)}} \label{eq:omega_z2}$$

#### AAT1164/AAT1164B/AAT1164C

$$\xi = \frac{C_{OUT}[r(R_L + r_C) + R_L r_C (1 - D)^2] + L}{2\sqrt{LC_{OUT}(R_L + r_C)[r + (1 - D)^2 R_L]}},$$

$$r = r_L + Dr_{DS} + (1 - D)R_F$$

$r_{L}$  is the inductor equivalent series resistance,  $r_{C}$  is capacitor ESR,  $R_{L}$  is the converter load resistance,  $C_{OUT}$  is the output filter capacitor,  $r_{DS}$  is the transistor turn on resistance, and  $R_{F}$  is the diode forward resistance.

The duty to inductor current transfer function  $T_{pi}$  is:

$$T_{pi}(s) = \frac{i_{l}}{d} = T_{pi0} \frac{s + \omega_{zi}}{s^{2} + 2\xi\omega_{n}s + \omega_{n}^{2}}$$

Where

$$T_{pi0} = \frac{V_{O}(R_{L} + 2r_{C})}{L(R_{L} + r_{C})}$$

,  $\omega_{zi} = \frac{1}{C_{OUT}(R_{L} / 2 + r_{C})}$

#### **Current Sampling Transfer Function**

Error voltage to duty transfer function  $F_m(s)$  is:

$$F_{m}(s) = \frac{d}{V_{ei}} = \frac{2f_{S}^{2} \left(s^{2} + 2\xi \omega_{n} s + {\omega_{n}}^{2}\right)}{T_{pi0} R_{CS} s \left(s + {\omega_{zi}}\right) \left(s + {\omega_{sh}}\right)}$$

Where

$$\omega_{sh} = \frac{3\omega_s}{\pi} \left(\frac{1-\alpha}{1+\alpha}\right)$$

,  $\alpha = \frac{M_2-M_a}{M_1+M_a}$ ,

$$\omega_s = 2\pi f_S$$

Therefore,  $F_m(s)$  depends on duty to inductor current transfer function  $T_{pi}(s)$ , and  $f_S$  is the clock switching frequency;  $R_{CS}$  is the current-sense amplifier transresistance.

For the boost converter  $M_1 = V_{IN} / L$  and  $M_2 = (V_O - V_{IN}) / L$ .

For AAT1164,  $R_{CS} = 0.24$  V/A, Ma is slope compensation, Ma =  $0.8 \times 10^{6}$ .

The closed-current loop transfer function  $T_{pi}(s)$  is:

$$T_{icl}(s) = \frac{{12{f_S}^2 }}{{R_{CS}}{T_{pi0}}} \times \frac{{{\left( {{s^2} + 2\xi {\omega _n}s + {\omega _n}^2} \right)}}}{{{\left( {s + {\omega _{zi}}} \right)}{{\left( {s^2} + {\omega _{sh}}s + 12{f_S}^2} \right)}}}$$

# The Voltage-Loop Gain with Current Loop Closed

The control to output voltage transfer function T<sub>d</sub> is:

$$T_{d}(s) = \frac{V_{O}(s)}{V_{C}(s)} = T_{icl}(s)T_{p}(s)$$

The voltage-loop gain with current loop closed is:

$$L_{VI}(s) = \beta T_{C}(s) T_{d}(s)$$

$$= \beta g_m R_C \frac{s + \omega_c}{s} \frac{12 f_S^2 T_{p0}}{R_{CS} T_{pi0}} \times$$

$$\frac{(s+\omega_{z1})(s-\omega_{z2})}{(s+\omega_{zi})(s^2+s\omega_{sh}+12f_S^2)}$$

Where

$$\beta = \frac{V_{FB}}{V_{O}}$$

The compensator transfer function

$$T_C(s) = \frac{V_C}{V_{fb}} = g_m R_C \, \frac{s + \omega_c}{s} \; , \label{eq:TC}$$

Vhere

$$\omega_C = \frac{1}{R_C C_C}$$

Figure 6. Voltage Loop Compensator

#### AAT1164/AAT1164B/AAT1164C

Compensator design guide:

- 1. Crossover frequency  $f_{ci} < \frac{1}{2}f_S$

- 2. Gain margin>10dB

- 3. Phase margin>45°

- 4. The  $|L_{VI}(s)| = 1$  at crossover frequency, Therefore, the compensator resistance,  $R_C$  is determined by:

$$R_C = \frac{V_O}{V_{FB}} \frac{2\pi f_{ci} C_{OUT} R_{CS}}{g_m k} \frac{\left(R_L + 2r_C\right)}{\left[\left(1 - D\right) R_L - \frac{r}{\left(1 - D\right)}\right]} \label{eq:RC}$$

Table 3. k Factor Table

| 10.010 01.111.0001 |             |           |  |

|--------------------|-------------|-----------|--|

| Соит               | Best Corner | k Factor  |  |

| Cout               | Frequency   | K i dotoi |  |

| 21.533μF           | 23.740kHz   | 4.692     |  |

| 25.079μF           | 21.842kHz   | 5.083     |  |

| 32.587μF           | 20.095kHz   | 6.042     |  |

| 36.312μF           | 15.649kHz   | 5.230     |  |

| 38.469μF           | 13.247kHz   | 4.703     |  |

5. The output filter capacitor is chosen so  $C_{\mbox{OUT}}R_{\mbox{\scriptsize L}}$  pole cancels  $R_{\mbox{\scriptsize C}}C_{\mbox{\scriptsize C}}$  zero

$$\begin{split} \epsilon R_C C_C &= C_{OUT} \Bigg( \frac{R_L}{2} + r_C \Bigg), \text{ and} \\ C_C &= \frac{C_{OUT}}{\epsilon R_C} \Bigg( \frac{R_L}{2} + r_C \Bigg) \\ \epsilon &= (1 \sim 3) \end{split}$$

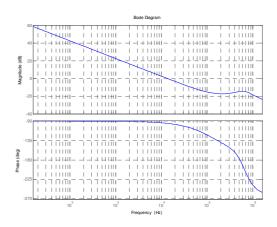

#### Example 3:

$$\begin{split} &V_{IN}=5V,\ V_O=13.3V,\ I_O=300mA,\ f_S=1,190kHz,\\ &V_{FB}=1.233V,\ L=6.65\mu H,\ g_m=85\mu S,\\ &r_L=76.689\,m\Omega\\ &r_C=9.13\,m\Omega,\ R_F=0.7667\,\Omega\,,C_C=1.95nF,\\ &R_C=7.6\,k\Omega\,,\ C_{OUT}=38.5\,\mu\,F\,,\epsilon=3,\ R_{CS}=0.23V/A. \end{split}$$

Figure 7. Bode Plot of Loop Gain Using Matlab® Simulation

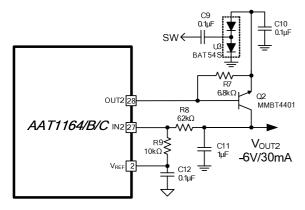

#### Positive and Negative LDO Driver Output Voltage Selection

The output voltage of positive LDO driver is set by a resistive divider from the output ( $V_{OUT3}$ ) to GND with the center tap connected to the IN3, where  $V_{IN3}$ , the positive LDO driver feedback regulation voltage, is 1.25V. Choose  $R_6$  (Figure 8) between  $10k\Omega$  and  $51k\Omega$ . And calculate  $R_5$  with the following equation.

$$R_5 = R_6 \left( \frac{V_{\text{OUT3}}}{V_{\text{IN3}}} - 1 \right)$$

The output voltage of negative LDO driver is set by a resistive divider from the output ( $V_{OUT2}$ ) to VREF with the center tap connected to IN2, where  $V_{IN2}$ , the negative LDO driver feedback regulation voltage, is 0.25V. Choose R<sub>9</sub> (Figure 9) between 10k $\Omega$  and 51k $\Omega$  and calculate R<sub>8</sub> with the following equation.

$$R_8 = R_9 \left( \frac{V_{IN2} - V_{OUT2}}{V_{REF} - V_{IN2}} \right)$$

#### AAT1164/AAT1164B/AAT1164C

Figure 8. The Positive LDO Driver

Figure 9. The Negative LDO Driver

#### Example 4:

For system design

$$\begin{split} V_{OUT3} &= 25 V, \ R_5 = 200 k \Omega, \ R_6 = 10 k \Omega, \\ V_{OUT2} &= -6 V, \ R_8 = 62 k \Omega, \ R_9 = 10 k \Omega \end{split}$$

#### Flying Capacitors

Increasing the flying capacitor ( $C_5$ ,  $C_7$ ,  $C_9$ ) values can lower output voltage ripples. The  $1\mu F$  ceramic capacitors works well in positive LDO driver. A  $0.1\mu F$  ceramic capacitor works well in negative LDO driver.

#### **LDO Driver Diode**

To achieve high efficiency, a Schottky diode should be

used. BAT54S (Figure 8 and 9) has fast recovery time and low forward voltage for best efficiency.

#### **LDO Driver Base-Emitter Resistors**

For AAT1164, the minimum drive current for positive and negative LDO drivers are 1mA, thus the minimum base-emitter resistance can be calculated by the following equation:

$$\begin{aligned} R_{4(min)} &\geq V_{BE(max)} / ((I_{OUT3(min)} - I_{C}) / h_{fe(min)}) \\ R_{7(min)} &\geq V_{BE(max)} / ((I_{OUT2(min)} - I_{C}) / h_{fe(min)}) \end{aligned}$$

**Table 4. Pass Transistor Specifications**

|                                | MMBT4401                    | MMBT4403 |  |

|--------------------------------|-----------------------------|----------|--|

| V <sub>BE(max)</sub>           | 0.65V                       | 0.5V     |  |

| h <sub>fe(min)</sub>           | h <sub>fe(min)</sub> 130 90 |          |  |

| DIODES Product, Package: SOT23 |                             |          |  |

#### Example 5:

Output current of  $V_{\text{OUT3}}$  and  $V_{\text{OUT2}}$  are 30mA, the minimum base-emitter resistor can be calculated as

$$R_{4(min)} \ge 0.5 / ((|1mA - 30mA|) / 90) \ge 750 \Omega$$

$R_{7(min)} \ge 0.65 / ((|1mA - 30mA|) / 130) \ge 845 \Omega$

The minimum value can be used, however, the larger value has the advantage of reducing quiescent current. So we choose  $6.8k\Omega$  to be  $R_4$ .

#### **Charge Pump Output Capacitor**

Using low ESR ceramic capacitor to reduce the output voltage ripple is recommended and output voltage ripple is dominated by the capacitance value. The minimum capacitance value can be calculated by the following equation:

#### AAT1164/AAT1164B/AAT1164C

$$C_{OUT} \ge \frac{I_{LOAD}}{2V_{ripple}f_S}$$

#### Example 6:

The output voltage ripple of  $V_{\text{OUT3}}$  and  $V_{\text{OUT2}}$  is under 1%, the minimum capacitance value can be calculated as

$$C_{OUT}(V_{OUT3}) \geq \frac{30mA}{\eta 2 \times 250mV \times 1.19MHz} \approx 0.1 \mu F$$

$$C_{OUT}(V_{OUT2}) \geq \frac{30mA}{\eta 2 \times 60mV \times 1.19MHz} \approx 0.33 \mu F$$

$\eta$  : Efficiency, about 60% at charge pump circuit

**Table 5. Recommended Components**

| DESIGNATION          | DESCRIPTION                |  |

|----------------------|----------------------------|--|

| 1                    | 6.8 μH, 1.8A,              |  |

| L                    | MITSUMI C6-K1.8L 6R8       |  |

|                      | 200mA 30V Schottky barrier |  |

| U1, U2, U3           | diode (SOT-23),            |  |

|                      | DIODES BAT54S              |  |

| <u></u>              | 2A 20V rectifier diode     |  |

| U                    | DIODES DFLS220L            |  |

| 00                   | 10 μF, 25V X5R ceramic     |  |

| C3                   | capacitor                  |  |

| 05 00 07             | 1 μF, 25V X5R ceramic      |  |

| C5, C6, C7           | capacitor                  |  |

| C0 C4 C0 C10 C10     | 0.1 μF, 50V X5R ceramic    |  |

| C2, C4, C9, C10, C12 | capacitor                  |  |

#### **Operational Amplifier**

The AAT1164 has five independent amplifiers. The operational amplifiers are usually used to drive  $V_{\text{COM}}$  and the gamma correction divider string for TFT-LCD. The output resistors and capacitors of amplifiers are used as low pass filters and compensators for unity gain stable.

#### **Soft Start Waveform**

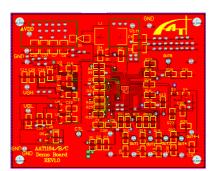

## **LAYOUT CONSIDERATION**

The system's performances including switching noise, transient response, and PWM feedback loop stability are greatly affected by the PC board layout and grounding. There are some general guidelines for layout:

#### Inductor

Always try to use a low EMI inductor with a ferrite core.

#### **Filter Capacitors**

Place low ESR ceramics filter capacitors (between  $0.1\mu F$  and  $0.22\mu F$ ) close to VDD and VREF pins. This will eliminate as much trace inductance effects as possible and give the internal IC rail a cleaner voltage

supply. The ground connection of the VDD and VREF bypass capacitor should be connected to the analog ground pin (GND) with a wide trace.

#### **Output Capacitors**

Place output capacitors as close as possible to the IC. Minimize the length and maximize the width of traces to get the best transient response and reduce the ripple noise. We choose  $10\mu F$  ceramics capacitor to reduce the ripple voltage, and use  $0.1\mu F$  ceramics capacitor to reduce the ripple noise.

Advanced Analog Technology, Inc. –

#### AAT1164/AAT1164B/AAT1164C

#### **Feedback**

If external compensation components are needed for stability, they should also be placed close to the IC. Take care to avoid the feedback voltage-divider resistors' trace near the SW. Minimize feedback track lengths to avoid the digital signal noise of TFT control board.

#### **Ground Plane**

The grounds of the IC, input capacitors, and output capacitors should be connected close to a ground plane. It would be a good design rule to have a ground plane on the PCB. This will reduce noise and ground loop errors as well as absorb more of the EMI radiated by the inductor. For boards with more than two layers, a ground plane can be used to separate the power plane and the signal plane for improved performance.

#### **PC Board Layout**

Figure 10. TOP Layer

Figure 11. Midlayer1 (Ground Plane)

Figure 12. Midlayer2 (Power Plane)

Figure 13. Bottom Layer

## **AAT1164/AAT1164B/AAT1164C**

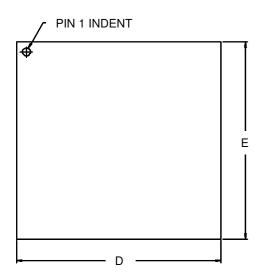

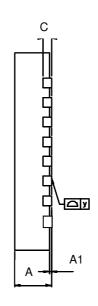

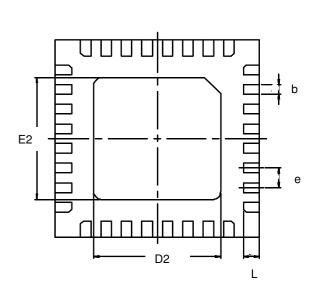

## **PACKAGE DIMENSION**

#### VQFN32

| Cymbol | Dimensions In Millimeters |      |       |  |

|--------|---------------------------|------|-------|--|

| Symbol | MIN                       | TYP  | MAX   |  |

| Α      | 0.8                       | 0.9  | 1.0   |  |

| A1     | 0.00                      | 0.02 | 0.05  |  |

| b      | 0.18                      | 0.25 | 0.30  |  |

| С      |                           | 0.2  |       |  |

| D      | 4.9                       | 5.0  | 5.1   |  |

| D2     | 3.05                      | 3.10 | 3.15  |  |

| E      | 4.9                       | 5.0  | 5.1   |  |

| E2     | 3.05                      | 3.10 | 3.15  |  |

| е      |                           | 0.5  |       |  |

| L      | 0.35                      | 0.40 | 0.45  |  |

| V      | 0.000                     |      | 0.075 |  |