# austriamicrosystems

AS8267 / AS8268 Single-Phase 2-Current Energy Measurement Integrated Circuits with Microcontroller, RTC, Programmable Multi-Purpose I/Os, LCD Driver and On-Chip FLASH Memory

# 1. Key Features

- Precision single-phase, one or two current input energy measurement front-end including Sigma-Delta modulators for A/D-conversion and digital signal processor (DSP).

- Low current consumption of 5mA, depending on MCU activity.

- Digital phase correction and selectable gain on both current channels for use with two current transformers (CT) or one CT and one shunt.

- Power-supply monitor (PSM) for power-on reset and reset when the supply voltage falls below a defined threshold.

- Customer programmable 8-bit 8051 compatible microcontroller (MCU).

- Programmable MCU clock for optional low power operating conditions.

- Highly reliable 32kBytes of non-volatile Flash memory is provided on-chip for storage of both program and data.

- Program and data security is provided by optional password and attack counter protection.

- 2 x Universal Asynchronous Receiver / Transmitters (UART) for external communications such as programme download and debugging.

- Programmable watchdog timer (WDT) and external system reset pin.

- Real-time clock/calendar (RTC) with on-chip digital calibration and separate battery supply pin.

- On-chip temperature sensor for optional temperature compensation.

- On-chip voltage reference (VREF) with small temperature coefficient (15ppm/K typ.).

- Low power 3.0 4.0MHz crystal oscillator.

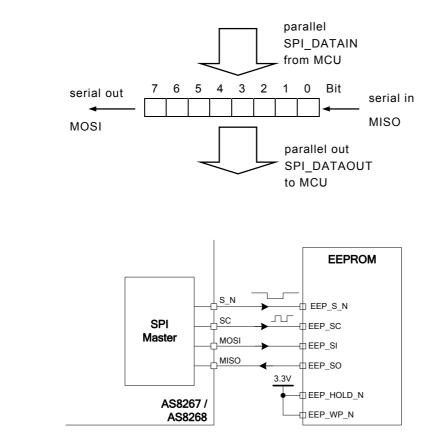

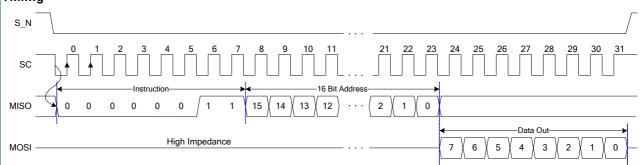

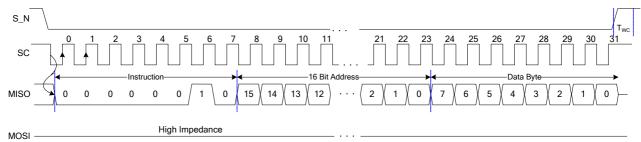

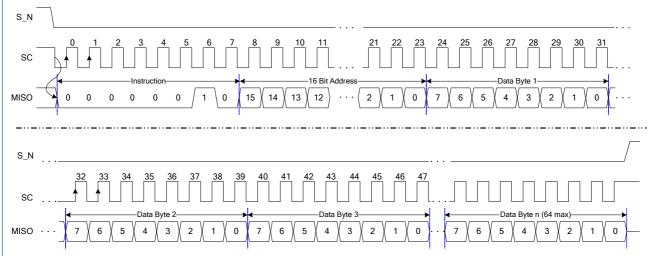

- SPI compatible interface for optional external non-volatile EEPROM memory selectable up to 32kBytes.

- Mains current lead/lag status indication for reactive energy measurement.

**DATA SHEET**

- Low power battery operating mode for meter reading when Mains voltage is not present.

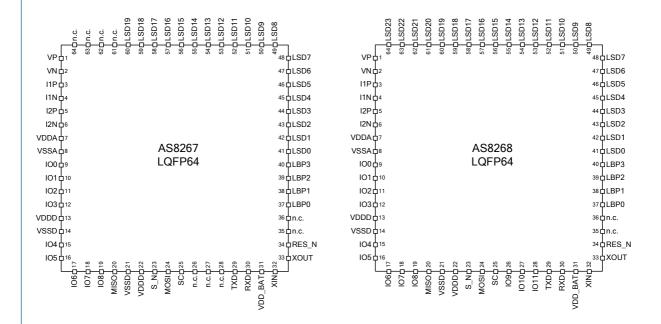

- AS8267: 20 x 4 segment LCDD 9 x multi-purpose I/O (MPIO)

- AS8268: 24 x 4 segment LCDD 12 x multi-purpose I/O (MPIO)

# 2. General Description

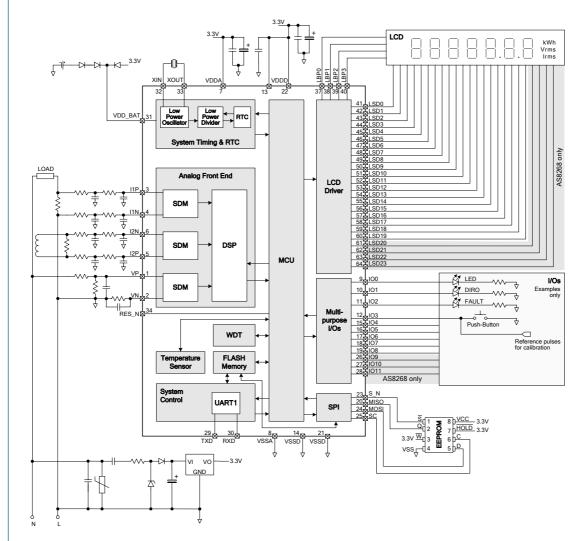

The AS8267 / AS8268 are highly integrated CMOS single-phase energy metering devices for fully electronic LCD meter systems. The AS8267 / AS8268 have been designed to ensure a meters full compliance with the international Standards IEC62052 and ANSI.

The AS8267 / AS8268 ICs include all the functions required for conventional 1 current or 2-current anti-tamper meters. The functions include precision energy measurement, an 8-bit microcontroller unit (MCU) with 32kBytes of Flash memory, an on-chip Liquid Crystal Display driver (LCDD), programmable multi-purpose Inputs/Outputs (MPIO), a real time clock/calendar (RTC) for complex tariff functions such as time-of-use or maximum demand billing and a Serial Peripheral Interface (SPI) for reading data from and writing data to an optional external non-volatile memory (EEPROM).

The AS8267 / AS8268 ICs have a dedicated energy measurement front-end, which includes an analog front-end and programmable Digital Signal Processor (DSP) from which active energy, mains voltage and mains current are provided. Reactive and apparent energy can also be calculated.

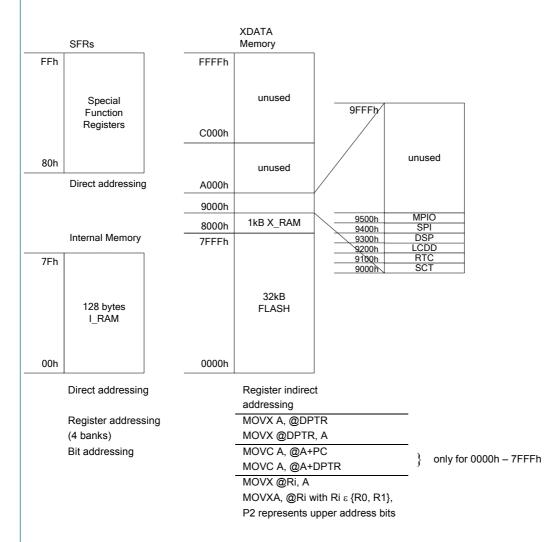

The on-chip 8-bit 8051 compatible microcontroller is freely programmable and provides user access to the various functional blocks. The dedicated Universal Asynchronous Receiver / Transmitter (UART1) in the System Control block allows access to various system functions and blocks. A second UART (UART2) is also provided, which may for example be used for debugging. The on-chip memory includes 32kByte of highly reliable nonvolatile Flash program (and data) memory and

1kByte volatile data memory. The meter system designer also has the option of an additional external EEPROM memory, which is selectable in size from 1kByte to 32kByte (in binary steps).

Program and data stored in the on-chip non-volatile Flash memory can be secured by password protection, in addition to an attack counter which 'locks' access after 5 unauthorised attacks.

An on-chip programmable watchdog timer (WDT) is available to automatically initiate a system reset if a regular 'hold-off' signal is not detected.

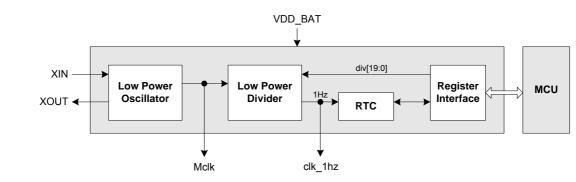

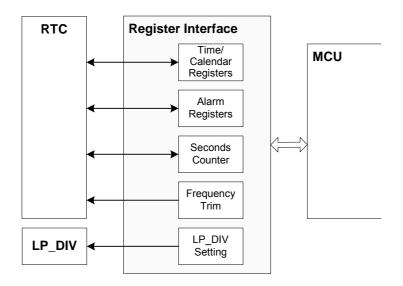

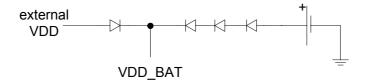

The system timing and real time clock (RTC) has a dedicated external battery supply pin (VDD\_BAT), enabling the oscillator and RTC to continue operation during 'power-down'. The RTC may be digitally calibrated for oscillator frequency accuracy.

The on-chip temperature sensor provides the meter designer the option of temperature compensation for any of the measured parameters or functional blocks provided, over the full operating temperature range of the device.

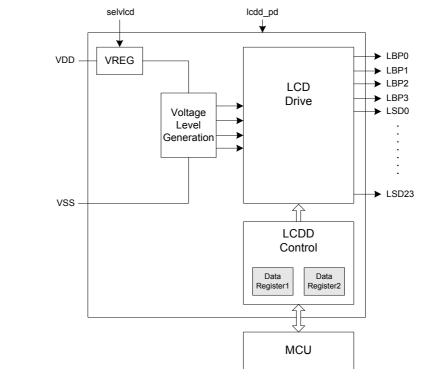

The LCD Driver (LCDD) block enables the display of information provided by the microcontroller, directly to the LCD. Two dedicated data register banks are provided to simplify programming, particularly in the case where scrolled display data is required.

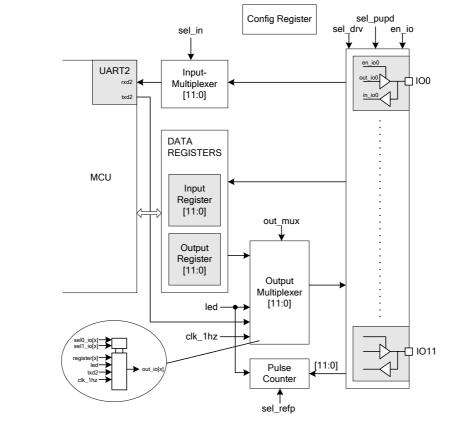

The programmable multi-purpose I/O pins (MPIO) may be independently configured as inputs or outputs. All the I/O pins are programmable for data direction, pull-up/pull-down resistors and drive strength (4mA/8mA). Typical functions may include LED energy consumption pulse output, energy direction and fault condition indication depending on current 1 or current 2 being active for the energy calculation, push button for display scrolling, mains isolation relay control for prepayment meters, optical interface etc.

An on-chip analog ground buffer (ABUF) and voltage reference (VREF) ensures that no external circuitry is required. A power-supply monitor (PSM) provides a reset, when VDD falls below a safe operating threshold.

A reset pin (RES\_N) is available for external system reset.

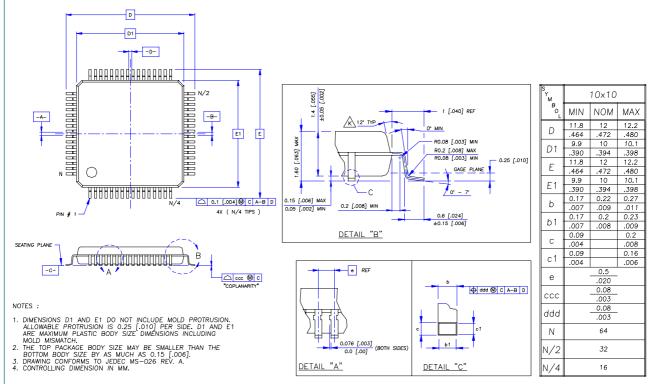

The AS8267 / AS8268 ICs are available in LQFP64 plastic package.

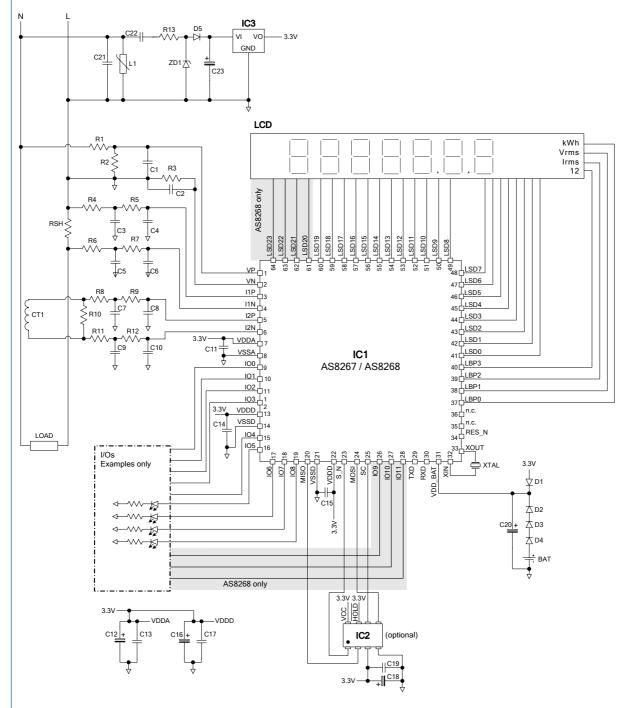

# 3. Typical Application Circuit

# 4. Pin Out

# 5. Pin Description

| Pin<br>No. | Pin Name<br>AS8267 | Pin Name<br>AS8268 | Туре | Description                                                                                                                                                                                                                    |

|------------|--------------------|--------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VP                 | VP                 | AI   | Positive input for the voltage channel. VP is a differential input with VN. The typical differential voltage is $\pm 100 mV$ peak.                                                                                             |

| 2          | VN                 | VN                 | AI   | Negative input for the voltage channel. VN is a differential input with VP.                                                                                                                                                    |

| 3          | l1P                | l1P                | AI   | Positive input for the first current channel. I1P is a differential input with I1N. The input gain is programmable depending on the desired current sensor. The typical differential voltage is $\pm 150$ mV peak (Gain = 4).  |

| 4          | I1N                | I1N                | AI   | Negative input for the first current channel. I1N is a differential input with I1P. The input gain is programmable depending on the desired current sensor. The typical differential voltage is $\pm 150$ mV peak (Gain = 4).  |

| 5          | I2P                | I2P                | AI   | Positive input for the second current channel. I2P is a differential input with I2N. The input gain is programmable depending on the desired current sensor. The typical differential voltage is $\pm 150$ mV peak (Gain = 4). |

| 6          | I2N                | I2N                | AI   | Negative input for the second current channel. I2N is a differential input with I2P. The input gain is programmable depending on the desired current sensor. The typical differential voltage is $\pm 150$ mV peak (Gain = 4). |

| 7          | VDDA               | VDDA               | S    | Positive supply voltage for the analog circuitry. The required supply voltage is 3.3V $\pm 10\%.$                                                                                                                              |

| 8          | VSSA               | VSSA               | S    | Ground reference for the analog circuitry.                                                                                                                                                                                     |

| 9          | IO0                | IO0                | DIO  | Programmable multi-purpose input/output, with selectable pull-up or pull-down resistors and selectable drive strength.                                                                                                         |

| 10         | IO1                | IO1                | DIO  | Programmable multi-purpose input/output, with selectable pull-up or pull-down resistors and selectable drive strength.                                                                                                         |

| Pin<br>No. | Pin Name<br>AS8267 | Pin Name<br>AS8268 | Туре  | Description                                                                                                                                                                         |  |  |  |

|------------|--------------------|--------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 11         | IO2                | IO2                | DIO   | Programmable multi-purpose input/output, with selectable pull-up or pull-down resistors and selectable drive strength.                                                              |  |  |  |

| 12         | IO3                | IO3                | DIO   | Programmable multi-purpose input/output, with selectable pull-up or pull-down resistors and selectable drive strength.                                                              |  |  |  |

| 13         | VDDD               | VDDD               | S     | Positive supply voltage to the digital circuitry and is internally connected to pin 22. The required supply voltage is $3.3V \pm 10\%$ .                                            |  |  |  |

| 14         | VSSD               | VSSD               | S     | Ground reference for the digital circuitry.                                                                                                                                         |  |  |  |

| 15         | IO4                | IO4                | DIO   | Programmable multi-purpose input/output, with selectable pull-up or pull-down resistors and selectable drive strength.                                                              |  |  |  |

| 16         | IO5                | IO5                | DIO   | Programmable multi-purpose input/output, with selectable pull-up or pull-down resistors and selectable drive strength.                                                              |  |  |  |

| 17         | IO6                | IO6                | DIO   | Programmable multi-purpose input/output, with selectable pull-up or pull-down resistors and selectable drive strength.                                                              |  |  |  |

| 18         | 107                | 107                | DIO   | Programmable multi-purpose input/output, with selectable pull-up or pull-down resistors and selectable drive strength.                                                              |  |  |  |

| 19         | IO8                | IO8                | DIO   | Programmable multi-purpose input/output, with selectable pull-up or pull-down resistors and selectable drive strength.                                                              |  |  |  |

| 20         | MISO               | MISO               | DIOPD | Serial peripheral interface (SPI):<br>Serial Data input in Master mode<br>Serial Data output in Slave mode                                                                          |  |  |  |

| 21         | VSSD               | VSSD               | S     | Ground reference for the digital circuitry.                                                                                                                                         |  |  |  |

| 22         | VDDD               | VDDD               | S     | Positive digital supply. VDDD provides the positive supply voltage to the digital circuitry and is internally connected to pin 13. The required supply voltage is $3.3V \pm 10\%$ . |  |  |  |

| 23         | S_N                | S_N                | DIOPU | Serial peripheral interface (SPI): Chip select                                                                                                                                      |  |  |  |

| 24         | MOSI               | MOSI               | DIOPD | Serial peripheral interface (SPI):<br>Serial Data output in Master mode<br>Serial Data input in Slave mode                                                                          |  |  |  |

| 25         | SC                 | SC                 | DIOPU | Serial peripheral interface (SPI): Serial clock                                                                                                                                     |  |  |  |

| 26         | n.c.               | IO9                | DIO   | Programmable multi-purpose input/output, with selectable pull-up or pull-down resistors and selectable drive strength.                                                              |  |  |  |

| 27         | n.c.               | IO10               | DIO   | Programmable multi-purpose input/output, with selectable pull-up or pull-down resistors and selectable drive strength.                                                              |  |  |  |

| 28         | n.c.               | IO11               | DIO   | Programmable multi-purpose input/output, with selectable pull-up or pull-down resistors and selectable drive strength.                                                              |  |  |  |

| 29         | TXD                | TXD                | DO    | Universal Asynchronous Receiver/Transmitter (UART1) serial transmit data output.                                                                                                    |  |  |  |

| 30         | RXD                | RXD                | DIPU  | Universal Asynchronous Receiver/Transmitter (UART1) serial receive data input.                                                                                                      |  |  |  |

| 31         | VDD_BAT            | VDD_BAT            | S     | Battery backup supply voltage input for the real time clock (RTC).                                                                                                                  |  |  |  |

| 32         | XIN                | XIN                | AI    | A 3.0 to 4.0MHz crystal may be connected across XIN and XOUT.<br>Alternatively, an external clock signal may be applied to XIN.                                                     |  |  |  |

| 33         | XOUT               | XOUT               | AO    | See XIN above, for the connection of a crystal. When an external clock is applied to XIN, XOUT is not connected.                                                                    |  |  |  |

| 34         | RES_N              | RES_N              |       | System reset active low.                                                                                                                                                            |  |  |  |

| 35         | n.c.               | n.c.               |       | Not connected                                                                                                                                                                       |  |  |  |

| Pin<br>No. | Pin Name<br>AS8267 | Pin Name<br>AS8268 | Туре | Description                          |  |  |  |

|------------|--------------------|--------------------|------|--------------------------------------|--|--|--|

| 36         | n.c.               | n.c.               |      | Not connected                        |  |  |  |

| 37         | LBP0               | LBP0               | AO   | _CD back-plane driver output signal. |  |  |  |

| 38         | LBP1               | LBP1               | AO   | LCD back-plane driver output signal. |  |  |  |

| 39         | LBP2               | LBP2               | AO   | LCD back-plane driver output signal. |  |  |  |

| 40         | LBP3               | LBP3               | AO   | LCD back-plane driver output signal. |  |  |  |

| 41         | LSD0               | LSD0               | AO   | LCD segment driver output signal.    |  |  |  |

| 42         | LSD1               | LSD1               | AO   | LCD segment driver output signal.    |  |  |  |

| 43         | LSD2               | LSD2               | AO   | LCD segment driver output signal.    |  |  |  |

| 44         | LSD3               | LSD3               | AO   | LCD segment driver output signal.    |  |  |  |

| 45         | LSD4               | LSD4               | AO   | LCD segment driver output signal.    |  |  |  |

| 46         | LSD5               | LSD5               | AO   | LCD segment driver output signal.    |  |  |  |

| 47         | LSD6               | LSD6               | AO   | LCD segment driver output signal.    |  |  |  |

| 48         | LSD7               | LSD7               | AO   | LCD segment driver output signal.    |  |  |  |

| 49         | LSD8               | LSD8               | AO   | LCD segment driver output signal.    |  |  |  |

| 50         | LSD9               | LSD9               | AO   | LCD segment driver output signal.    |  |  |  |

| 51         | LSD10              | LSD10              | AO   | LCD segment driver output signal.    |  |  |  |

| 52         | LSD11              | LSD11              | AO   | LCD segment driver output signal.    |  |  |  |

| 53         | LSD12              | LSD12              | AO   | LCD segment driver output signal.    |  |  |  |

| 54         | LSD13              | LSD13              | AO   | LCD segment driver output signal.    |  |  |  |

| 55         | LSD14              | LSD14              | AO   | LCD segment driver output signal.    |  |  |  |

| 56         | LSD15              | LSD15              | AO   | LCD segment driver output signal.    |  |  |  |

| 57         | LSD16              | LSD16              | AO   | LCD segment driver output signal.    |  |  |  |

| 58         | LSD17              | LSD17              | AO   | LCD segment driver output signal.    |  |  |  |

| 59         | LSD18              | LSD18              | AO   | LCD segment driver output signal.    |  |  |  |

| 60         | LSD19              | LSD19              | AO   | LCD segment driver output signal.    |  |  |  |

| 61         | n.c.               | LSD20              | AO   | LCD segment driver output signal.    |  |  |  |

| 62         | n.c.               | LSD21              | AO   | LCD segment driver output signal.    |  |  |  |

| 63         | n.c.               | LSD22              | AO   | LCD segment driver output signal.    |  |  |  |

| 64         | n.c.               | LSD23              | AO   | LCD segment driver output signal.    |  |  |  |

Note: Shaded pins above only available with AS8268 IC

| PIN Types: | S<br>AI<br>AO         | Supply pin<br>Analog Input pin<br>Analog Output pin                                                                                                  |  |  |  |  |  |

|------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|            | DIPU<br>DO            | Digital Input pin with pull-up resistor<br>Digital Output pin                                                                                        |  |  |  |  |  |

|            | DIO<br>DIOPD<br>DIOPU | Programmable Digital Input or Output pin<br>Digital Input or Output pin with pull-down resistor<br>Digital Input or Output pin with pull-up resistor |  |  |  |  |  |

# Table of Contents

| 1.  | Key Features                                                             | 1   |

|-----|--------------------------------------------------------------------------|-----|

| 2.  | General Description                                                      | 1   |

| 3.  | Typical Application Circuit                                              | 3   |

| 4.  | Pin Out                                                                  | 4   |

| 5.  | Pin Description                                                          |     |

| 6.  | Electrical Characteristics                                               |     |

| -   | 5.1 Absolute Maximum Ratings (Non-Operating)                             |     |

| 6.  | 6.2 Operating Conditions                                                 |     |

| 6.  | DC/AC Characteristics for Digital Inputs and Outputs                     | 9   |

| 6.  | 6.4 Electrical System Specification                                      | 10  |

| 7.  | Performance Graphs                                                       | 12  |

| 8.  | Detailed Functional Description                                          | 15  |

| 8.  | B.1 Energy Measurement Front End (Including DSP)                         |     |

| 8.  | 3.2 Temperature Sensor                                                   | 50  |

| 8.  | B.3 LCD Driver (LCDD)                                                    |     |

| -   | 8.4 Programmable Multi-Purpose I/Os (MPIO)                               |     |

| -   | 8.5 Serial Peripheral Interface (SPI)                                    |     |

|     | 3.6 External EEPROM Requirements                                         |     |

|     | <ul> <li>FLASH Memory</li> <li>8.8 8051 Microcontroller (MCU)</li> </ul> |     |

|     | 8.9 System Control (SCT)                                                 |     |

|     | 8.10 Serial Interface – UART1                                            |     |

| 9.  | Circuit Diagram                                                          |     |

| 10. | Parts List                                                               | 128 |

|     | Packaging                                                                |     |

|     | Product Ordering Guide                                                   |     |

|     | Collection of Formulae                                                   |     |

|     | Terminology                                                              |     |

|     | Revision                                                                 |     |

|     |                                                                          |     |

|     | Copyright                                                                |     |

| 17. | Disclaimer                                                               | 136 |

| 18. | Contact                                                                  | 136 |

# 6. Electrical Characteristics

# 6.1 Absolute Maximum Ratings (Non-Operating)

Stresses beyond the 'Absolute Maximum Ratings' may cause permanent damage to the AS8267 / AS8268 ICs. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under 'Operating Conditions' is not implied.

Caution: Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameter                | Symbol            | Min  | Max     | Unit | Notes                       |

|--------------------------|-------------------|------|---------|------|-----------------------------|

| DC supply voltage        | VDD               | -0.3 | +5.0    | V    |                             |

| Input pin voltage        | V <sub>in</sub>   | -0.3 | VDD+0.3 | V    |                             |

| Electrostatic discharge  | ESD               |      | 1000    | V    | Norm: MIL 883 E method 3015 |

| Storage temperature      | T <sub>strg</sub> | -55  | 125     | °C   |                             |

| Lead temperature profile | T <sub>lead</sub> |      |         |      | Norm: IPC/JEDEC-020C        |

| Humidity non-condensing  |                   | 5    | 85      | %    |                             |

# 6.2 Operating Conditions

| Parameter                       | Symbol            | Min  | Тур      | Max | Unit | Notes                      |

|---------------------------------|-------------------|------|----------|-----|------|----------------------------|

| Positive analog supply voltage  | VDDA              | 3.0  | 3.3      | 3.6 | V    |                            |

| Negative analog supply voltage  | VSSA              | 0    |          | 0   | V    |                            |

| Difference of supplies          | A - D             | -0.1 |          | 0.1 | V    | VDDA – VDDD<br>VSSA – VSSD |

| Positive digital supply voltage | VDDD              | 3.0  | 3.3      | 3.6 | V    |                            |

| Negative digital supply voltage | VSSD              | 0    |          | 0   | V    |                            |

| Battery supply voltage          | VDD_BAT           | 2.0  | 3.3      | 3.6 | V    |                            |

| Ambient temperature             | T <sub>amb</sub>  | -40  | 25       | 85  | °C   |                            |

| Supply current                  | I <sub>supp</sub> |      | 5        |     | mA   | Depending on MCU activity  |

| System clock frequency          | f <sub>osc</sub>  | 3.0  | 3.579545 | 4.0 | MHz  |                            |

# 6.3 DC/AC Characteristics for Digital Inputs and Outputs

| Parameter                | Symbol          | Min       | Тур | Max       | Unit | Notes                         |

|--------------------------|-----------------|-----------|-----|-----------|------|-------------------------------|

| High level input voltage | V <sub>IH</sub> | 0.7 x VDD |     |           | V    |                               |

| Low level input voltage  | VIL             |           |     | 0.3 x VDD | V    |                               |

| Low level input current  | IIL             | -100      |     | -15       | μA   | Tested at VDD=3.6V and Vin=0V |

### CMOS Input with Schmitt Trigger and Pull-up Resistor (RXD, RES\_N)

### CMOS Output (TXD)

| Parameter                 | Symbol          | Min | Тур | Max | Unit | Notes                           |

|---------------------------|-----------------|-----|-----|-----|------|---------------------------------|

| High level output voltage | V <sub>OH</sub> | 2.5 |     |     | V    | Tested at VDD=3.0V              |

| Low level output voltage  | V <sub>OL</sub> |     |     | 0.4 | V    | Tested at VDD=3.0V              |

| High level output current | I <sub>OH</sub> |     |     | 4   | mA   | Tested at VDD=3.0V and Vout=VOH |

| Low level output current  | I <sub>OL</sub> | -4  |     |     | mA   | Tested at VDD=3.0V and Vout=VOL |

### MPIO Inputs with Pull-up or Pull-down Resistor (SC, S\_N, MISO, MOSI)

| Parameter                 | Symbol          | Min     | Max     | Unit | Notes                                       |

|---------------------------|-----------------|---------|---------|------|---------------------------------------------|

| High level input voltage  | ViH             | 0.7*VDD |         | V    |                                             |

| Low level input voltage   | VIL             |         | 0.3*VDD | V    |                                             |

| High level output voltage | V <sub>OH</sub> | 2.5     |         | V    |                                             |

| Low level output voltage  | V <sub>OL</sub> |         | 0.4     | V    |                                             |

| High level output current | I <sub>ОН</sub> |         | 4       | mA   |                                             |

| Low level output current  | I <sub>OL</sub> | -4      |         | mA   |                                             |

| Pull-up                   |                 |         |         | •    | •                                           |

| High level input leakage  | I <sub>IH</sub> | -1      | 1       | μA   | Tested at VDD=Vin=3.6V                      |

| Low level input current   | IIL             | -100    | -15     | μA   | Tested at VDD=3.6V and Vin=0V;<br>'pull-up' |

| Pull-down                 |                 |         |         | •    | •                                           |

| High level input leakage  | I <sub>IH</sub> | 100     | 15      | μA   | Tested at VDD=Vin=3.6V; 'pull-down'         |

| Low level input current   | IIL             | -1      | 1       | μA   | Tested at VDD=3.6V and Vin=0V               |

Note:

$V_{\text{OH}},\,V_{\text{OL}},\,I_{\text{OH}}$  and  $I_{\text{OL}}$  are tested at VDD=3.0V.

$I_{OL}$  is tested at Vout=V<sub>OL</sub>

I<sub>OH</sub> is tested at Vout=V<sub>OH</sub>

### MPIO Inputs with Schmitt Trigger and Selectable Pull-up/Pull-down

| Parameter                | Symbol          | Min       | Тур | Max       | Unit | Notes                                           |

|--------------------------|-----------------|-----------|-----|-----------|------|-------------------------------------------------|

| High level input voltage | V <sub>IH</sub> | 0.7 x VDD |     |           | V    |                                                 |

| Low level input voltage  | V <sub>IL</sub> |           |     | 0.3 x VDD | V    |                                                 |

| High level input current | I <sub>IH</sub> | 15        |     | 100       | μA   | Tested at VDD=3.6V and Vin=3.6V;<br>'pull-down' |

| Low level input current  | IIL             | -100      |     | -15       | μA   | Tested at VDD=3.6V and Vin=0V;<br>'pull-up'     |

### MPIO Outputs with Programmable Drive Strength

| Parameter                 | Symbol          | Min | Тур | Max | Unit | Notes                                                    |

|---------------------------|-----------------|-----|-----|-----|------|----------------------------------------------------------|

| High level output current | V <sub>OH</sub> | 2.5 |     |     | V    | Tested at VDD=3.0V                                       |

| Low level output current  | V <sub>OL</sub> |     |     | 0.4 | V    | Tested at VDD=3.0V                                       |

| High level output current | I <sub>ОН</sub> |     |     | 4   | mA   | If '4mA' is selected. Tested at<br>VDD=3.0V and Vout=VOH |

| Low level output current  | I <sub>OL</sub> | -4  |     |     | mA   | If '4mA' is selected. Tested at<br>VDD=3.0V and Vout=VOL |

| High level output current | I <sub>OH</sub> |     |     | 8   | mA   | If '8mA' is selected. Tested at<br>VDD=3.0V and Vout=VOH |

| Low level output current  | I <sub>OL</sub> | -8  |     |     | mA   | If '8mA' is selected. Tested at<br>VDD=3.0V and Vout=VOL |

### LCDD Outputs

The Liquid Crystal display driver (LCDD) outputs are specified in the LCD Driver section of this data sheet.

# 6.4 Electrical System Specification

| Parameter                                  | Symbol                                | Min    | Тур | Max | Unit | Notes              |

|--------------------------------------------|---------------------------------------|--------|-----|-----|------|--------------------|

| Input Signals                              |                                       |        |     |     |      |                    |

| Voltage channel input voltage              | V <sub>VP</sub>                       |        | 100 | 212 | mVp  | Referenced to VSSA |

| Current channel input voltage<br>(Gain=4)  | V <sub>11P</sub>  ,  V <sub>12P</sub> |        | 150 | 212 | mVp  | Referenced to VSSA |

| Current channel input voltage<br>(Gain=16) | V <sub>11P</sub>  ,  V <sub>12P</sub> |        | 38  | 54  | mVp  | Referenced to VSSA |

| Current channel input voltage<br>(Gain=20) | V <sub>11P</sub>  ,  V <sub>12P</sub> |        | 30  | 42  | mVp  | Referenced to VSSA |

| Mains frequency                            | f <sub>mains</sub>                    | 45     |     | 65  | Hz   |                    |

| Dynamic range current                      | DR(I)                                 | 600:1  |     |     |      |                    |

| Dynamic range power                        | DR(P)                                 | 2000:1 |     |     |      |                    |

| Accuracy                                   |                                       | 0.1    |     |     | %    | Reading            |

| Error variation over dyn. range            | err(dr)                               |        |     | 0.2 | %    | 1)                 |

| Parameter                        | Symbol             | Min | Тур  | Max | Unit   | Notes                                  |

|----------------------------------|--------------------|-----|------|-----|--------|----------------------------------------|

| Error variation over temperature | err(temp)          |     |      | 0.5 | %      | Within operating temperature range, 1) |

| Error variation over cos(phi)    | err(cosphi)        |     |      | 0.5 | %      | From 1 to 0.5, 1)                      |

| Error variation with VDD         | err(VDD)           |     |      | 0.2 | %      | 1)                                     |

| Output pulse jitter              | J                  |     |      | 0.1 | %      | 2)                                     |

| Mains voltage                    | V <sub>mains</sub> |     |      | 264 | V(rms) | 240V + 10%, 3)                         |

| Measured current                 | I <sub>max</sub>   |     |      | 120 | A(rms) | 3)                                     |

| Measurement bandwidth            | BW                 |     | 1.75 |     | kHz    |                                        |

Notes:

1) Errors determined during energy measurement using a demo board and a reference meter with high accuracy (0.05%), which calculates the actual error.

Difference between largest and smallest error of 20 successive error samples; maximum meter constant: 1,600i/kWh; reference meter: 10,000 x DUT-meter-constant; measured at 5% lb, lb and I<sub>max</sub>.

3) What is used for system considerations/calculations.

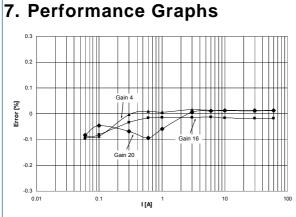

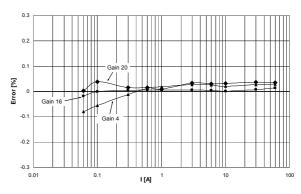

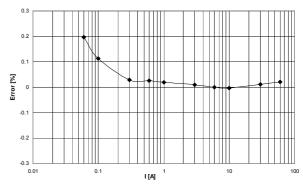

Error as a % of reading for gain setting 4, 16, 20 – Channel I1

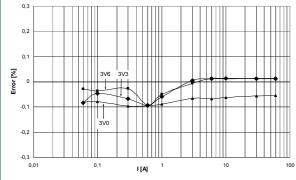

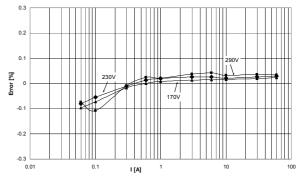

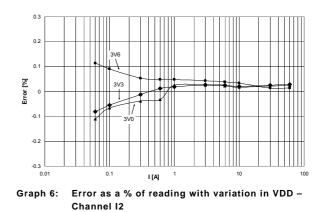

Graph 5: Error as a % of reading with variation in VDD – Channel I1

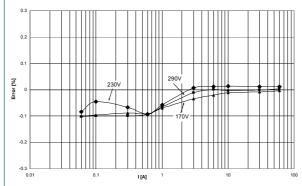

Graph 2: Error as a % of reading for gain setting 4, 16, 20 - Channel I2

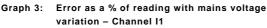

Graph 4: Error as a % of reading with mains voltage variation – Channel I2

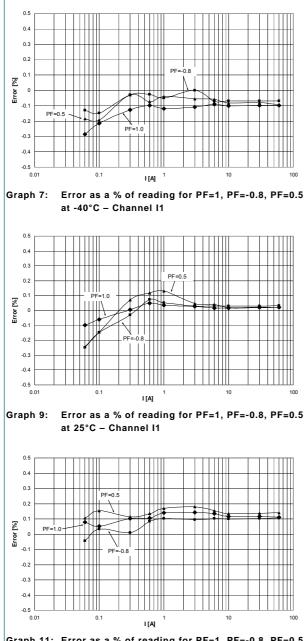

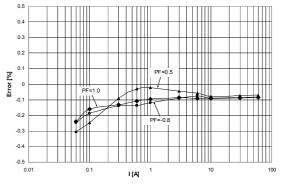

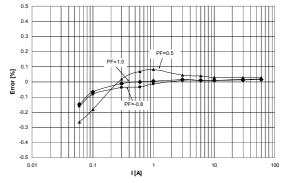

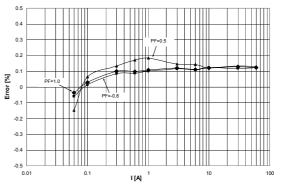

Graph 11: Error as a % of reading for PF=1, PF=-0.8, PF=0.5 at 85°C – Channel I1

Graph 8: Error as a % of reading for PF=1, PF=-0.8, PF=0.5 at -40°C - Channel I2

Graph 10: Error as a % of reading for PF=1, PF=-0.8, PF=0.5 at 25°C – Channel I2

Graph 12: Error as a % of reading for PF=1, PF=-0.8, PF=0.5 at 85°C – Channel I2

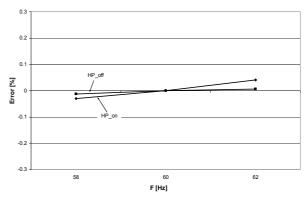

F [Hz]

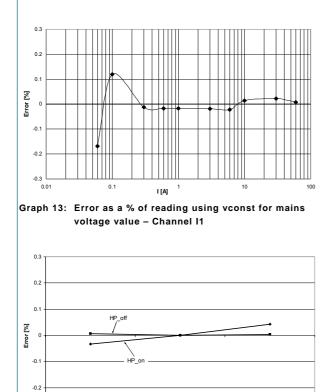

Graph 15: Error as a % of reading with variation in line

frequency - Channel I1

Graph 14: Error as a % of reading using vconst for mains voltage value – Channel I2

Graph 16: Error as a % of reading with variation in line frequency – Channel I2

Note:

-0.3

58

All measurements taken for the compilation of the graphs above were made using a reference meter design using the application circuit depicted on page 3 of this data sheet and incorporating the AS8267 / AS8268 integrated circuits.

62

For all graphical measurements, where the temperature was not specified, measurements were made at ambient (25 °C).

# 8. Detailed Functional Description

The AS8267 / AS8268 integrated circuits have a dedicated measurement front end, which is capable of measuring active and reactive energy, RMS mains voltage, RMS mains current as well as power factor. There are two completely separate differential current channel inputs, for measurement of both the Live and Neutral currents. The two current inputs may be connected to a shunt resistor (I1) and a current transformer (I2). Both current channels have programmable gains; thus it is possible to connect the shunt resistor to any of the two differential current inputs. The option to use two current transformers is also available. The AS8267 / AS8268 ICs may be programmed to accept either of the two measured currents for the energy calculation, or may be programmed to accept the larger of the two currents for the energy calculation.

The AS8267 / AS8268 ICs may also be used for conventional 1-phase single current measurement applications, where only the Live current is measured. In this case, the I2P and I2N pins are left unconnected and the second current channel modulator can be powered down.

The voltage channel input for measurement of the line voltage is also differential and is connected to a tap of a resistive divider of the line voltage. The resistive divider can be set to accommodate any line voltage standard (V<sub>mains</sub>) including 100V, 110V, 220V, 230V or 240V.

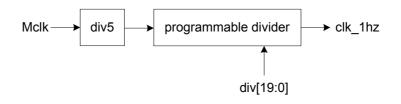

A 3.0 to 4.0MHz low power oscillator generates the system clock for the AS8267 / AS8268 ICs. The absolute clock frequency may be calibrated on-chip. A low power divider is used to generate a 1Hz clock for the on-chip real time clock/calendar (RTC). The supply voltage to the low power oscillator, the low power divider and the RTC may be buffered with an external battery in case of mains power drops or failures.

The integrated temperature sensor can be used to compensate for temperature drift of the quartz crystal to improve measurement accuracy.

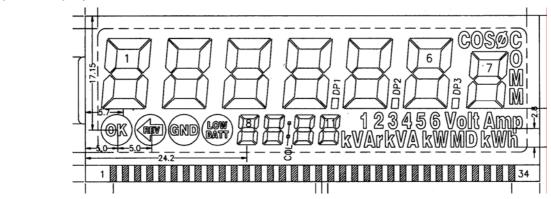

The LCD driver (LCDD) signals LSD0 ... LSD23 and LBP0 ... LBP3 can be directly connected to a liquid crystal display (LCD), which is used to display the various measured parameters. A total of 80 LCD segments may be driven by the AS8267 IC and 96 segments may be driven by the AS8268 IC.

A maximum of 12 programmable multi-purpose input/output (MPIO) pins are available for various meter functions, for example light-emitting diodes (LED) to signal energy consumption, energy direction, fault condition, etc. These I/O pins may also be programmed for use as bi-directional communication channels such as an optical interface or an additional Universal Asynchronous Receiver/Transmitter (UART2) Interface, should it so be required. The AS8267 has 9 x MPIO pins, while the AS8268 has 12 x MPIO pins.

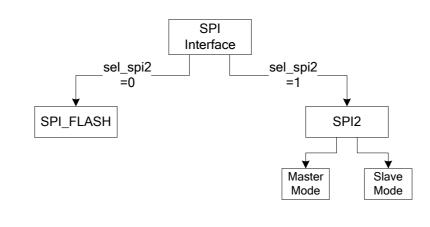

A dedicated Serial Peripheral Interface (SPI) which can be configured as master or slave is also provided. In master mode an external EEPROM (1kByte up to 32kByte) with a compatible serial peripheral interface can be connected if required.

In slave mode the interface allows direct access to the internal Flash memory.

The on-chip 8051 compatible microcontroller performs all the required calculations and enables the user to customize the input and output configuration of the meter. The microcontroller has a 1kB data memory, a square root calculation facility and a second UART (UART2) for debugging purposes.

The highly reliable 32kByte Flash memory allows storage of program and data. With the integrated security concept Flash Data can be protected against unauthorised access. The security concept offers password protection as well as an attack counter which blocks the Flash after five unauthorised attacks.

A programmable watchdog timer is provided to automatically initiate a system reset when a regular hold-off signal is not detected by the watchdog timer. The watchdog timer is an optional function which is software enabled.

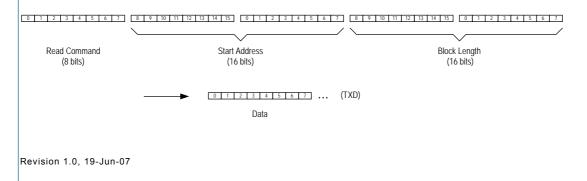

A dedicated serial Universal Asynchronous Receiver/Transmitter (UART1) Interface within the System Control is provided to communicate with the AS8267 / AS8268 ICs and perform all the required programming and reading of data, especially during the meter production process.

The AS8267 / AS8268 ICs supply voltages (2 x VDDD and VDDA) are typically 3.3 Volts. These supply voltages should be derived from the  $V_{mains}$  with the use of a standard voltage regulated power supply circuit.

An on-chip power supply monitor (PSM) ensures that a reset is generated independently of the supply voltage rise and fall times. Monitoring of the V<sub>mains</sub> is provided to ensure early power-down detection. A reset pin (RES\_N) is also available for external system reset. The RES\_N pin can be left unconnected if not required.

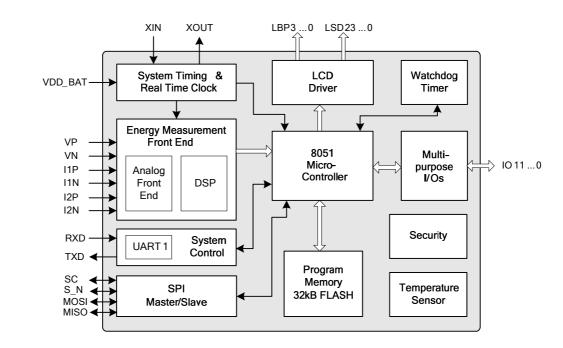

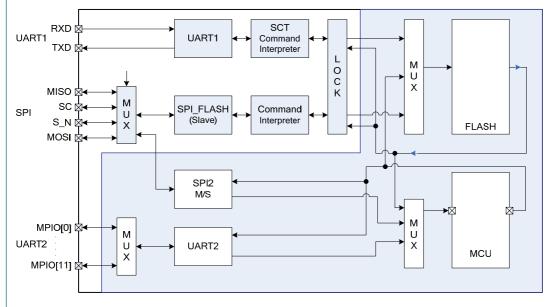

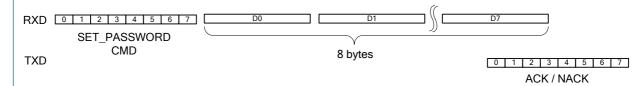

The individual functional elements of the AS8267 / AS8268 ICs, as well as the relationships between the various functional blocks are shown in the following block diagram. A detailed description of the AS8267 / AS8268 ICs system and the flexibility available to the kWh meter designer, through the system programmability is also described below:

Figure 2: AS8267 / AS8268 block diagram

## 8.1 Energy Measurement Front End (Including DSP)

The Energy Measurement Front End is made up of the analog front end and the digital signal processing block (DSP), which performs the active energy measurement calculations for the microcontroller.

The analog front end comprises of the three Sigma-Delta modulators for the sampling of the mains voltage, Line current and a second current channel, for the optional measurement of the Neutral current. Also included in the analog front end is the voltage reference, which provides the temperature stability to the Sigma-Delta modulators. Setting up for the optimum input conditions for the voltage and current channels is also described in this section.

The digital signal processing block (DSP) provides the filtering and processing of the output data from the sigma-delta modulators and ensures that the specified measurement accuracy is provided by the AS8267 / AS8268. The DSP offers programming of measurement parameters and provides for fast and efficient meter production calibration procedures.

A power supply monitor (PSM) ensures that a reset is generated independently of the rise and fall times of the supply voltage (VDD). The PSM is also described in this section.

### Analog Front End

The analog front end comprises of three identical Sigma-Delta modulators, which convert the differentially connected analog voltage and current inputs into digital signals. The two current inputs are gain adjustable to accommodate both directly connected or galvanically isolated current sensors.

The on-chip voltage reference (VREF) is the most important contributor to the accuracy of the AS8267 / AS8268 ICs due to it providing temperature stability to the circuit. Considering that the voltage and current signals are multiplied to derive the energy value, errors introduced prior to multiplication function results in errors being multiplied. Thus the introduction of errors into the voltage and the current channel inputs will result in a doubling of the percentage error after multiplication at the energy output.

The temperature coefficient of the VREF is specified at 15 ppm/K typical (30 ppm/K max.).

#### **Current Inputs for Energy Calculation**

The AS8267 / AS8268 ICs have 2 identical current inputs, I1P/I1N and I2P/I2N, for measurement of both the Live and Neutral currents. Either of the two current inputs may be selected for calculating the energy value.

These two differential current inputs are second order Sigma-Delta modulators, with each of the inputs being provided with selectable gains of 4, 16 and 20. The selectable gains are provided so that the AS8267 / AS8268 ICs may be easily adapted for use with either 2 current transformers or alternatively a shunt resistor and a current transformer for current sensing. The AS8267 / AS8268 ICs may also be used in a conventional single current configuration with either a current transformer or shunt resistor being used for current sensing.

The current input signal levels may be programmed by means of on-chip programmable gain settings. The required gain setting is selected as follows:

#### **Current Input Gain Settings**

| Gain      | Input Voltage                  | Comments                    |  |  |  |  |  |  |  |

|-----------|--------------------------------|-----------------------------|--|--|--|--|--|--|--|

| Current I | Current Inputs I1P, I1N        |                             |  |  |  |  |  |  |  |

| 20        | $-30mV \le V_{I1P} \le 30mV$   | Shunt mode; default setting |  |  |  |  |  |  |  |

| 16        | $-38mV \le V_{I1P} \le 38mV$   | CT mode or shunt mode       |  |  |  |  |  |  |  |

| 4         | $-150mV \le V_{I1P} \le 150mV$ | CT mode                     |  |  |  |  |  |  |  |

| Current I | nputs I2P, I2N                 |                             |  |  |  |  |  |  |  |

| 20        | $-30mV \le V_{I2P} \le 30mV$   | Shunt mode                  |  |  |  |  |  |  |  |

| 16        | -38mV≤V <sub>I2P</sub> ≤38mV   | CT mode or shunt mode       |  |  |  |  |  |  |  |

| 4         | $-150mV \le V_{12P} \le 150mV$ | CT mode; default setting    |  |  |  |  |  |  |  |

Notes:

1) Refer to the Settings Register (SREG) in the DSP section for programming of the Gain Settings.

For optimum operating conditions, the input signal at the Maximum Current ( $I_{max}$ ) condition should be set at ±30mVp, when the Gain = 20, or ±150mVp, when the Gain = 4.

The default Gain, the AS8267 / AS8268 ICs current input gain settings without any programming required, is Gain = 20 for the I1 input and Gain = 4 for the I2 input.

The value of an ideal shunt resistor, may be calculated as follows:

Assuming an I<sub>max</sub> rating of 60A (rms)  $\rightarrow$  84.85A (peak), then a shunt value of 350µ $\Omega$  would be suitable.

$$R_{shunt} = \frac{30mV_p}{84.85A_p} = 354\mu\Omega$$

thus a standard 350 $\mu\Omega$  shunt resistor may be selected.

The mains currents are sampled at 3.4956kHz, assuming that the recommended crystal oscillator frequency of 3.5795MHz, is used.

The current transformer(s) must be terminated with a voltage setting resistor ( $R_{VS}$ ) to ensure the optimum voltage input level to the current input(s) of the AS8267 / AS8268 ICs. The value of  $R_{VS}$  is calculated as follows:

$$R_{VS} = \frac{V_{in(p)}}{I_L \sqrt{2}}$$

where  $I_L$  = CT RMS secondary current at rated conditions ( $V_{mains}$ ;  $I_{max}$ )

$V_{in(p)}$  = The peak input voltage to the IC at rated conditions ( $V_{mains}$ ;  $I_{max}$ ). For example, if Gain = 4,  $V_{in(p)}$  should be set at 150mVpeak.

Example: A current transformer is specified at 60A/24mA and the Gain = 4:

$$R_{VS} = \frac{V_{in(p)}}{I_L \sqrt{2}} = \frac{150 \text{mV}}{24 \text{mA} \sqrt{2}} = 4.42 \Omega \Rightarrow 4.3 \Omega \qquad \text{thus a } 4.3 \Omega \text{ Burden resistor may be selected}$$

#### Voltage Input for Energy Calculation

The voltage channel input consisting of inputs VP and VN which are differential, with VP connected to the tap of a resistor divider circuit of the line voltage and VN connected to VSSA. For optimum operating conditions, the input signal at VP should be set at 100mVp for the rated voltage condition.

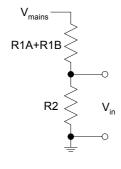

The resistor values for an ideal voltage divider may be calculated as follows:

Assuming a V<sub>mains</sub> of 230V (rms)  $\rightarrow$  325V (peak) and R2 = 470 $\Omega$  (according to the voltage divider shown below), the value of R1A+R1B may be calculated as follows:

$$R1A + R1B = R2 \times \frac{(V_{mains} - V_{in(P)})}{V_{in(P)}} = 470\Omega \times \frac{325V - 100mV}{100mV} = 1.53M\Omega$$

thus R1A = 820k $\Omega$  and R1B = 750k $\Omega$  resistors may be selected.

The mains voltage is also sampled at 3.4956kHz, assuming that the recommended crystal oscillator frequency of 3.5795MHz is used.

#### Digital Signal Processing Block (DSP)

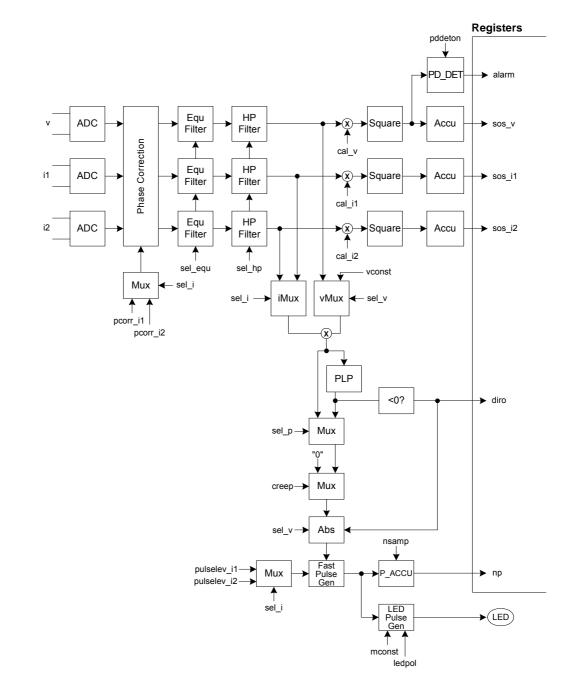

The digital signal processing (DSP) block provides the signal processing required to ensure that the specified measured accuracy is performed and that the microcontroller (MCU) is provided with the appropriate data and protocol to perform all the required meter functions. For the description below, please refer to the following block diagram (Figure 3).

The DSP makes allowance for phase correction of the two current channels (i1 and i2) within the Sinc<sup>3</sup> decimation filters in the phase correction block. The applicable phase correction setting (pcorr\_i1 or pcorr\_i2) is selected (sel\_i), depending upon which current (i1 or i2) is being used for the power calculation.

The equalization filters on the voltage and current channels which may be by-passed (sel\_equ), correct for the attenuation introduced by the decimation filters at the edge of the input frequency band, while the high pass filters, which may also be by-passed (sel\_hp), eliminate any DC offsets introduced into the input channels.

Independent calibration of the voltage  $(cal_v)$  and current signals  $(cal_i1 \text{ and } cal_i2)$  is done after the voltage and current signals are provided for power calculation. This ensures that calibration of the voltage  $(sos_v)$ , current channel 1  $(sos_i1)$ , current channel 2  $(sos_i2)$  has no influence on the power (np) calibration.

The iMux (current multiplexer) allows the selection of the applicable current for power calculation (sel\_i), while the vMux (voltage multiplexer) allows the selection of either the mains voltage data, or a constant voltage value, vconst (sel\_v). The multiplication of the appropriately selected voltage and current signals is then performed.

After multiplication, the next multiplexer (sel\_p) enables the selection of either instantaneous power or real power, which is derived through low pass filtering, PLP. The direction indicator output (diro) is derived from the output of the power low pass filter (PLP).

The following multiplexer (creep) allows the selection of the power signal, or blocks the power signal, depending on the required anti-creep and starting current thresholds, which may be set in the microcontroller.

Only when constant voltage value (vconst) is selected by the vMux (voltage multiplexer) or when diro=1, it is necessary to derive the absolute power value, for measurement (Abs).

The first pulse generator (Fast Pulse Gen) produces fast internal pulses, with the number of pulses being proportional to the measured energy. The multiplexer enables the selection of the appropriate pulse level (pulselev\_i1 or pulselev\_i2) depending on the current being used for energy measurement (sel\_i). The output of the Fast Pulse Gen is always directly proportional to the LED pulse output, generated in the LED Pulse Gen. The LED output pulses rate is selectable (mconst). The polarity of the LED output pulses is also selectable (ledpol).

To ensure that the power data transferred to the microcontroller (MCU) is identical to that of the LED pulses, the power accumulator (P\_ACCU) counts the pulses generated by the Fast Pulse Gen. After a defined number of sampling periods (nsamp), an interrupt is sent to the MCU, for the MCU to collect the accumulated energy data.

Revision 1.0, 19-Jun-07

#### **Phase Correction**

The DSP provides phase correction of the two current channels (i1 and i2) by means of the Sinc<sup>3</sup> decimation filters in the phase correction block. Only one of the phase correction settings (pcorr\_i1 or pcorr\_i2) is valid at a time, depending on which current (i1 or i2) has been selected for the power calculation (sel\_i).

The phase correction step size is dependent upon the main oscillator frequency selected ( $f_{osc}$ ) and the mains frequency ( $f_{mains}$ ). Assuming a 3.579545MHz crystal oscillator frequency and 50Hz mains frequency, the phase can be corrected in steps of 2.41' or 0.04 degrees.

|       |       | Phase Correction<br>[unit(s)] |       |       |       |       |       |       |      |

|-------|-------|-------------------------------|-------|-------|-------|-------|-------|-------|------|

| Bit 8 | Bit 7 | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |      |

| 0     | 1     | 1                             | 1     | 1     | 1     | 1     | 1     | 1     | 255  |

| 0     | 1     | 1                             | 1     | 1     | 1     | 1     | 1     | 0     | 254  |

|       |       |                               |       |       |       |       |       |       |      |

| 0     | 0     | 1                             | 1     | 1     | 1     | 1     | 1     | 1     | 127  |

| 0     | 0     | 1                             | 1     | 1     | 1     | 1     | 1     | 0     | 126  |

|       |       |                               |       |       |       |       |       |       |      |

| 0     | 0     | 0                             | 0     | 0     | 0     | 0     | 1     | 0     | 2    |

| 0     | 0     | 0                             | 0     | 0     | 0     | 0     | 0     | 1     | 1    |

| 0     | 0     | 0                             | 0     | 0     | 0     | 0     | 0     | 0     | 0    |

| 1     | 1     | 1                             | 1     | 1     | 1     | 1     | 1     | 1     | -1   |

| 1     | 1     | 1                             | 1     | 1     | 1     | 1     | 1     | 0     | -2   |

|       |       |                               |       |       |       |       |       |       |      |

| 1     | 1     | 0                             | 0     | 0     | 0     | 0     | 0     | 1     | -127 |

| 1     | 1     | 0                             | 0     | 0     | 0     | 0     | 0     | 0     | -128 |

|       |       |                               |       |       |       |       |       |       |      |

| 1     | 0     | 0                             | 0     | 0     | 0     | 0     | 0     | 1     | -255 |

| 1     | 0     | 0                             | 0     | 0     | 0     | 0     | 0     | 0     | -256 |

One 'unit' equals a certain phase shift related to the mains frequency:

1 unit =

$$360^{\circ} \times \frac{f_{mains}}{f_{osc} / 8}$$

Phase Correction

$$[^{\circ}] =$$

#units × 360° ×  $\frac{f_{mains}}{f_{osc} / 8}$

Example:

$$1\,unit=360^\circ \times \frac{f_{mains}}{f_{osc}\:/\:8}=0.04023^\circ=2.41^\circ$$

255 units = 255 x 0.04023° = 10.26°

where  $f_{\text{mains}}$  is the mains frequency and  $f_{\text{OSC}}$  is the oscillator frequency.

#### Calculating Phase Correction Factors

The measured phase\_error in percentage is defined by the following formula

phase \_ error =

$$\frac{\cos(60^\circ + \text{phase } \text{_shift}) - \cos(60^\circ)}{\cos(60^\circ)} \times 100$$

[%]

while the phase\_shift in degrees, is calculated as follows:

phase shift =

$$\operatorname{arccos}\left[\left(1 + \frac{\operatorname{phase}\operatorname{error}[\%]}{100}\right) \times \cos(60^{\circ})\right] - 60^{\circ}$$

phase\_correction= -phase\_shift

The required phase correction factor can be determined from error measurements with a power factor (PF) less than 1.

Assuming that at PF = 1 the meter has been calibrated and the error is approximately 0 for  $I_{cal}$  (calibration current), the PF is reduced and the effect of phase differences results in an increased error ('phase\_error').

Example: The phase\_error at PF = 0.5 ( $\varphi$  = 60°) is measured to be 9.2 %.

The related phase shift can be calculated using the following formula:

phase shift = arc cos

$$\left( \left( 1 + \frac{\text{phase} - \text{error}[\%]}{100} \right) \times \cos 60^{\circ} \right) - 60^{\circ}$$

where the phase\_error is the measured error in percentage and  $\cos \Phi$  is the phase angle.

For phase\_error = 9.2[%] the phase\_shift is  $-3.0^{\circ}$  and therefore the phase correction is  $3.0^{\circ}$ .

If  $f_{osc}$  = 3.579545MHz and  $f_{mains}$  = 50Hz, one phase correction unit represents 2.41', which is 0.04023°.

Thus the phase correction factor must be set to

$$\frac{3.0^{\circ}}{0.04023^{\circ}} = 74.57 \text{ units}$$

= 75 units.

The pcorr register has to be set to 4Bh.

#### **Equalization Filters**

The equalization filters in the voltage and current channels correct for the attenuation effects introduced by the decimation filters around the frequency band limit. The resulting transfer curve after the equalization filter has approximately 0dB attenuation over the entire frequency band.

The equalization filters may be by-passed (sel\_equ), if required.

#### **High-Pass Filters**

The high pass filters in the voltage and current channels, with corner frequencies of <10Hz, correct for DC offsets introduced into the input channels.

Each of the voltage and current channels has a separate high pass filter in order to avoid any phase shift being introduced between the voltage and the two current channels.

The high pass filters may also be by-passed (sel\_hp), if so desired.

Corner frequency: <10Hz

### **RMS** Calculations

The DSP provides the voltage and current channel data in 'sum-of-squares' format. To calculate RMS values from the voltage (sos\_v) and current (sos\_i1 and sos\_i2), the following formula should be applied for the voltage and current respectively:

$$V_{rms} = \sqrt{\frac{1}{nsamp} \sum_{i=1}^{nsamp} V_i^2} , \qquad \text{where } \sum_{i=1}^{nsamp} V_i^2 \text{ is the sos_v value}$$

$$I_{rms} = \sqrt{\frac{1}{nsamp} \sum_{i=1}^{nsamp} I_i^2} , \qquad \text{where } \sum_{i=1}^{nsamp} I_i^2 \text{ is the sos_i value}$$

nsamp should be selected in order to achieve coherent sampling as close as possible:

e.g. f<sub>s</sub> = 3.4956kHz (f<sub>osc</sub> = 3.579545MHz)  $\Rightarrow$  nsamp = 3496 should be selected if the MCU has to be interrupted every 1 second.

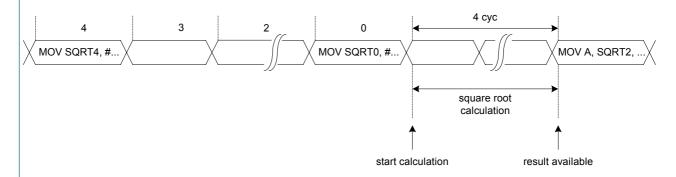

Refer to Squareroot Block (SQRT) for a detailed description of the programming sequence of the squareroot input operand.

#### Calibration of V and I Channels

The single channel data may be corrected with a 16-bit calibration value. The calibration range is [1 LSB; 2 - 1 LSB], step size (1 LSB):  $3.052 \times 10^{-5}$ .

| Calibration Register Setting | Value                 |

|------------------------------|-----------------------|

| 0000h                        | 0                     |

| 0001h                        | 0.00003052 (= 1 LSB)  |

|                              |                       |

| 2000h                        | 0.25                  |

|                              |                       |

| 4000h                        | 0.5                   |

|                              |                       |

| 8000h                        | 1.0                   |

|                              |                       |

| FFFFh                        | 1.99996948 (2 – 1LSB) |

The V and I channel RMS calculation and calibration is described below (V and I channel are identical, thus only the I channel is shown):

The ideal values after RMS calculations of voltage and current are:

RMS\_V(ideal) = 479(rms) RMS\_I(ideal) = 292,110(rms)

These values assume ideal input conditions with  $V_{in}$  = 100mVp at rated conditions and  $I_{in}$  = 30mVp (Gain = 20) at rated conditions.

Due to non-ideal components a different RMS value is calculated: RMS\_I(actual). From this, the required calibration factor is calculated using the following formula:

$cal_i = \frac{RMS_l(ideal)}{RMS_l(actual)}$

The following formula calculates the actual value to be programmed into the calibration registers (cal\_v; cal\_i1; cal\_i2):

$cal_i(reg) = hex(round(cal_i \times 32,768))$

e.g.

RMS\_I(ideal) = 292,110 at 40A

$I_{cal} = 10A \rightarrow RMS_1(ideal) = \frac{292,110}{4} = 73,027 \text{ at } 10A$

$I_{actual} = 9.2A \rightarrow RMS_I(actual) = 67,185$

Revision 1.0, 19-Jun-07

$$cal_i(reg) = hex\left(round\left(\frac{73,027}{67,185} \times 32,768\right)\right)$$

= hex(round (35,617.31))

= hex(35,617)

= 8B21h

#### Constant Voltage Register (vconst)

The vconst registers (9334h and 9335h) provide a predefined voltage value that can be used for calculating energy when the  $V_{mains}$  is not available.

The default value of vconst is 2877 (0B3Dh) which translates into an equivalent V<sub>mains</sub> value of 311V.

The energy is calculated using vconst and the selected current (i1 or i2) when sel\_v in the SREG/Select register is set to '1'.

The vconst value may be calculated according to the formula:

vconst = RMS \_ V ×  $\sqrt{2}$  ×  $\pi$

Example: RMS\_V = 479  $\Rightarrow$  vconst = 479 ×  $\sqrt{2}$  ×  $\pi$ = 2,128 (Once the voltage channel has been calibrated, 479 is the typical value when  $V_{\text{mains}}$  = 230V)

Note: When vconst is used for the calculation of energy, sel\_p must be set to '0'.

#### Low Pass Filter for Real Power (PLP)

When the instantaneous power is low pass filtered the result is practically a DC value for the power, which is termed real power. It is generally preferred to use real power to generate pulses for the calibration, as the duration between pulses is more constant (pulse jitter).

Corner frequency: 18.6Hz

The low pass filter ensures that the power output pulse jitter is minimised.

#### **Direction Indicator (DIRO)**

The direction indicator (DIRO) situated in the Status Register (Bit 4) defines the direction of the measured power. The direction is determined by the phase relationship between the Mains voltage and selected Mains current (i1 or i2).

When bit 4 in the Status Register is '0', the Mains voltage and selected Mains current are in phase, thus indicating positive energy flow. When bit 4 in the Status Register is '1', the Mains voltage and the selected Mains current have a phase reversal, indicating negative energy flow. The energy calculation (np) is generated

from positive energy, thus when DIRO = 1, the negative energy is converted to positive energy by the 'Abs' block shown in Figure 3: AFE block diagram.

Should the meter application require unidirectional energy measurement, the MCU can separately derive both the positive and negative energy values, depending on the status of the DIRO bit.

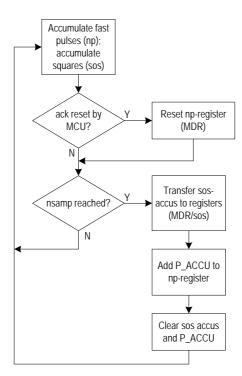

#### Accumulator for Real Power (P\_ACCU)

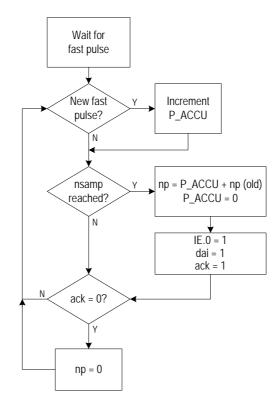

To ensure that the power information transferred to the MCU is identical to that of the LED pulses, the P\_ACCU counts the pulses generated by Fast Pulse Gen. After 'nsamp' (nyquist) sampling periods an interrupt is sent to the MCU requesting to fetch the new energy information. (Interrupt line 'IE.0' goes high and the 'data available interrupt' (dai) flag in the SREG/Status register is set). The 'ack' bit in the SREG/Status register is also set to 1. If the MCU takes the energy information, it has to reset the 'ack' bit signalling that the energy information has been taken. If the 'ack' bit is not reset the P\_ACCU will add the 'old' energy information to the 'new' energy information accumulated in the following cycle.

In any event, the MCU must reset the dai flag in order to clear the interrupt.

Note: The above flow chart assumes that the dai flag is always reset in time before the next interrupt is generated.

#### **Pulse Generation**

Two pulse generators are provided to ensure that virtually any LED pulse rate output can be programmed for display and calibration purposes. The first pulse generator (Fast Pulse Gen) produces fast internal pulses. These fast pulses are accumulated in the power accumulator (P\_ACCU) for energy data transfer to the MCU.

The second pulse generator (LED Pulse Gen) produces the LED output pulses (meter constant) from the fast internal pulses. This type of data interface ensures that the MCU receives exactly the same energy information as is displayed by the LED pulses.

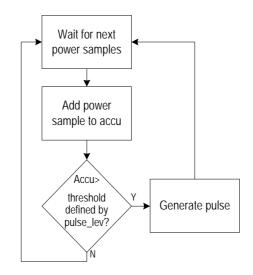

In case of 'creep', the power samples to be added will be set to 0. The following flow chart shows the basic flow diagram for pulse generation:

The Fast Pulse Gen output pulse rate always has the same relationship with the LED pulse rate defined by mconst. Only if LED is calibrated to a meter constant different from those provided in the mconst table, will the fast internal pulse rate be different.

Formula for fast internal pulse rate (PRint):

$$PR_{int} = 204,800 \times \frac{T \operatorname{argetPulseRate}}{mconst} [i / kWh]$$

$$1i = \frac{1,000 \times 3,600}{PR_{int}} [Ws]$$

where mconst is the meter constant.

when 1i is one impulse representing an energy equivalent.

e.g.

TargetPulseRate = mconst = 3200i/kWh

$PR_{int} = 204,800 \times 1 \text{ [i/kWh]}$  $1i = \frac{1,000 \times 3,600}{204,800} = 17.58 \text{ [Ws]}$

#### Active Power Calibration (Pulse\_lev)

This paragraph describes how the active power measurement within the AS8267 / AS8268 ICs is calibrated. The parameter Pulse\_lev is the main parameter which determines the output frequency of the Fast Pulse Gen. This frequency relates to the measured power and is the basis from which the output pulse rate is derived.

Revision 1.0, 19-Jun-07

Prior to system calibration, the appropriate value for the parameter Pulse\_lev must be calculated to produce the required output pulse rate. The calibration exercise must accommodate all non-idealities that are present in the meter system.

The Pulse\_lev is specified such that a typical pulse rate of 204,800i/kWh can be achieved. During energy pulse calibration the correct Pulse\_lev is determined in order to get the desired pulse rate. The default value for Pulse\_lev is defined for  $I_{max}$ =40A and  $V_{mains}$ =230V.

Default Pulse\_lev: 570,950 (Pulse\_lev(default))

Pulse \_lev(ideal) =  $\frac{230V}{V} \times \frac{40A}{L} \times Pulse _lev(default)$

Example for Pulse\_lev calculations:

|                        | v <sub>mains</sub> I <sub>ma</sub>         | х                 |                 |

|------------------------|--------------------------------------------|-------------------|-----------------|

| V <sub>mains</sub> (V) | I <sub>max</sub> (A)                       | Pulse_lev (ideal) | Notes           |

| 230                    | 100                                        | 228,380           |                 |

| 230                    | 80                                         | 285,475           |                 |

| 230                    | 60                                         | 380,633           |                 |

| 230                    | 40                                         | 570,950           | Default setting |

| 230                    | 20                                         | 1,141,900         |                 |

| 230                    | 10                                         | 2,283,800         |                 |

| 240                    | 100                                        | 218,864           |                 |

| 240                    | 80                                         | 273,580           |                 |

| 240                    | 60                                         | 364,774           |                 |

| 240                    | 40                                         | 547,160           |                 |

| 240                    | 20                                         | 1,094,321         |                 |

| 240                    | 10                                         | 2,188,642         |                 |

| Pulse_lev(ideal) =     | 230/V <sub>mains</sub> x 40/I <sub>n</sub> | nax x 570,950     | •               |

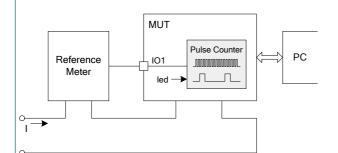

#### **Comparison Calibration Method**

The most common calibration method is the comparison of energy reading of the meter under test (MUT) against a standard or reference meter. Normally, the standard, or reference meter has a considerably higher pulse rate than the meter under calibration. Reference meter output pulses are then counted between consecutive led pulses. To facilitate the calibration procedure, a pulse counter is provided in the MPIO block. In this case, the absolute calibration time and the calibration current are not relevant for the calibration cycle. The basic calibration setup is shown below:

#### Figure 4: Basic setup for comparison calibration method (using IO1 as example input)

Note: An I/O used as push-button input can be used for the input of the reference meter pulses during calibration.

The standard or reference meter pulses are counted between two pulses from the meter to be calibrated. Ideally the sum of the pulses would exactly be the ratio between standard meter or reference pulse rate and the pulse rate of the meter under test. From the deviation the corrected Pulse\_lev may be calculated.

Pulse \_lev(corrected) = Pulse \_lev(ideal)  $\times \frac{Ni}{Na}$

where Ni is the ideal number of pulses and Na is the actual number of pulses (PCNT register in MPIO). The actual number of pulses is available in the pulse count register (PCNT).

The ideal number of pulses Ni is the ratio between the pulse rates of the reference meter and the meter under test, which is always >1. The formula for Ni is as follows:

$$Ni = \frac{PR(ref)}{LED Pulse Rate(mconst)}$$

, where PR(ref) is the reference meter constant.

The Pulse\_lev (ideal) is calculated using the following formula:

$$Pulse\_lev(ideal) = \frac{230V}{V_{mains}} \times \frac{40A}{I_{max}} \times Pulse\_lev(default)$$

#### Example

The reference meter has a pulse rate, which is 10,000 times greater than the pulse rate of the AS8267 / AS8268 LED output.

LED Pulse Rate = 3,200i/kWh PR(ref) = 3,200 x 10,000 ⇒ Ni = 10,000

During a calibration cycle we measure 11,000 pulses between two LED pulses.

$\Rightarrow Na = 11,000$  Assuming a meter with V<sub>mains</sub> = 230V I<sub>max</sub> = 60A

Revision 1.0, 19-Jun-07

$$Pulse\_lev(ideal) = \frac{230V}{230V} \times \frac{40A}{60A} \times 570,950$$

= 380,633

Pulse\_lev (corrected) =

$$380,633 \times \frac{10,000}{11,000} = 346,030$$

### LED Meter Constant Selection (mconst, 9330h)

The LED pulses are derived directly from the fast internal pulses (204,800i/kWh). The 'mconst' register in SREG specifies the LED pulse rate:

| MSB |   |   |   |           |           |           | LSB       |

|-----|---|---|---|-----------|-----------|-----------|-----------|

| -   | - | - | - | mconst[3] | mconst[2] | mconst[1] | mconst[0] |

| Bit             | Symbol      | Function |      |      |      |      |                |

|-----------------|-------------|----------|------|------|------|------|----------------|

| <u>Біі</u><br>7 | Symbol<br>- | Not used |      |      |      |      |                |

| 6               | _           | Not used |      |      |      |      |                |

| 5               | _           | Not used |      |      |      |      |                |

| 4               |             | Not used |      |      |      |      |                |

|                 | -           |          |      | DKO  |      | DKO  |                |

| 3               | mconst[3]   |          | Bit3 | Bit2 | Bit1 | Bit0 | LED Pulse Rate |

|                 |             |          | 0    | 0    | 0    | 0    | 204,800        |

|                 |             |          | 0    | 0    | 0    | 1    | 102,400        |

|                 |             |          | 0    | 0    | 1    | 0    | 51,200         |

| 2               | mconst[2]   |          | 0    | 0    | 1    | 1    | 25,600         |

|                 |             |          | 0    | 1    | 0    | 0    | 12,800         |

|                 |             |          | 0    | 1    | 0    | 1    | 6,400          |

|                 |             |          | 0    | 1    | 1    | 0    | 3,200          |

| 1               | mconst[1]   |          | 0    | 1    | 1    | 1    | 1,600          |

|                 |             |          | 1    | 0    | 0    | 0    | 800            |

|                 |             |          | 1    | 0    | 0    | 1    | 400            |

| 0               | mconst[0]   | 1        | 1    | 0    | 1    | 0    | 200            |

|                 |             |          | 1    | 0    | 1    | 1    | 100            |

|                 |             |          | 1    | 1    | Х    | Х    | 100            |

If the target meter constant is different from one of the selectable (mconst) meter constants defined above:

e.g. 1,000i/kWh (Target Pulse Rate)

The same formula  $Ni = \frac{PR(ref)}{LEDPulseRate(mconst)}$  can be used, but Ni is calculated using the Target Pulse Rate:

$$Ni = \frac{PR(ref)}{T \operatorname{arg} et \operatorname{Pulse} Rate}$$

(Important: Select a pulse rate which is close to mconst, for the Target Pulse Rate, so that the Pulse\_lev stays within reasonable limits.)

After this calibration the energy equivalent of 1 fast pulse (1i) is different!

Standard: internal pulse rate: 204,800i/klWh

$$\Rightarrow$$

1i =  $\frac{1,000 \times 3,600 [Ws]}{204,800}$  = 17.58Ws

When a special pulse rate is required, the following formula applies:

$$\Rightarrow 1i = \frac{1,000 \times 3,600}{204,800} \times \frac{\text{LED PulseRate}}{\text{T arg etPulseRate}} [Ws]$$

Example:

Assuming a pulse rate of 1,000 is required:

1,600 → 204,800 1,000 → 204,800 x 1,000/1,600

$$\Rightarrow 1i = \frac{1,000 \times 3,600 [Ws]}{204,800 \times 1,000 / 1,600} = 28.13 Ws$$

#### Mains Current Leads/Lags Mains Voltage

The i\_lead flag in the SREG/Status register determines if the mains current leads the mains voltage or lags the mains voltage. The data is provided for reactive power calculation, to establish if the measured power is capacitive or inductive.

#### LED Output Timing

The pulses on the LED output indicate the amount of energy that has been consumed over a certain period of time. Each pulse has an equivalent that can be set in the SREG/mconst register exactly. The unit is impulses per kWh (i/kWh).

This output may be used for calibration.

The polarity of the LED pulses may be selected via the ledpol bit in the SREG/Select Register for either positive or negative going pulses.

#### Timing Diagram

#### **Timing Parameters**

| Parameter   | Symbol | Min | Тур | Max | Unit | Notes                                                                                                    |

|-------------|--------|-----|-----|-----|------|----------------------------------------------------------------------------------------------------------|

| Pulse width | t1     |     | 80  |     | ms   | 50% duty cycle is enabled when the LED<br>period is less than 160ms. For mconst=0,<br>t1 will be 17.9μs. |

#### Register Interface to MCU

One register block contains the data for the Meter Data Register (MDR) and the Settings Register (SREG), hence only one interface to the MCU is required.

#### Meter Data Register (MDR)

The meter data register is updated after 'nsamp' samples. Then an interrupt is issued to the MCU, which may take the energy data and process them further on. When an interrupt is generated the 'ack' bit in the SREG/Status register is set. If the MCU takes the data, it has to reset the 'ack' bit.

If the 'ack' bit has not been reset by the MCU when a new set of data is ready, the previous np value will be added to the new one.

In any case the dai flag in the SREG/Status register must be reset in order to clear the interrupt.

The following table shows the data which is available in the MDR:

| Register Name   | Address | Reset Value | Description                                                                                                                                 |

|-----------------|---------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| samptoend[7:0]  | 9300h   | FFh         | Indicates how many samples are left (until nsamp), before the next                                                                          |

| samptoend[15:8] | 9301h   | FFh         | interrupt is generated. Using this information the MCU can<br>determine if it still has time to transfer the MDR data to the MCU<br>memory. |

| np[7:0]         | 9302h   | 00h         |                                                                                                                                             |

| np[15:8]        | 9303h   | 00h         | number of fast pulses, equivalent to energy information                                                                                     |

| np[23:16]       | 9304h   | 00h         | accumulated during nsamp samples                                                                                                            |

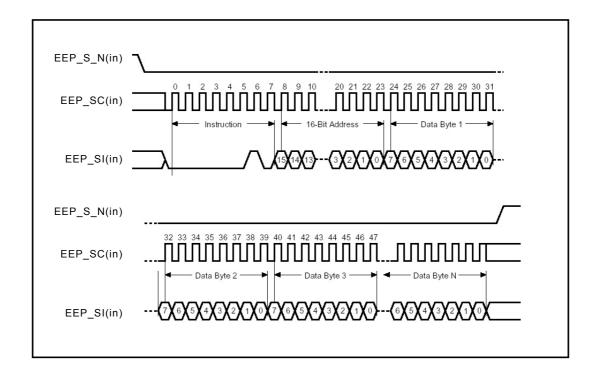

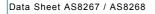

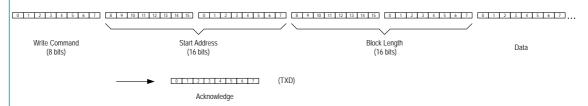

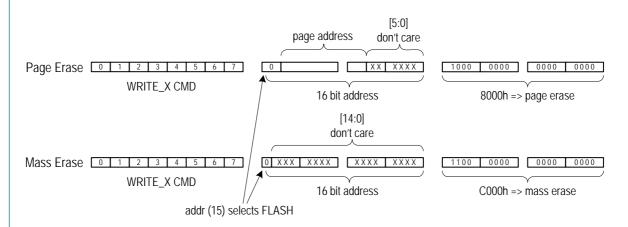

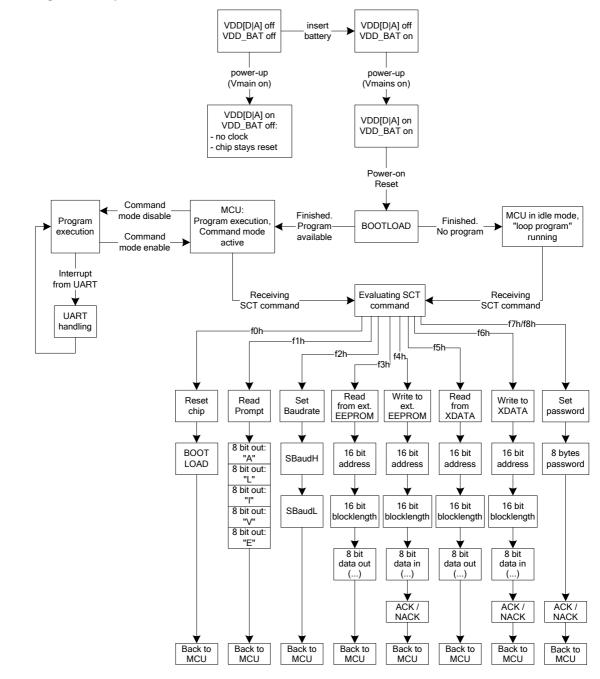

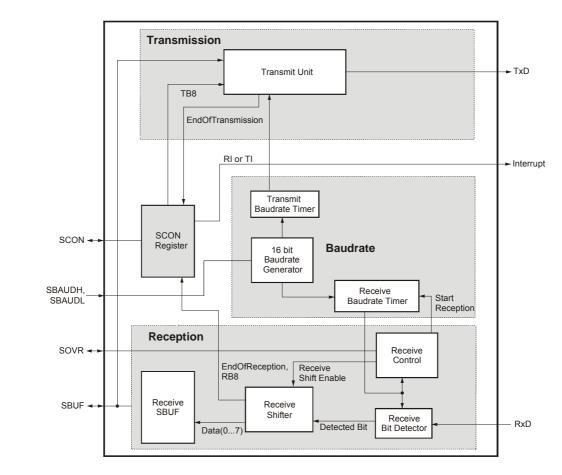

| np[31:24]       | 9305h   | 00h         |                                                                                                                                             |