# HT1380/HT1381 Serial Timekeeper Chip

### Features

- Operating voltage: 2.0V~5.5V

- Maximum input serial clock: 500kHz at  $V_{DD}$ =2V, 2MHz at  $V_{DD}$ =5V

- Operating current: less than 400nA at 2V, less than  $1.2\mu A$  at 5V

- TTL compatible

- $V_{IH}$ : 2.0V~ $V_{DD}$ +0.3V at  $V_{DD}$ =5V

- $V_{IL}$ : -0.3V~+0.8V at  $V_{DD}$ =5V

### Applications

• Microcomputer serial clock

# General Description

The HT1380/HT1381 is a serial timekeeper IC which provides seconds, minutes, hours, day, date, month and year information. The number of days in each month and leap years are automatically adjusted. The HT1380/HT1381 is designed for low power consumption and can operate in two modes: one is the 12-hour mode with an AM/PM indicator, the other is the 24-hour mode.

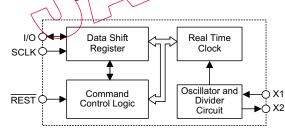

# **Block Diagram**

- Two data transmission modes: single-byte, or burst mode

- Serial I/O transmission

- All registers store BCD format

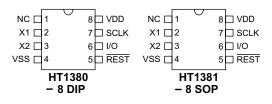

- HT1380: 8-pin DIP package HT1381: 8-pin SOP package

Clock and Calendar

The HT1380/HT1381 has several registers to store the corresponding information with 8-bit data format. A 32768Hz crystal is required to provide the correct timing. In order to minimize the pin number, the HT1380/HT1381 use a serial I/O transmission method to interface with a microprocessor. Only three wires are required: (1) REST, (2) SCLK and (3) I/O. Data can be delivered 1 byte at a time or in a burst of up to 8 bytes.

# **Pin Assignment**

October 2, 1999

1

| Pad Assignment                                                                                                                          |        | Pad Coord                          | linates           | Unit: µm    |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------------|-------------------|-------------|--|--|

| X1 1                                                                                                                                    |        | Pad No.                            | X                 | Y           |  |  |

| X2 2                                                                                                                                    | 7 VDD  | 1                                  | -851.40           | 775.00      |  |  |

|                                                                                                                                         | 6 SCL  | к 2                                | -851.40           | 494.60      |  |  |

| <b>↑</b>                                                                                                                                |        | 3                                  | -844.40           | -203.90     |  |  |

| (0,0)                                                                                                                                   | 5 I/O  | 4                                  | 845.90            | -618.30     |  |  |

| vss 3                                                                                                                                   |        | 5                                  | 848.40            | -4.30       |  |  |

|                                                                                                                                         |        | 6                                  | 845,90            | 332.60      |  |  |

|                                                                                                                                         | 4 RES  | T (7)                              | 844.40            | 572.60      |  |  |

| Chip size: 2010 × 1920 (µm) <sup>2</sup><br>* The IC substrate should be connected to VSS in the PCB layout artwork.<br>Pad Description |        |                                    |                   |             |  |  |

| Pad No. Pad Name I/O Internal<br>Connection                                                                                             |        |                                    | Description       |             |  |  |

| 1 X1 I CMOS                                                                                                                             | 32768  | 3Hz crystal inpu                   | ut pad            |             |  |  |

| 2 X2 O CMOS                                                                                                                             | Oscill | ator output pac                    | d                 |             |  |  |

| 3 VSS I CMOS                                                                                                                            | Grou   | Ground pin                         |                   |             |  |  |

| 4 REST I CMOS                                                                                                                           | Reset  | Reset pin with serial transmission |                   |             |  |  |

| 5 I/O VO CMOS                                                                                                                           | Data   | input/output pi                    | n with serial tr  | ransmission |  |  |

| 6 SCLK I CMOS                                                                                                                           | Seria  | l clock pulse pir                  | n with serial tra | ansmission  |  |  |

# **Absolute Maximum Ratings**

VDD

7

| Supply Voltage | 0.3V to 5.5V                     |

|----------------|----------------------------------|

| Input Voltage  | $V_{SS}$ –0.3V to $V_{DD}$ +0.3V |

Ι

CMOS

Storage Temperature......–50°C to  $125^\circ C$ Operating Temperature ......0°C to  $70^\circ C$

$\mathbf{2}$

Power supply pin

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

# **D.C. Characteristics**

| Ta=25°0 | 2 |

|---------|---|

|---------|---|

| G1               | Demonster         | Т                                   | Test Conditions       |        | <b>T</b>                                      | ЪЛ                 | <b>T T !</b> 4 |

|------------------|-------------------|-------------------------------------|-----------------------|--------|-----------------------------------------------|--------------------|----------------|

| Symbol           | Parameter         | $\mathbf{V}_{\mathbf{D}\mathbf{D}}$ | Conditions            | Min.   | Тур.                                          | Max.               | Unit           |

| V <sub>DD</sub>  | Operating Voltage |                                     |                       | 2      |                                               | 5.5                | V              |

| T                | Stor dhu Gumant   | 2V                                  |                       |        | _                                             | 100                | nA             |

| I <sub>STB</sub> | Standby Current   | 5V                                  |                       |        |                                               | 100                | nA             |

| T                | Otime C           | 2V                                  | N. I. J               | —      | 0.7                                           | 1.0                | μA             |

| I <sub>DD</sub>  | Operating Current | 5V                                  | No load               |        | 0.7                                           | 1.2                | μΑ             |

| т                | G G 4             | 2V                                  | V <sub>OH</sub> =1.8V | -0.2   | -0.4                                          |                    | mA             |

| I <sub>OH</sub>  | Source Current    | 5V                                  | V <sub>OH</sub> =4.5V | -0.5   | -1.0                                          |                    | mA             |

| т                |                   | 2V                                  | V <sub>OL</sub> =0.2V | 0.7    | 1.5                                           |                    | mA             |

| I <sub>OL</sub>  | Sink Current      | 5V                                  | V <sub>QL</sub> =0.5V | 2.0    | 4.0                                           | — /                | mA             |

| V <sub>IH</sub>  | "H" Input Voltage | 5V                                  |                       | 2      | — /                                           | $\sim$             | V              |

| V <sub>IL</sub>  | "L" Input Voltage | 5V                                  | _                     | —      | $\sim$                                        | 0.8                | V              |

| fosc             | System Frequency  | 5V                                  | 32768Hz X'TAL         | $\sim$ | 32768                                         | $\left( - \right)$ | Hz             |

|                  |                   | 2V                                  |                       | (-)    | $\left( \begin{array}{c} \end{array} \right)$ | 0.5                | MHz            |

| fSCLK            | Serial Clock      | 5V                                  |                       | FL     |                                               | 2                  | MHz            |

\* I<sub>STB</sub> is specified with SCLK, I/O, REST open. The clock halt bit must be set to logic 1 (oscillator disabled).

# A.C. Characteristics

### $Ta=25^{\circ}C$

| Gundhal          | A Baranta           | Tes             | t Conditions | Min  | Max. | Unit |  |

|------------------|---------------------|-----------------|--------------|------|------|------|--|

| Symbol           | Parameter           | V <sub>DD</sub> | Conditions   | Min. | max. | Unit |  |

| tab              | Data to Clock Setup | 2V              | —            | 200  |      | na   |  |

| t <sub>DC</sub>  | Data to Clock Setup | 5V              | —            | 50   |      | ns   |  |

| tana             | Clock to Data Hold  | 2V              | —            | 280  |      |      |  |

| t <sub>CDH</sub> | Clock to Data Hold  | 5V              | —            | 70   |      | ns   |  |

| t                | Clash to Data Dalam | 2V              | _            |      | 800  |      |  |

| t <sub>CDD</sub> | Clock to Data Delay | 5V              | _            |      | 200  | ns   |  |

| t                |                     | 2V              | _            | 1000 |      |      |  |

| t <sub>CL</sub>  | Clock Low Time      | 5V              |              | 250  |      | ns   |  |

| +                | Olash II'rk Miraa   | 2V              |              | 1000 |      |      |  |

| t <sub>CH</sub>  | Clock High Time     | 5V              |              | 250  |      | ns   |  |

| f                | Clash Engeneer      | 2V              |              |      | 0.5  | MIT- |  |

| f <sub>CLK</sub> | Clock Frequency     | 5V              |              | D.C. | 2.0  | MHz  |  |

3

| Symbol           | Parameter                       | Tes             | t Conditions                                             | Min.           | Max. | Unit |  |

|------------------|---------------------------------|-----------------|----------------------------------------------------------|----------------|------|------|--|

| Symbol           | Farameter                       | V <sub>DD</sub> | Conditions                                               | <b>IVIIII.</b> | max. | Unit |  |

| t <sub>r</sub>   | Clock Rise and Fall Time        | 2V              |                                                          | _              | 2000 | 20   |  |

| tf               | Clock Rise and Fall Time        | 5V              |                                                          | _              | 500  | ns   |  |

| taa              | Reset to Clock Setup            | 2V              |                                                          | 4              | —    |      |  |

| t <sub>CC</sub>  | Reset to Clock Setup            | 5V              |                                                          | 1              | —    | us   |  |

| taar             | Clock to Reset Hold             | 2V              |                                                          | 240            | _    |      |  |

| t <sub>CCH</sub> | Clock to Reset Hold             | 5V              |                                                          | 60             | _    | ns   |  |

| +                | Reset Inactive Time             | 2V              | - <                                                      | 4              | _    |      |  |

| t <sub>CWH</sub> | Reset mactive 11me              | 5V              |                                                          | × ×            | _    | us   |  |

| tana             | Denot to I/O II: ah Immedian an | 2V              |                                                          |                | 280  |      |  |

| t <sub>CDZ</sub> | Reset to I/O High Impedance     | 5V              | $\left( \begin{array}{c} \leftarrow \end{array} \right)$ |                | 70   | ns   |  |

# **Functional Description**

The HT1380/HT1381 mainly contains the following internal elements, a data shift register array to store the clock/calendar data, command control logic oscillator circuit and read timer clock. The clock is contained in eight read/write registers as shown below. Data contained in the clock register is in binary coded decimal format.

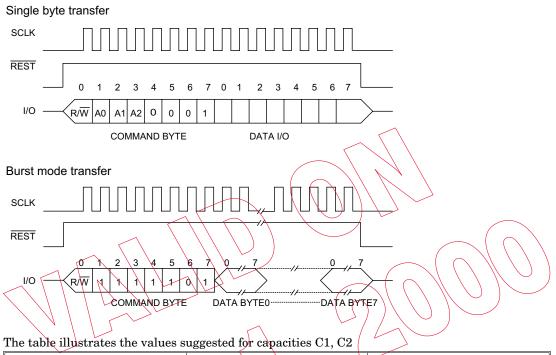

Two modes are available for transferring the data between the microprocessor and the HT1380/HT1381 One is in single-byte mode ad the other is in multiple-byte mode.

The HT1380/HT1881 also contains two additional bits, the clock halt bit (CH) and the write protect bit (WP). These bits control the operation of the oscillator and so data can be written to the register array. These two bits should first be specified in order to read from and write to the register array properly.

# Command byte

For each data transfer, a Command Byte is initiated to specify which register is accessed. This is to determine whether a read, write, or test cycle is operated and whether a single byte or burst mode transfer is to occur. Refer to the table shown below and follow the steps to write the data to the chip. First give a Command Byte of HT1380/HT1381, and then write a data in the register.

|                                     |           | Command Byte |    |    |    |    |    |     |

|-------------------------------------|-----------|--------------|----|----|----|----|----|-----|

| Function Description                | <b>C7</b> | <b>C6</b>    | C5 | C4 | C3 | C2 | C1 | C0  |

| Select Read or Write Cycle          |           |              |    |    |    |    |    | R/W |

| Specify the Register to be Accessed |           |              |    |    | A2 | A1 | A0 |     |

| Clock Halt Flag                     | С         |              |    |    |    |    |    |     |

| For IC Test Only                    | 1         | 0            | 0  | 1  | x  | x  | x  | 1   |

| Select Single Byte or Burst Mode    | 1         | 0            | 1  | 1  | 1  | 1  | 1  | x   |

4

| This table illustrates the correlation | between Command Byte and | their bits: |

|----------------------------------------|--------------------------|-------------|

|----------------------------------------|--------------------------|-------------|

Note: "x" stands for don't care

| Register         | Range          |            |               | Regi     | ster l    | Defin      | Definition |           |                 | Address | Bit    | Command                     |     |        |                             |

|------------------|----------------|------------|---------------|----------|-----------|------------|------------|-----------|-----------------|---------|--------|-----------------------------|-----|--------|-----------------------------|

| Name             | Data           | <b>D7</b>  | D6            | D5       | <b>D4</b> | <b>D</b> 3 | D2         | <b>D1</b> | <b>D0</b>       | A2~A0   | R/W    | Byte                        |     |        |                             |

| Seconds          | 00~59          | СН         | CH 10 SEC SEC |          | 0 SEC     |            | 10 SEC     |           | SEC             |         | SEC    |                             | 000 | W<br>R | $\frac{10000000}{10000001}$ |

| Minutes          | 00~59          | 0          | 1             | 0 MI     | N         |            | Μ          | IN        |                 | 001     | W<br>R | $\frac{10000010}{10000011}$ |     |        |                             |

| Hours            | 01~12<br>00~23 | $12 \\ 24$ | 0<br>0        | AP<br>10 | HR<br>HR  |            | НО         | UR        |                 | 010     | W<br>R | $\frac{10000100}{10000101}$ |     |        |                             |

| Date             | 01~31          | 0          | 0             | 10 D     | ATE       |            | DA         | TE        | $\langle $      | 01/1    | W<br>R | $\frac{10000110}{10000111}$ |     |        |                             |

| Month            | 01~12          | 0          | 0             | 0        | 10M       |            | моі        | NTH       | )               | 100     | W<br>R | $\frac{10001000}{10001001}$ |     |        |                             |

| Day              | 01~07          | -0         | 0             | 0        | Q         |            | D          | AY        |                 | 101     | W<br>R | 10001010<br>10001011        |     |        |                             |

| Year             | 00~99          |            | 10 Y          | EAR      | 1         |            | YE         | AR        |                 | 110     | W<br>R | 10001100<br>10001101        |     |        |                             |

| Write<br>Protect | 00~80          | WP         |               |          | ALW       | AYS Z      | ZERO       | 1         | $( \mathcal{S}$ | 111     | WR     | 10001110<br>10001111        |     |        |                             |

The following table shows the register address and its data format:

- CH: Clock Halt bit CH=0 oscillator enabled CH=1 oscillator disabled

- WP: Write protect bit WP=0 register data can be written in WP=1 register data can not be written in

Bit 7 of Reg2: 12/24 mode flag bit 7=1, 12-hour mode bit 7=0, 24-hour mode Bit 5 of Reg2: AM/PM mode defined AP=1 PM mode

# AP=0 AM mode

#### **R/W** signal

The LSB of the Command Byte determines whether the data in the register be read or be written to.

When it is set as "0" means that a write cycle is to take place otherwise this chip will be set into the read mode.

# A0~A2

A0 to A2 of the Command Byte is used to specify which registers are to be accessed. There are eight registers used to control the month data, etc., and each of these registers have to be set as a write cycle in the initial time.

#### Burst mode

When the Command Byte is 10111110 (or 10111111), the HT1380/HT1381 is configured in burst mode. In this mode the eight clock/calendar registers can be written (or read) in series, starting with bit 0 of register address 0 (see the timing on the next page).

#### Test mode

When the Command Byte is set as 1001xxx1, HT1380/HT1381 is configured in test mode. The test mode is used by Holtek only for testing purposes. If used generally, unpredictable conditions may occur.

#### $\mathbf{5}$

#### Write protect register

This register is used to prevent a write operation to any other register. Data can be written into the designated register only if the Write Protect signal (WP) is set to logic 0. The Write Protect Register should be set first before restarting the system or before writing the new data to the system, and it should set as logic 1 in the read cycle. The Write Protect bit cannot be written to in the burst mode.

#### **Clock Halt bit**

D7 of the Seconds Register is defined as the Clock Halt Flag (CH).

When this bit is set to logic 1, the clock oscillator is stopped and the chip goes into a low-power standby mode. When this bit is written to logic 0, the clock will start.

#### 12-hour/24-hour mode

The D7 of the hour register is defined as the 12-hour or 24-hour mode select bit.

When this bit is in high level, the 12-hour mode is selected otherwise it's the 24-hour mode.

#### AM-PM mode

These are two functions for the D5 of the hour register determined by the value D7 of the same register.

One is used in AMPM selection on the 12-hour mode. When D5 is logic P, it is PM, otherwise it's AM. The other is used to set the second 10-hour bit (20~23 hours) on the 24-hour mode.

#### **Reset and Serial Clock control**

The  $\overline{\text{REST}}$  pin is used to allow access data to the shift register like a toggle switch. When the  $\overline{\text{REST}}$  pin is taken high, the built-in control logic is turned on and the address/command sequence can access the corresponding shift register. The REST pin is also used to terminate either single-byte or burst mode data format.

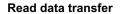

The input signal of SCLK is a sequence of a falling edge followed by a rising edge and it is used to synchronize the register data whether read or write. For data input, the data must be read after the rising edge of SCLK. The data on the I/O pin becomes output mode after the falling edge of the SCLK. All data transfer terminates if the REST pin is low and the I/O pin goes to a high impedance state. The data transfer is illustrated on the next page.

### Data in and Data out

In writing a data byte with HT1380/HT1381, the read/write should first set as R/W=0 in the Command Byte and follow with the corresponding data register on the rising edge of the next eight SCLK cycles. Additional SCLK cycles are ignored. Data inputs are entered starting with bit 0.

In reading a data on the register of HT1380/HT1381, RW=1 should first be entered as input. The data bit outputs on the falling edge of the next eight SCLK cycles. Note that the first data bit to be transmitted on the first falling edge after the last bit of the read command byte is written. Additional SCLK cycles re-transmits the data bytes as long as REST remains at high level. Data outputs are read starting with bit 0.

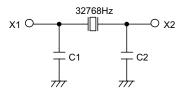

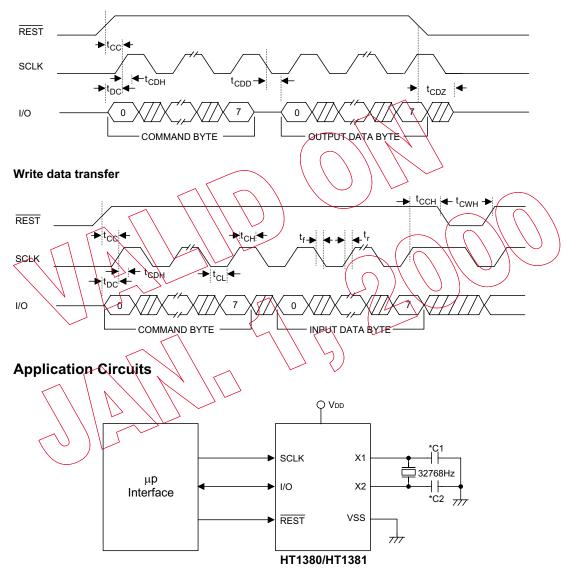

#### **Crystal selection**

6

A 32768Hz crystal can be directly connected to the HT1380/HT1381 via pin 2 and pin 3 (X1, X2). In order to obtain the correct frequency, two additional load capacities (C1, C2) are needed. The value of the capacity depends on how accurate the crystal is. We suggest that you can follow the table on the next page.

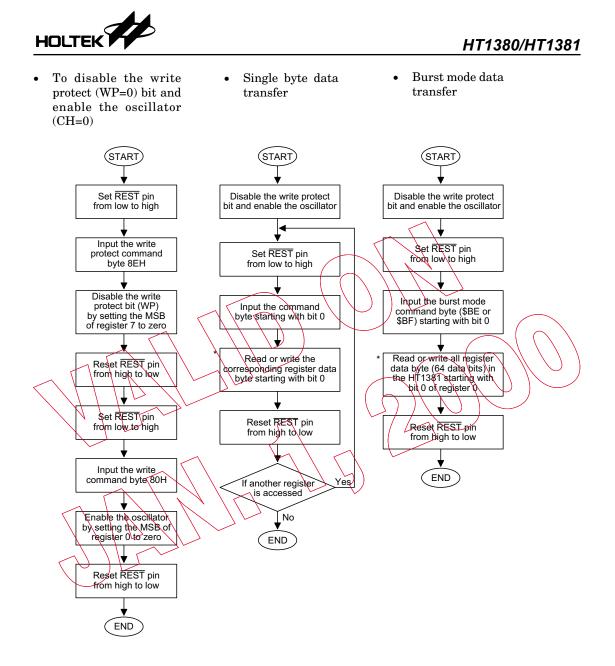

The following diagram shows the single and burst mode transfer:

| Part No.      | Crystal Error | Capacity Value  |

|---------------|---------------|-----------------|

| HT1380/HT1381 | ±10ppm        | $5 \mathrm{pF}$ |

| H11380/H11381 | 10~20ppm      | 8pF             |

#### **Operating flowchart**

To initiate any transfer of data, REST is taken high and an 8-bit command byte is first loaded into the control logic to provide the register address and command information. Following the command word, the clock/calendar data is serially transferred to or from the corresponding register. The REST pin must be taken low again after the transfer operation is completed. All data enter on the rising edge of SCLK and outputs on the falling edge of SCLK. In total, 16 clock pulses are needed for a single byte mode and 72 for burst mode. Both input and output data starts with bit 0.

In using the HT1380/HT1381, set first the WP and CH to 0 and wait for about 3 seconds, the oscillator will generate the clocks for internal use. Then, choose either single mode or burst mode to input the data. The read or write operating flowcharts are shown on the next page.

October 2, 1999

7

\* In reading data byte from HT1380/HT1381 register, the first data bit to be transmitted at the first falling edge after the last bit of the command byte is written.

October 2, 1999

8

HT1380/HT1381

# **Timing Diagrams**

9

\*Note: The value of the capacity depends on how accurate the crystal is. Refer to the suggestion table of page 7.

#### Holtek Semiconductor Inc. (Headquarters)

No.3 Creation Rd. II, Science-based Industrial Park, Hsinchu, Taiwan, R.O.C. Tel: 886-3-563-1999 Fax: 886-3-563-1189

#### Holtek Semiconductor Inc. (Taipei Office)

5F, No. 576, Sec. 7 Chung Hsiao E. Rd., Taipei, Taiwan, R.O.C. Tel: 886-2-2782-9635 Fax: 886-2-2782-9636 Fax: 886-2-2782-7128 (International sales hotline)

#### Holtek Semiconductor (Hong Kong) Ltd.

RM.711, Tower 2, Cheung Sha Wan Plaza, 833 Cheung Sha Wan Rd., Kowloon, Hong Kong Tel: 852-2-745-8288 Fax: 852-2-742-8657

Copyright @ 1999 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek assumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification, nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information, please visit our web site at http://www.holtek.com.tw.

10