# AS8202

# TTP/C-C2 Communication Controller

Preliminary Data Sheet Rev. 1.0, October 2000

# Key Features

- Dedicated controller supporting TTP/C (time triggered protocol class C)

- Suited for dependable distributed real-time systems with guaranteed response time

- Application fields: Automotive (by-wire braking, steering, vehicle dynamics control, drive train control), Aerospace (aircraft electronic systems), Industrial systems, Railway systems

- TTP/C asynchronous data rate up to 5 MBit/s @ clock 40 MHz, synchronous data rate 25 MBit/s @ clock 40 MHz

- Single power supply 3.3V

- 0.35µm CMOS process

- Temperature range: -40°C to 125° C

- 2k x 16 RAM message, status and control area (communication network interface)

- RAM for instruction code and configuration data

- 16 Bit non-multiplexed host CPU interface

- 16 Bit RISC architecture

- 16k x 16 internal FLASH memory for firmware and scheduling information

- software tools, design-in support, development boards available (http://www.tttech.com)

- 80 pin TQFP Package

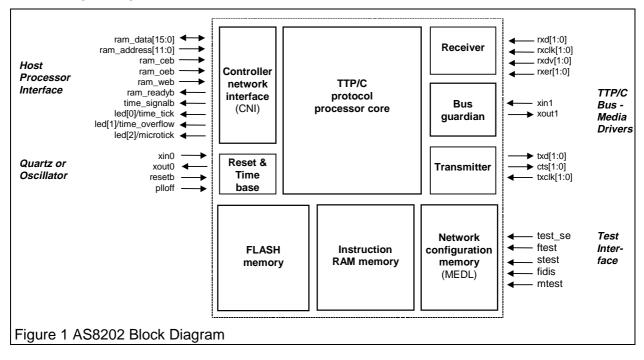

# **General Description**

The AS8202 communications controller is an integrated device supporting serial communication according to the TTP/C specification. It performs all communications tasks such as reception and transmission of messages in a TTP<sup>®</sup> cluster without interaction of the host CPU.

TTP<sup>®</sup> provides mechanisms that allow the deployment in high-dependability distributed realtime systems. It provides following services:

- predictable transmission of messages with minimal jitter

- fault-tolerant distributed clock synchronisation

- consistent membership service with small delay

- masking of single faults

The CNI (communication network interface) forms a temporal firewall. It decouples the controller network from the host subsystem by use of a dual ported RAM. This prevents the propagation of control errors. The interface to the host CPU is implemented as 16 bit wide non-multiplexed asynchronous bus interface.

TTP/C follows a conflict-free media access strategy called time-division-multiple access (TDMA). This means, TTP/C deploys a time slot technique based on a global time which is permanently synchronised. Each node is assigned a time slot in which it is allowed to perform transmit operation. The sequence of time slots is called TDMA round, a set of TDMA rounds forms a cluster cycle. After one cluster cycle the operation of the network repeats. The sequence of interactions forming the cluster cycle is defined in a static time schedule, called message-descriptor-list (MEDL). The definition of the MEDL in conjunction with the global time determines the response time for a service request.

The membership of all nodes in the network is evaluated by the communication controller. This information is presented in a consistent fashion to all correct cluster members. During operation, the status of every other node is propagated within one TDMA round. The MEDL is loaded into the configuration memory when the system starts up.

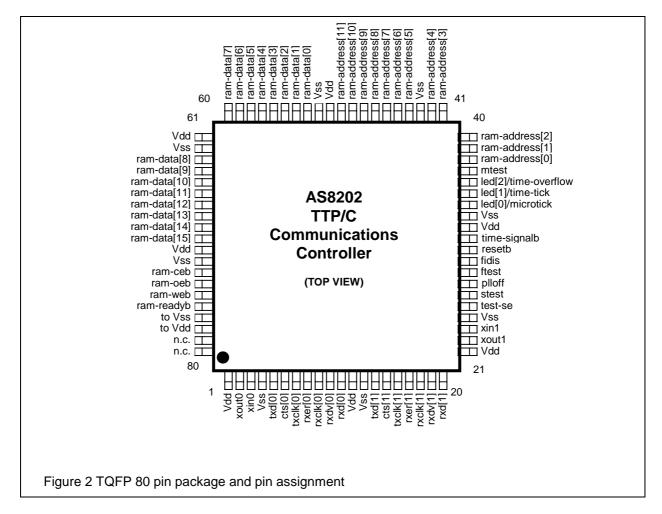

# Package and Pin Assignment

Type: TQFP 80, plastic package

# **Pin Description**

| Pin                    | Name                 | Dir                                | Description                                             |

|------------------------|----------------------|------------------------------------|---------------------------------------------------------|

| 1,12,21,32,51,61,71    | Vdd                  | Р                                  | positive power supply                                   |

| 4,13,24,33,43,52,62,72 | Vss                  | Р                                  | Negative power supply                                   |

| 2                      | xout0                | 0                                  | Main clock: analog pad from oscillator / leave open     |

|                        |                      |                                    | when providing external clock                           |

| 3                      | xin0                 | 1                                  | Main clock: analog pad from oscillator / use as input   |

|                        |                      |                                    | when providing external clock                           |

| 5                      | txd[0]               | O <sub>PU</sub>                    | Transmit data channel 0                                 |

| 6                      | cts[0]               | OPD                                | Transmit enable channel 0                               |

| 7                      | txclk[0]             | I <sub>PD</sub>                    | TTP/C synchronous: Transmit clock channel 0             |

| 8                      | rxer[0]              | I <sub>PU</sub>                    | TTP/C synchronous: Receive error channel 0              |

| 9                      | rxclk[0]             | I <sub>PD</sub>                    | TTP/C synchronous: Receive clock channel 0              |

| 10                     | rxdv[0]              | I <sub>PU</sub>                    | TTP/C synchronous: Receive data valid channel 0         |

| 11                     | rxd[0]               | I <sub>PU</sub>                    | Receive data channel 0                                  |

| 14                     | txd[1]               | O <sub>PU</sub>                    | Transmit data channel 1                                 |

| 15                     | cts[1]               | O <sub>PD</sub>                    | Transmit enable channel 1                               |

| 16                     | txclk[1]             | IPD                                | TTP/C synchronous: Transmit clock channel 1             |

| 17                     | rxer[1]              | I <sub>PU</sub>                    | TTP/C synchronous: Receive error channel 1              |

| 18                     | rxclk[1]             | I <sub>PD</sub>                    | TTP/C synchronous: Receive clock channel 1              |

| 19                     | rxdv[1]              | I <sub>PU</sub>                    | TTP/C synchronous: Receive data valid channel 1         |

| 20                     | rxd[1]               | I <sub>PU</sub>                    | Receive data channel 1                                  |

| 22                     | xout1                | 0                                  | Bus guardian clock: analog pad from oscillator / leave  |

|                        |                      |                                    | open when providing external clock                      |

| 23                     | xin1                 | I                                  | Bus guardian clock: analog pad from oscillator / use as |

|                        |                      |                                    | input when providing external clock                     |

| 25                     | toot oo              | 1                                  | Test input, connect to Vss                              |

| 25<br>26               | test_se              | I <sub>PD</sub>                    |                                                         |

| 20                     | stest                | IPD                                | Test input, connect to Vss                              |

| 28                     | plloff<br>ftest      | I <sub>PD</sub>                    | PLL disable pin<br>Test input, connect to Vss           |

| 29                     | fidis                | I <sub>PD</sub>                    | Test input, connect to Vss                              |

| 30                     | resetb               | I <sub>PD</sub>                    | main reset input signal, active low                     |

| 31                     | time_signalb         |                                    | CNI control signal, CNI time signal                     |

| 34                     | led[0]/microtick     | O <sub>PU</sub><br>O <sub>PD</sub> | Configurable: either generic output port (f.e. to drive |

| 54                     | led[0]/microtick     | OPD                                | LEDs) or timing signal TIME_TICK                        |

| 35                     | led[1]/time_tick     | O <sub>PD</sub>                    | Configurable: either generic output port (f.e. to drive |

| 55                     | led[])time_tex       | OPD                                | LEDs) or timing signal TIME_OVERFLOW                    |

| 36                     | led[2]/time_overflow | Opd                                | Configurable: either generic output port (f.e. to drive |

| 50                     | led[z]/time_overnow  | OPD                                | LEDs) or timing signal TIME_OVERFLOW                    |

| 37                     | mtest                | I <sub>PD</sub>                    | Test input, connect to Vss                              |

| 38-42,44-50            | ram_address[0:11]    |                                    | Host interface (CNI) address bus                        |

| 53-60,63-70            | ram_data[0:15]       | I/O                                | Host interface (CNI) data bus, tristate                 |

| 73                     | ram_ceb              | I, C                               | Host interface (CNI) chip enable, active low            |

| 74                     | ram_oeb              | I <sub>PU</sub>                    | Host interface (CNI) output enable, active low          |

| 75                     | ram_web              | I <sub>PU</sub>                    | Host interface (CNI) write enable, active low           |

| 76                     | ram_readyb           | OPU                                | Host interface (CNI) transfer finish signal, active low |

| 77                     | to Vss               | P                                  | Connect to Vss                                          |

| 78                     | to Vdd               | I <sub>PU</sub>                    | Connect to Vdd                                          |

| 79                     | high Z               | iFU                                | Do not connect                                          |

|                        | ·····                | 1                                  |                                                         |

#### I Input CMOS

l<sub>PU</sub> h pull down O

$I_{PD} \quad \mbox{Input CMOS with pull down} \\ O_{PD} \quad \mbox{Output with pull down when tristate}$

I/O Input/Output CMOS tristate

Input CMOS with pull up

O Output CMOS

$O_{PU}$  Output with pull up when tristate

P Power Pin

# **Electrical Specifications**

|                   |                          | •                  | •,                 |                             |

|-------------------|--------------------------|--------------------|--------------------|-----------------------------|

| SYMBOL            | PARAMETER                | MIN                | MAX                | NOTE                        |

| VDD               | DC Supply Voltage        | -0.3 V             | 5.0 V              |                             |

| V <sub>in</sub>   | Input Voltage on any Pin | - 0.3 V            | VDD + 0.3 V        |                             |

| l <sub>in</sub>   | Input Current on any Pin | -100 mA            | 100 mA             | 25°C                        |

| T <sub>strg</sub> | Storage Temperature      | -55 <sup>0</sup> C | 150 <sup>0</sup> C |                             |

| T <sub>sold</sub> | Soldering Temperature    |                    | 260 <sup>0</sup> C | 1)                          |

| t <sub>sold</sub> | Soldering Time           |                    | 10 sec             | Reflow and Wave             |

| Н                 | Humidity                 | 5 %                | 85 %               |                             |

| ESD               | Electrostatic Discharge  | 1000 V             |                    | HBM: R = 1.5 k□, C = 100 pF |

### Absolute Maximum Ratings (Non Operating)

1. 300 <sup>o</sup>C all ceramic packages and DIL plastic packages, 260 <sup>o</sup>C for surface mounting plastic packages **Note:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other

conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may effect device reliability (e.g. hot carrier degradation).

### **Recommended Operating Conditions**

| PARAMETER                    | SYMBOL | MIN    | ТҮР    | MAX                 | NOTE                          |

|------------------------------|--------|--------|--------|---------------------|-------------------------------|

| DC Supply Voltage            | VDD    | 3.0 V  | 3.3 V  | 3.6 V               | 1)                            |

| Circuit Ground               | VSS    | 0.0 V  | 0.0 V  | 0.0 V               |                               |

| Static Supply Current        | IDDS   |        | 700 µA | 800 µA              | 2)                            |

| Operating Supply Current     | IDD    |        | 45 mA  | 56 mA               | fCLK = 40  MHz,  VDD = 3.6  V |

| Main clock frequency         | CLK    | 5 MHz  |        | 20 MHz              | oscillator pins xin0, xout0   |

| Bus Guardian clock frequency | CLK2   | 4 MHz  |        | 16 MHz              | oscillatpr pins xin1, xout1   |

| Ambient Temperature          | Та     | -40 °C |        | +125 <sup>0</sup> C | 1)                            |

The input and output parameter values in this table are directly related to ambient temperature and DC supply voltage. A temperature range other Ta<sub>min</sub> to Ta<sub>max</sub> or a supply voltage range other than VDD<sub>min</sub> to VDD<sub>max</sub> will affect these values and must be evaluated extra.

2. Static supply current IDDS is exclusive of input/output drive requirements and is measured at maximum VDD with the clocks stopped and all inputs tied to VDD or VSS, configured to draw minimum current.

3. Operating current is exclusive of input/output drive requirements and is measured at maximum VDD and maximum clock frequency 40 MHz.

## DC Characteristics and Voltage Levels

CMOS I/O levels for specified voltage and temperature range unless otherwise noted.

#### Inputs Pins

| •                      |     |     |         |      | 1      |     | I              |

|------------------------|-----|-----|---------|------|--------|-----|----------------|

| Pin Name               | Vil | Vih | lil (1) |      | lih(2) |     | NOTE           |

|                        | max | min | min     | max  | min    | max |                |

| All inputs and IO pins | 30% | 70% | NA      | -1.0 | NA     | 1.0 | CMOS input (3) |

| without pull-up/down   | VDD | VDD |         | μA   |        | μA  | ,              |

| Inputs with pull-up    | 30% | 70% | -50     | -160 | NA     | NA  | CMOS with      |

|                        | VDD | VDD | μA      | μA   |        |     | pull up (3)    |

| Inputs with pull-down  | 30% | 70% | NA      | NA   | 30     | 160 | CMOS with      |

|                        | VDD | VDD |         |      | μA     | μA  | pull down (3)  |

1. Iil ist tested at VDDmax and Vin = 0

2. lih ist tested at VDDmax and Vin = VDDmax

3. CMOS input levels are in percentage of VDD, for pull-up/down refer to pin description above.

#### **Output Pins**

| Pin Name                   | Vol | Voh | lol (1) | loh(2) | loz(3) | NOTE                  |

|----------------------------|-----|-----|---------|--------|--------|-----------------------|

|                            | V   | V   | mA      | mA     | μΑ     |                       |

| txd[0,1],cts[0,1],led[0,2] | 0.4 | 2.4 | 4.0     | -4.0   | NA     | CMOS output           |

| All other output pins      | 0.4 | 2.4 | 2.0     | -2.0   | NA     | CMOS output           |

| (except xout0, xout1)      |     |     |         |        |        |                       |

| All I/O pins               | 0.4 | 2.4 | 2.0     | -2.0   | +/-10  | CMOS output, Tristate |

1. Vol, lol is tested at VDD = 3.3V

2. Voh, loh is tested at VDD = 3.3V

3. loz is tested at VDD = 3.6V

## AC Characteristics

| PARAMETER                                  | SYMBOL | PIN        | MIN   | MAX    | NOTE                              |

|--------------------------------------------|--------|------------|-------|--------|-----------------------------------|

| main clock external operating<br>frequency | clkext | xin0       | 0     | 40 MHz | pin plloff = high<br>PLL not used |

| main clock XTAL0 frequency                 | clkxt0 | xin0/xout0 | 1 MHz | 20 MHz | oscillator cell 1 1)              |

| main internal clock frequency              | clk0   |            |       | 40 MHz | pin plloff = low PLL              |

| XTAL1 operating frequency                  | clkxt1 | xin1/xout1 | 1 MHz | 20 MHz | oscillator cell 2 1)              |

1. XTAL frequency or external clock frequency for PLL input is fixed to 10 MHz, other frequencies applicable only without PLL function in use.

# **Application Information**

## Host CPU Interface

The host CPU interface also referred as CNI (communication network interface) connects the application circuitry to the TTP controller. All ram\_-lines provide asynchronous read/write access to a dual ported RAM. There are no setup/hold constraints referred to the microtick (main clock "clk0"). The signals have to be applied for certain duration to be synchronized to the main internal clock (microtick). The time\_-lines signal to host CPU the global synchronous time of the TTP network and determine when to deliver, resp. to fetch data from the host interface. One of the lines may be connected to an interrupt input of the host CPU. Note that the microtick, time\_overflow and the time\_tick pins can be configured as general purpose output LED pins (see the LED Interface section below).

| Host Interface Ports |             |       |                                               |

|----------------------|-------------|-------|-----------------------------------------------|

| Pin Name             | mode        | width | comment                                       |

| ram_address[0:11]    | in          | 12    | DPRAM address bus, 12 bit                     |

| ram_data[0:15]       | inout (tri) | 16    | DPRAM data bus, 16 bit                        |

| ram_ceb              | In          | 1     | DPRAM chip enable                             |

| ram_web              | In          | 1     | DPRAM write enable                            |

| ram_oeb              | In          | 1     | DPRAM output enable                           |

| ram_readyb           | out         | 1     | DPRAM ready                                   |

| time_overflow        | out         | 1     | Overflow of global time (global time is Zero) |

| microtick            | out         | 1     | Microtick (internal main clock)               |

| time_signal          | out         | 1     | CNI time signal                               |

| time_tick            | out         | 1     | Macrotick (global time is incremented)        |

Host Interface Ports

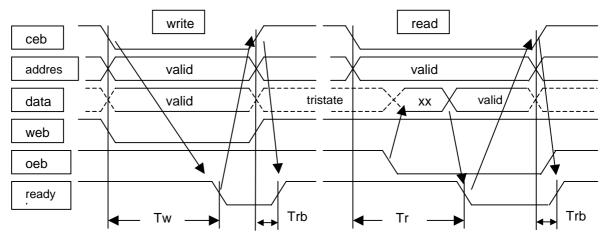

### Asynchronous DPRAM interface

Signals ram\_address[0:11] and ram\_web have to be stable before the falling edge of ram\_ceb For a write access the host sets ceb, web, address and data until the DPRAM has taken the data and set readyb active low. The next access may start with readyb inactive again. A read cycle starts with valid address and ceb, the data is valid with readyb active low. A low level on oeb and ceb switches the data bus from tristate to output. Access times depend on the controller clock rate and controller activity, typical values are:

| controller cycle time | Тс  | Min 25 ns (40 MHz) |

|-----------------------|-----|--------------------|

| write time            | Tw  | Min 4 Tc           |

| read time             | Tr  | Min 5 Tc           |

| readyb low time       | Trb | Min 1 Tc           |

## Reset and Oscillator

| Pin Name | mode | width | Comment                        |  |

|----------|------|-------|--------------------------------|--|

| xin0     | in   | 1     | main oscillator input          |  |

| xout0    | out  | 1     | main oscillator output         |  |

| xin1     | in   | 1     | bus guardian oscillator input  |  |

| xout1    | out  | 1     | bus guardian oscillator output |  |

| plloff   | in   | 1     | PLL disable                    |  |

| resetb   | in   | 1     | external reset                 |  |

Table 1: Reset and Oscillator Ports

#### **External Reset Signal**

To issue a reset of the chip the resetb port has to be driven low for at least  $\Box \Box \Box \mu s$ . After power-up the reset must overlap the build-up time of the oscillator circuit.

#### Integrated Power-On Reset

The Device has an internal Power-On Reset generator. When supply voltage ramps up, the internal reset signal is kept active (low) for about 33 µs typical.

| Parameter                                   | Symbol               | Min | Тур | Мах | Unit |

|---------------------------------------------|----------------------|-----|-----|-----|------|

| supply voltage slope                        | dV/dt                | 250 | -   | -   | kV/s |

| power on reset active time after VDD > 1,0V | t <sub>pon_res</sub> | 25  | 33  | 49  | us   |

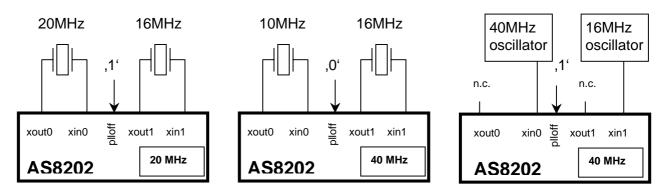

#### **Oscillator circuitry**

The internal oscillator cell requires an external quartz or an external oscillator respectively. The frequency applied on the main clock input (xin0, xout0) can be reduced by a factor of four by using the internal PLL. In order to generate an internal frequency of 40 MHz using the internal PLL, an external quartz or quartz oscillator with a frequency of 10 MHz is connected and the plloff input is tied low. The bus guardian clock has no internal PLL.

Figure 3: Quartz Circuit PLL off

Figure 4: Quartz Circuit PLL on

Figure 5: Oscillator Circuit

## TTP/C Asynchronous Bus Interface

The TTP/C asynchronous bus interface uses MFM patterns to transmit/receive signals at a maximum data rate of 5 MBit/s on a shared media (physical bus). The pins can either be connected to drivers using recessive/dominant states on the wire as well as drivers using active push/pull functionality.

| Pin Name | mode | comment                      |

|----------|------|------------------------------|

| txd[0]   | out  | Transmit data channel 0      |

| cts[0]   | out  | Transmit enable channel 0    |

| txclk[0] | in   | no function (do not connect) |

| rxer[0]  | in   | no function (do not connect) |

| rxclk[0] | in   | no function (do not connect) |

| rxdv[0]  | in   | no function (do not connect) |

| rxd[0]   | in   | Receive data channel 0       |

| txd[1]   | out  | Transmit data channel 1      |

| cts[1]   | out  | Transmit enable channel 1    |

| txclk[1] | in   | no function (do not connect) |

| rxer[1]  | in   | no function (do not connect) |

| rxclk[1] | in   | no function (do not connect) |

| rxdv[1]  | in   | no function (do not connect) |

| rxd[1]   | in   | Receive data channel 1       |

Table 2: TTP/C Asynchronous Bus Interface Pins

## TTP/C Synchronous Bus Interface

The TTP/C synchronous bus interface uses a synchronous transfer method to transfer data at a rate of 25 MBit/s. PHY drivers used in commercial 100 MBit Ethernet applications can be connected to this interface.

| Pin Name | mode | comment                      |

|----------|------|------------------------------|

| txd[0]   | out  | Transmit data channel 0      |

| cts[0]   | out  | Transmit enable channel 0    |

| txclk[0] | in   | Transmit clock channel 0     |

| rxer[0]  | in   | Receive error channel 0      |

| rxclk[0] | in   | Receive clock channel 0      |

| rxdv[0]  | in   | Receive data valid channel 0 |

| rxd[0]   | in   | Receive data channel 0       |

| txd[1]   | out  | Transmit data channel 1      |

| cts[1]   | out  | Transmit enable channel 1    |

| txclk[1] | in   | Transmit clock channel 1     |

| rxer[1]  | in   | Receive error channel 1      |

| rxclk[1] | in   | Receive clock channel 1      |

| rxdv[1]  | in   | Receive data valid channel 1 |

| rxd[1]   | in   | Receive data channel 1       |

Table 3: TTP/C Synchronous Bus Interface Pins

## Test Interface

The Test Interface supports the manufacturing test and characterisation of the chip. In the application environment test pins and special pins have to be connected as following:

test\_se, stest, ftest, fidis, mtest, Vpp : connect to Vss Tmr : connect to Vdd Tm0, Tm1 : do not connect

#### Warning:

Any other connection of this pins may cause permanent damage to the device.

## LED Signals

The LED signals can be used as a universal output port. The driver strength of the LED ports is 4mA. Note that the pins can be configured as special-function host interface pins (see the Host Interface section for more details).

# **Ordering Information**

Part Number: Part Name: Package: AS8202 TTP/C-C2 Communication Controller TQFP 80

# Support

Software tools, hardware development boards, evaluation systems and extensive support on TTP system integration as well as consulting is provided by:

TTTech Computertechnik AG Time-Triggered Technology and TTChip GmbH – a TTTech Company Schoenbrunnerstrasse 7 A1040 Vienna Austria Voice: +43 1 5853434 - 0 Fax: +43 1 5853434 - 90 email: office@tttech.com web: http://www.tttech.com

Note: TTP<sup>®</sup> is a registered trademark of FTS Computertechnik GmbH. All other trademarks are the property of their respective holders.

Copyright © 2000 TTTech Computertechnik AG

Copyright © 2000, Austria Mikro Systeme International AG, Schloß Premstätten, 8141 Unterpremstätten, Austria.

Telefon +43-(0)3136-500-0, Telefax +43-(0)3136-52501, E-Mail info@amsint.com

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, without the prior permission in writing by the copyright holder. To the best of its knowledge, Austria Mikro Systeme International asserts that the information contained in this publication is accurate and correct.