#### rev 0.3

# ASM2P2310A

# 2.5-V TO 3.3-V High-Performance Clock Buffer

#### Features

- High-Performance 1:10 Clock Driver for General Purpose applications. Operates up to 200 MHz at 3.3V Supply Voltage

- Pin-to-Pin Skew < 100 pS at 3.3V Supply Voltage

- Supply Range : 2.3V to 3.6V

- Operating Temperature Range : -40°C to 85°C

- Output Enable Glitch Suppression

- Distributes One Clock Input to Two Banks of Five Outputs

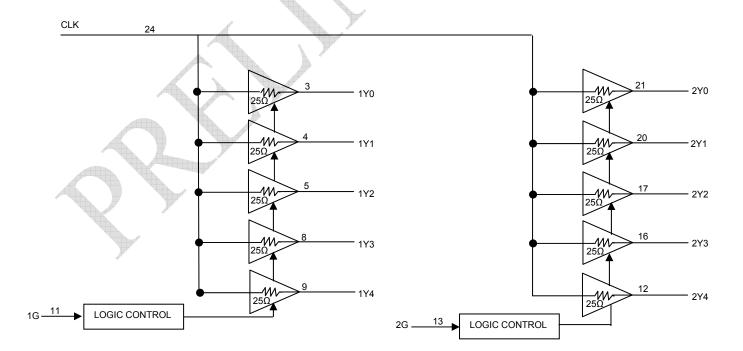

- 25Ω On Chip Series Damping Resistors

- Packaged in 24 Pin TSSOP Package

#### **Product Description**

The ASM2P2310A is a high-performance, low-skew clock buffer that operates up to 200MHz. Two banks of five outputs each provide low-skew copies of CLK. After power up, the default state of the outputs is low regardless of the state of the control pins. For normal operation, the outputs of bank 1Y[0:4] or 2Y[0:4] can be placed in a low state when the control pins (1G or 2G, respectively) are held low and a negative clock edge is detected on the CLK input. The outputs of bank 1Y[0:4] or 2Y[0:4] can be switched into the buffer mode when the control pins (1G and 2G) are held high and a negative clock edge is detected on the CLK input. The device operates in a 2.5V and 3.3V environment. The built-in output enable glitch suppression ensures a synchronized output enable sequence to distribute full period clock signals.

The ASM2P2310A is characterized for operation from -40°C to 85°C.

PulseCore Semiconductor Corporation 1715 S. Bascom Ave Suite 200, Campbell, CA 95008 • Tel: 408-879-9077 • Fax: 408-879-9018 www.pulsecoresemi.com

#### **Block Diagram**

Notice: The information in this document is subject to change without notice.

# ASM2P2310A

# November 2006

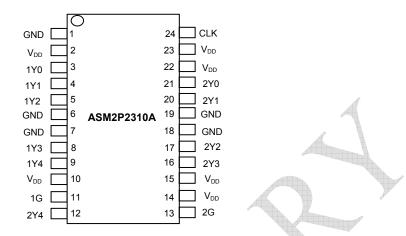

# rev 0.3 Pin Configuration

#### **Pin Description**

| Pin # | Pin Name        | Туре | Description                                                                                                                                                             |

|-------|-----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | GND             | Р    | Ground Pin                                                                                                                                                              |

| 2     | V <sub>DD</sub> | Р    | DC Power supply, 2.3 V – 3.6V                                                                                                                                           |

| 3     | 1Y0             | 0    | Buffered Output Clock                                                                                                                                                   |

| 4     | 1Y1             | 0    | Buffered Output Clock                                                                                                                                                   |

| 5     | 1Y2             | 0    | Buffered Output Clock                                                                                                                                                   |

| 6     | GND             | Р    | Ground Pin                                                                                                                                                              |

| 7     | GND             | Р    | Ground Pin                                                                                                                                                              |

| 8     | 1Y3             | 0    | Buffered Output Clock                                                                                                                                                   |

| 9     | 1Y4             | 0    | Buffered Output Clock                                                                                                                                                   |

| 10    | V <sub>DD</sub> | Р    | DC power supply, 2.3V – 3.6V                                                                                                                                            |

| 11    | 1G              |      | Output enable control for 1Y[0:4] outputs. This output enable is active-high, meaning the 1Y[0:4] clock outputs follow the input clock (CLK) if this pin is logic high. |

| 12    | 2Y4             | 0    | Buffered Output Clock                                                                                                                                                   |

| 13    | 2G              |      | Output enable control for 2Y[0:4] outputs. This output enable is active-high, meaning the 2Y[0:4] clock outputs follow the input clock (CLK) if this pin is logic high. |

| 14    | V <sub>DD</sub> | Р    | DC power supply, 2.3V – 3.6V                                                                                                                                            |

| 15    | VDD             | P    | DC power supply, 2.3V – 3.6V                                                                                                                                            |

| 16    | 2Y3             | 0    | Buffered Output Clock                                                                                                                                                   |

| 17    | 2Y2             | 0    | Buffered Output Clock                                                                                                                                                   |

| 18    | GND             | Р    | Ground Pin                                                                                                                                                              |

| 19    | GND             | Р    | Ground Pin                                                                                                                                                              |

| 20    | 2Y1             | 0    | Buffered Output Clock                                                                                                                                                   |

| 21    | 2Y0             | 0    | Buffered Output Clock                                                                                                                                                   |

| 22    | V <sub>DD</sub> | Р    | DC power supply, 2.3V – 3.6V                                                                                                                                            |

| 23    | V <sub>DD</sub> | Р    | DC power supply, 2.3V – 3.6V                                                                                                                                            |

| 24    | CLK             | Ι    | Input reference frequency                                                                                                                                               |

#### rev 0.3

#### **Function Table**

| Input                   |                                                                                                                               |              | Output           |                  |  |  |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------|------------------|------------------|--|--|--|

| 1G                      | 2G                                                                                                                            | CLK          | 1Y[0:4]          | 2Y[0:4]          |  |  |  |

| L                       | L                                                                                                                             | $\downarrow$ | L                | L                |  |  |  |

| Н                       | L                                                                                                                             | $\downarrow$ | CLK <sup>1</sup> | A                |  |  |  |

| L                       | Н                                                                                                                             | $\downarrow$ | L                | CLK <sup>1</sup> |  |  |  |

| Н                       | Н                                                                                                                             | $\downarrow$ | CLK <sup>1</sup> | CLK <sup>1</sup> |  |  |  |

| Note: 1 After detecting | Note: 1 After detecting one negative edge on the CLK input, the output follows the input CLK if the control pin is held high. |              |                  |                  |  |  |  |

#### **Detailed Description**

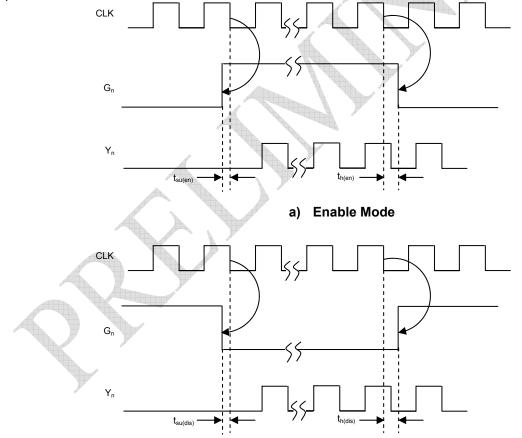

#### **Output Enable Glitch Suppression Circuit**

The purpose of the glitch suppression circuitry is to ensure the output enable sequence is synchronized with the clock input such that the output buffer is enabled or disabled on the next full period of the input clock (negative edge triggered by the input clock) (see Figure 1).

The G input must fulfill the timing requirements ( $t_{su}$ ,  $t_h$ ) according to the Switching Characteristics table for predictable operation.

b) Disable Mode Figure 1. Enable and Disable Mode Relative to CLK  $\downarrow$

#### rev 0.3

#### **Absolute Maximum Ratings**

| Parameter                                                                                                            | Rating                                                   |

|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Supply Voltage range, V <sub>DD</sub>                                                                                | -0.5V to 4.6V                                            |

| Input Voltage range, VI <sup>1,2</sup>                                                                               | -0.5 V to V <sub>DD</sub> + 0.5 V                        |

| Output Voltage range, V <sub>0</sub> <sup>1,2</sup>                                                                  | -0.5 V to V <sub>DD</sub> + 0.5 V                        |

| Continuous total output current, $I_0$ (V <sub>o</sub> = 0 to V <sub>DD</sub> )                                      | ±50 mA                                                   |

| Package thermal impedance, $\theta_{JA}^{3}$ : PW package                                                            | 120°C/W                                                  |

| Storage temperature range T <sub>stg</sub>                                                                           | -65°C to 150°C                                           |

| Static Discharge Voltage , t <sub>DV</sub> (As per JEDEC STD22- A114-B)                                              | 2KV                                                      |

| Note: These are stress ratings only and are not implied for functional use. Exposure to absolute device reliability. | maximum ratings for prolonged periods of time may affect |

Notes :

1 The input and output negative voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

2 This value is limited to 4.6 V maximum.

3 The package thermal impedance is calculated in accordance with JESD 51.

# **Recommended Operating Conditions<sup>1</sup>**

|                                            | Parameter                               | Min | Тур | Max             | Unit |  |

|--------------------------------------------|-----------------------------------------|-----|-----|-----------------|------|--|

| Supply voltage, V <sub>DD</sub>            |                                         | 2.3 | 2.5 |                 | V    |  |

|                                            |                                         |     | 3.3 | 3.6             | v    |  |

| Low-level input voltage, V <sub>IL</sub>   | V <sub>DD</sub> = 3V to 3.6V            |     |     | 0.8             | v    |  |

| Low-level input voltage, vi                | V <sub>DD</sub> = 2.3V to 2.7V          |     |     | 0.7             | v    |  |

| High-level input voltage, V <sub>IH</sub>  | V <sub>DD</sub> = 3V to 3.6V            | 2   |     |                 | v    |  |

|                                            | V <sub>DD</sub> = 2.3V to 2.7V          | 1.7 |     |                 | v    |  |

| Input voltage, V <sub>I</sub>              |                                         | 0   |     | $V_{\text{DD}}$ | V    |  |

| High-level output current, I <sub>OH</sub> | V <sub>DD</sub> = 3V to 3.6V            |     |     | 12              | mA   |  |

|                                            | V <sub>DD</sub> = 2.3 V to 2.7V         |     |     | 6               |      |  |

| Low-level output current, Io               | $V_{DD} = 3V$ to 3.6V                   |     |     | 12              | mA   |  |

|                                            | V <sub>DD</sub> = 2.3V to 2.7V          |     |     | 6               |      |  |

| Operating free-air temperature             | , T <sub>A</sub>                        | -40 |     | 85              | °C   |  |

| Note:1 Unused inputs must be held hig      | h or low to prevent them from floating. |     |     |                 |      |  |

# ASM2P2310A

#### rev 0.3

#### **Electrical Characteristics**

Over recommended operating free-air temperature range (unless otherwise noted)

| Symbol                                                                                                                        | Parameter             | Test C                          | onditions                       | Min | Typ <sup>1</sup> | Max  | Unit |  |

|-------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------------|---------------------------------|-----|------------------|------|------|--|

| VIK                                                                                                                           | Input voltage         | $V_{DD} = 3V,$                  | l <sub>l</sub> = -18 mA         |     |                  | -1.2 | V    |  |

| I <sub>I</sub>                                                                                                                | Input current         | $V_{I} = 0V \text{ or } V_{DD}$ |                                 |     |                  | ±5   | μA   |  |

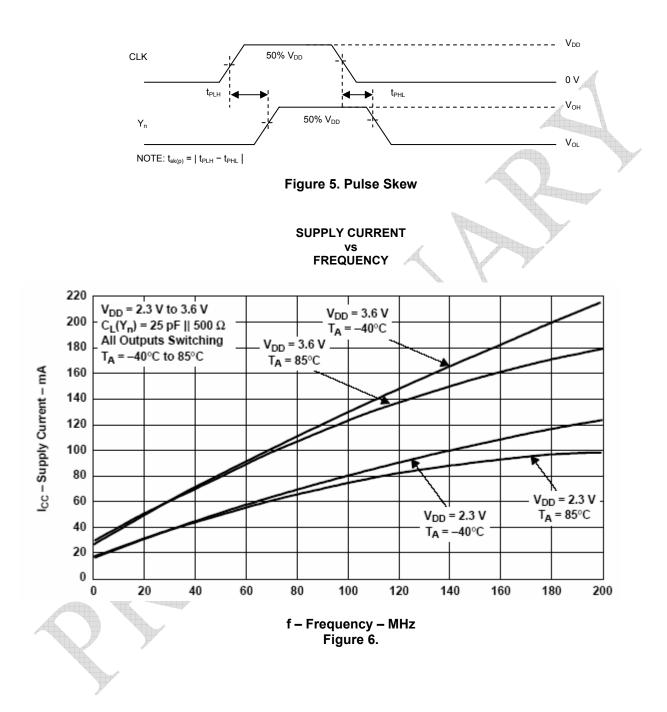

| $I_{DD}^2$                                                                                                                    | Static device current | $CLK = 0V \text{ or } V_{DD},$  | I <sub>0</sub> = 0 mA           |     |                  | 80   | μA   |  |

| CI                                                                                                                            | Input capacitance     | V <sub>DD</sub> = 2.3V to 3.6V, | $V_{I} = 0V \text{ or } V_{DD}$ |     | 2.5              |      | pF   |  |

| Co                                                                                                                            | Output capacitance    | V <sub>DD</sub> = 2.3V to 3.6V, | $V_I = 0V \text{ or } V_{DD}$   |     | 2.8              |      | pF   |  |

| Note: 1 All typical values are at respective nominal V <sub>DD</sub> .<br>2 For I <sub>CC</sub> over frequency, see Figure 6. |                       |                                 |                                 |     |                  |      |      |  |

## $V_{DD}$ = 3.3 V ±0.3 V

| Symbol          | Parameter                 | Test C                      | onditions                     | Min                   | Typ <sup>1</sup> | Max  | Unit |

|-----------------|---------------------------|-----------------------------|-------------------------------|-----------------------|------------------|------|------|

|                 |                           | V <sub>DD</sub> = Min to Ma | ix, I <sub>OH</sub> = -100 μA | V <sub>DD</sub> - 0.2 |                  |      |      |

| V <sub>OH</sub> | High-level output voltage | V <sub>DD</sub> = 3 V       | I <sub>OH</sub> = -12 mA      | 2.1                   |                  |      | V    |

|                 |                           | VDD - 3 V                   | I <sub>ОН</sub> = -6 mA       | 2.4                   |                  |      |      |

|                 |                           | V <sub>DD</sub> = Min to Ma | ux, I <sub>OL</sub> = -100 μA |                       |                  | 0.2  |      |

| V <sub>OL</sub> | Low-level output voltage  |                             | I <sub>OL</sub> = 12mA        |                       |                  | 0.8  | V    |

|                 |                           | V <sub>DD</sub> = 3V        | I <sub>OL</sub> = 6 mA        |                       |                  | 0.55 |      |

|                 |                           | $V_{DD} = 3V,$              | V <sub>0</sub> = 1V           | -28                   |                  |      |      |

| I <sub>OH</sub> | High-level output current | $V_{DD} = 3.3V,$            | V <sub>0</sub> = 1.65V        |                       | -36              |      | mA   |

|                 |                           | $V_{DD} = 3.6V,$            | V <sub>0</sub> = 3.135V       |                       |                  | -14  |      |

|                 |                           | $V_{DD} = 3V,$              | V <sub>o</sub> = 1.95V        | 28                    |                  |      |      |

| I <sub>OL</sub> | Low-level output current  | $V_{DD} = 3.3V,$            | V <sub>O</sub> = 1.65V        |                       | 36               |      | mA   |

|                 |                           | $V_{DD} = 3.6V,$            | V <sub>O</sub> = 0.4V         |                       |                  | 14   |      |

# V<sub>DD</sub> = 2.5 V ±0.2 V

| Symbol          | Parameter                                                              | Test Cor                      | ditions                   | Min                   | Typ <sup>1</sup> | Max  | Unit |  |

|-----------------|------------------------------------------------------------------------|-------------------------------|---------------------------|-----------------------|------------------|------|------|--|

| V <sub>он</sub> | High-level output voltage                                              | V <sub>DD</sub> = Min to Max, | I <sub>OH</sub> = -100 μA | V <sub>DD</sub> - 0.2 |                  |      | v    |  |

| VOH             | Tigh-level output voltage                                              | V <sub>DD</sub> = 2.3V        | I <sub>он</sub> = -6 mA   | 1.8                   |                  |      | v    |  |

| VOL             | Low-level output voltage                                               | V <sub>DD</sub> = Min to Max, | I <sub>OL</sub> = 100 μA  |                       |                  | 0.2  | v    |  |

| VOL             | Low-level output voltage                                               | V <sub>DD</sub> = 2.3V        | I <sub>OL</sub> = 6 mA    |                       |                  | 0.55 | v    |  |

| Ť               |                                                                        | V <sub>DD</sub> = 2.3V,       | $V_0 = 1V$                | -17                   |                  |      |      |  |

| I <sub>ОН</sub> | High-level output current                                              | V <sub>DD</sub> = 2.5V,       | V <sub>0</sub> = 1.25V    |                       | -25              |      | mA   |  |

|                 | <i>¥</i>                                                               | V <sub>DD</sub> = 2.7V,       | V <sub>O</sub> = 2.375V   |                       |                  | -10  |      |  |

|                 |                                                                        | V <sub>DD</sub> = 2.3V,       | V <sub>0</sub> = 1.2V     | 17                    |                  |      |      |  |

| I <sub>OL</sub> | Low-level output current                                               | V <sub>DD</sub> = 2.5V,       | V <sub>O</sub> = 1.25V    |                       | 25               |      | mA   |  |

|                 |                                                                        | V <sub>DD</sub> = 2.7V,       | V <sub>O</sub> = 0.3V     |                       |                  | 10   |      |  |

| Note: 1 All typ | Note: 1 All typical values are at respective nominal V <sub>DD</sub> . |                               |                           |                       |                  |      |      |  |

$\overbrace{}$

### rev 0.3

Timing Requirements Over recommended ranges of supply voltage and operating free-air temperature

| Symbol | Parameter       | Test Conditions                  | Min | Тур | Max | Unit |

|--------|-----------------|----------------------------------|-----|-----|-----|------|

| f      | Clock froguenov | $V_{DD} = 3 V \text{ to } 3.6 V$ | 0   |     | 200 | MHz  |

| Tclk   | Clock frequency | V <sub>DD</sub> = 2.3 V to 2.7V  | 0   |     | 170 |      |

#### **Switching Characteristics**

Over recommended operating free-air temperature range (unless otherwise noted)

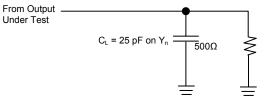

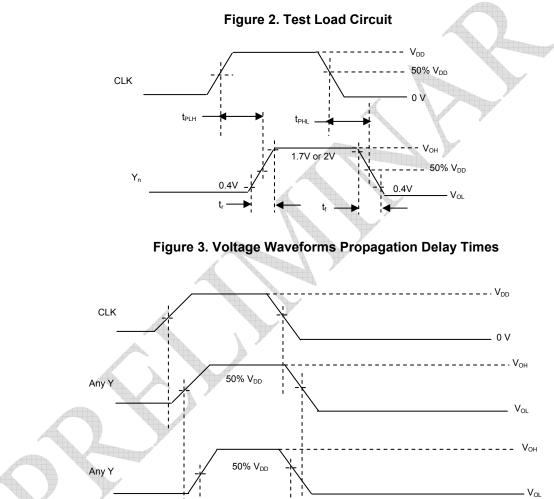

#### V<sub>DD</sub> = 3.3 V ±0.3 V (See Figure 2)

| Symbol                        | Parameter                                                                                   | Test Conditions                           | Min | Тур | Max | Unit |  |  |

|-------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------|-----|-----|-----|------|--|--|

| t <sub>PLH</sub>              | CLK to Yn                                                                                   | f = 0 MHz to 200 MHz<br>For circuit load, | 1.3 |     | 2.8 | nS   |  |  |

| t <sub>PHL</sub>              |                                                                                             | see Figure 2.                             |     |     |     |      |  |  |

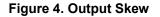

| tsk(o)                        | Output skew (Ym to Yn) <sup>1</sup> (see Figure 4)                                          |                                           |     |     | 100 | pS   |  |  |

| <b>t</b> sk(p)                | Pulse skew (see Figure 5)                                                                   |                                           |     |     | 250 | pS   |  |  |

| tsk(pp)                       | Part-to-part skew                                                                           |                                           |     |     | 500 | pS   |  |  |

| tr                            | Rise time (see Figure 3)                                                                    | $V_0 = 0.4V$ to 2V                        | 0.7 |     | 2   | V/nS |  |  |

| t <sub>f</sub>                | Fall time (see Figure 3)                                                                    | $V_0 = 2 V \text{ to } 0.4 V$             | 0.7 |     | 2   | V/nS |  |  |

| <b>t</b> su(en)               | Enable setup time,G_high before CLK $\downarrow$                                            |                                           | 0.1 |     |     | nS   |  |  |

| tsu(dis)                      | Disable setup time, G_low before $CLK\downarrow$                                            |                                           | 0.1 |     |     | nS   |  |  |

| <b>t</b> h(en)                | Enable hold time, G_high after CLK ↓                                                        |                                           | 0.4 |     |     | nS   |  |  |

| th(dis)                       | Disable hold time, G_low after CLK $\downarrow$                                             |                                           | 0.4 |     |     | nS   |  |  |

| Note: 1 The t <sub>sk(c</sub> | Note: 1 The t <sub>sk(o)</sub> specification is only valid for equal loading of all outputs |                                           |     |     |     |      |  |  |

#### V<sub>DD</sub> = 2.5 V ±0.2 V (See Figure 2)

| Symbol                        | Parameter                                                        | Test Conditions                         | Min | Тур | Max | Unit                                                                                        |  |  |  |  |  |  |  |  |

|-------------------------------|------------------------------------------------------------------|-----------------------------------------|-----|-----|-----|---------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| t <sub>PLH</sub>              | CLK to Yn                                                        | f = 0MHz to 170MHz<br>For circuit load, | 1.5 |     | 3.5 | nS                                                                                          |  |  |  |  |  |  |  |  |

| t <sub>PHL</sub>              |                                                                  | see Figure 2.                           |     |     |     |                                                                                             |  |  |  |  |  |  |  |  |

| tsk(o)                        | Output skew (Ym to Yn) <sup>1</sup> (see Figure 4)               |                                         |     |     | 170 | pS                                                                                          |  |  |  |  |  |  |  |  |

| tsk(p)                        | Pulse skew (see Figure 5)                                        |                                         |     |     | 400 | pS                                                                                          |  |  |  |  |  |  |  |  |

| tsk(pp)                       | Part-to-part skew                                                |                                         |     |     | 600 | pS                                                                                          |  |  |  |  |  |  |  |  |

| tr                            | Rise time (see Figure 3)                                         | $V_0 = 0.4V$ to 1.7V                    | 0.5 |     | 1.4 | V/nS                                                                                        |  |  |  |  |  |  |  |  |

| t <sub>f</sub>                | Fall time (see Figure 3)                                         | V <sub>O</sub> = 1.7V to 0.4V           | 0.5 |     | 1.4 | V/nS                                                                                        |  |  |  |  |  |  |  |  |

| tsu(en                        | Enable setup time,G_high before CLK↓                             |                                         | 0.1 |     |     | nS                                                                                          |  |  |  |  |  |  |  |  |

| tsu(dis)                      | Disable setup time, G_low before CLK↓                            |                                         | 0.1 |     |     | nS                                                                                          |  |  |  |  |  |  |  |  |

| th(en)                        | Enable hold time, G_high after CLK ↓                             |                                         | 0.4 |     |     | nS                                                                                          |  |  |  |  |  |  |  |  |

| th(dis)                       | Disable hold time, G_low after CLK $\downarrow$                  |                                         | 0.4 |     |     | nS                                                                                          |  |  |  |  |  |  |  |  |

| Note: 1 The t <sub>sk(c</sub> | ,<br>specification is only valid for equal loading of all output | ts.                                     | -1  |     | •   | ote: 1 The t <sub>sk(0)</sub> specification is only valid for equal loading of all outputs. |  |  |  |  |  |  |  |  |

# ASM2P2310A

#### rev 0.3

#### **Parameter Measurement Information**

t<sub>SK(O)</sub>

A. C<sub>L</sub> includes probe and jig capacitance.

B. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  200 MHz, Z<sub>0</sub> = 50 $\Omega$ , t<sub>r</sub> < 1.2 ns, t<sub>r</sub> < 1.2 ns,

t<sub>SK(O)</sub>

# 2.5-V TO 3.3-V High-Performance Clock Buffer

7 of 11

# **ASM2P2310A**

## rev 0.3

ASM2P2310A

rev 0.3

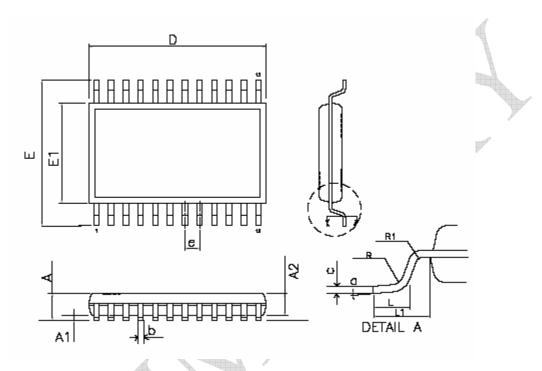

# Package Information

24L TSSOP (173 mil)

|        |        | Dimen  | sions    |       |  |

|--------|--------|--------|----------|-------|--|

| Symbol | Inch   | ies    | Millim   | eters |  |

|        | Min    | Max    | Min      | Max   |  |

| A      |        | 0.043  |          | 1.2   |  |

| A1     | 0.0020 | 0.0059 | 0.05     | 0.15  |  |

| A2     | 0.031  | 0.041  | 0.80     | 1.05  |  |

| D      | 0.3031 | 0.311  | 7.70     | 7.90  |  |

| L L    | 0.020  | 0.030  | 0.50     | 0.75  |  |

| E      | 0.252  | BSC    | 6.40     | BSC   |  |

| E1     | 0.169  | 0.177  | 4.30     | 4.50  |  |

| R      | 0.004  |        | 0.09     |       |  |

| R1     | 0.004  |        | 0.09     |       |  |

| b      | 0.007  | 0.012  | 0.19     | 0.30  |  |

| С      | 0.004  | 0.008  | 0.09     | 0.20  |  |

| L1     | 0.039  | REF    | 1.0 REF  |       |  |

| е      | 0.026  | BSC    | 0.65 BSC |       |  |

| а      | 0°     | 8°     | 0°       | 8°    |  |

rev 0.3

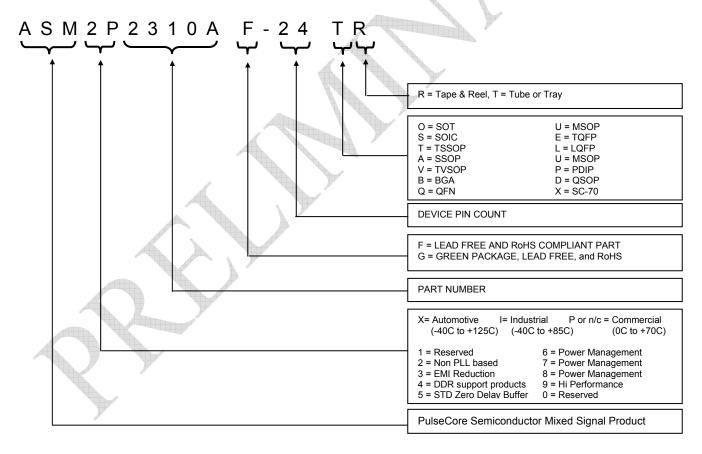

#### **Ordering Information**

| Part Number      | Marking  | Package Type                       | Temperature |

|------------------|----------|------------------------------------|-------------|

| ASM2P2310AF-24TR | 2P2310AF | 24-Pin TSSOP, TAPE & REEL, Pb Free | Commercial  |

| ASM2P2310AF-24TT | 2P2310AF | 24-Pin TSSOP, TUBE, Pb Free        | Commercial  |

| ASM2P2310AG-24TR | 2P2310AG | 24-Pin TSSOP, TAPE & REEL, Green   | Commercial  |

| ASM2P2310AG-24TT | 2P2310AG | 24-Pin TSSOP, TUBE, Green          | Commercial  |

| ASM2I2310AF-24TR | 2I2310AF | 24-Pin TSSOP, TAPE & REEL, Pb Free | Industrial  |

| ASM2I2310AF-24TT | 2I2310AF | 24-Pin TSSOP, TUBE, Pb Free        | Industrial  |

| ASM2I2310AG-24TR | 2I2310AG | 24-Pin TSSOP, TAPE & REEL, Green   | Industrial  |

| ASM2I2310AG-24TT | 2I2310AG | 24-Pin TSSOP, TUBE, Green          | Industrial  |

#### **Device Ordering Information**

Licensed under US patent Nos 5,488,627 and 5,631,920.

PulseCore

rev 0.3

PulseCore Semiconductor Corporation 1715 S. Bascom Ave Suite 200 Campbell, CA 95008 Tel: 408-879-9077 Fax: 408-879-9018 www.pulsecoresemi.com Copyright © PulseCore Semiconductor All Rights Reserved Preliminary Information Part Number: ASM2P2310A Document Version: v0.3

Note: This product utilizes US Patent # 6,646,463 Impedance Emulator Patent issued to PulseCore Semiconductor, dated 11-11-2003

© Copyright 2006 PulseCore Semiconductor Corporation. All rights reserved. Our logo and name are trademarks or registered trademarks of PulseCore Semiconductor. All other brand and product names may be the trademarks of their respective companies. PulseCore reserves the right to make changes to this document and its products at any time without notice. PulseCore assumes no responsibility for any errors that may appear in this document. The data contained herein represents PulseCore's best data and/or estimates at the time of issuance. PulseCore reserves the right to change or correct this data at any time, without notice. If the product described herein is under development, significant changes to these specifications are possible. The information in this product data sheet is intended to be general descriptive information for potential customers and users, and is not intended to operate as, or provide, any guarantee or warrantee to any user or customer. PulseCore does not assume any responsibility or liability arising out of the application or use of any product described herein, and disclaims any express or implied warranties related to the sale and/or use of PulseCore products including liability or warranties related to fitness for a particular purpose, merchantability, or infringement of any intellectual property rights, except as express agreed to in PulseCore's Terms and Conditions of Sale (which are available from PulseCore). All sales of PulseCore products are made exclusively according to PulseCore's Terms and Conditions of Sale. The purchase of products from PulseCore does not convey a license under any patent rights, copyrights; mask works rights, trademarks, or any other intellectual property rights of PulseCore or third parties. PulseCore does not authorize its products for use as critical components in life-supporting systems where a malfunction or failure may reasonably be expected to result in significant injury to the user, and the inclusion of PulseCore products in such life-supporting systems implies that the manufacturer assumes all risk of such use and agrees to indemnify PulseCore against all claims arising from such use.