## Power Supply Selector Switch

### **General Description**

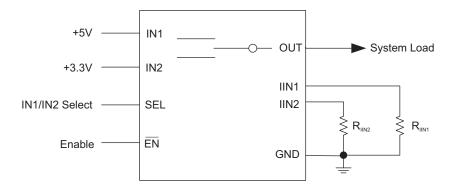

The AAT4674/4674-1 are members of AnalogicTech's Application Specific Power Management SmartSwitch™ family. These devices are dual input single output power supply selector switches designed to operate from batteries, or any other power supply with an input voltage up to 6V.

The AAT4674/4674-1 connects the supply voltage on IN1 to OUT, or IN2 to OUT, through a very low  $R_{\text{DS}(\text{ON})}$  power MOSFET that minimizes voltage drops and power dissipation. The enable  $(\overline{\text{EN}})$  and select (SEL) pin voltages control the operational state of the internal power MOSFET switches. Once enabled, the SEL pin will switch between the IN1 and IN2 inputs. If both input voltages are below the UVLO, then the AAT4674 output floats. In the case of the AAT4674-1, if one of the input voltages is above the UVLO threshold then that input voltage that is above the UVLO threshold is passed through to the output.

The two power switches are current limited and the current limit thresholds can be programmed through the resistors on IIN1 and IIN2 pins respectively.

The AAT4674/4674-1 are available in thermally enhanced, space-saving Pb-free 12-pin TSOPJW packages. The AAT4674/4674-1 are specified for operation over the -40°C to +85°C temperature range.

### **Features**

- Input Voltage Supply Range: 2.5V to 6V

- High Level of Integration:

- Reverse Blocking Diode

- Current Sensing

- Programmable Current Limit

- Single Control Pin Switching

- Break-Before-Make Switch-Over

- Minimum Output Voltage Drop During Change-Over

- Shutdown Current < 1µA

- Thermal Protection

- TSOPJW-12 Package

### **Applications**

- Bluetooth<sup>™</sup> Headsets

- Cell Phones

- Digital Still Cameras

- MP3 Players

- Personal Data Assistants (PDAs)

- · Set Top Boxes

## **Typical Application**

SmartSwitch<sup>TM</sup>

# Power Supply Selector Switch

# **Pin Descriptions**

| Pin Number | Name | Туре | Function                                                               |  |

|------------|------|------|------------------------------------------------------------------------|--|

| 1, 2       | IN1  | I    | Power supply 1 input.                                                  |  |

| 3, 4       | IN2  | I    | Power supply 2 input.                                                  |  |

| 5          | EN   |      | Enable pin, active low.                                                |  |

| 6, 7       | GND  | I/O  | Ground.                                                                |  |

| 8          | SEL  | I    | IN2 or IN1 select input.  Logic '0' → OUT = IN1  Logic '1' → OUT = IN2 |  |

| 9          | IIN2 | I    | IN2-OUT switch current limit set resistor input.                       |  |

| 10         | IIN1 | I    | IN1-OUT switch current limit set resistor input.                       |  |

| 11, 12     | OUT  | 0    | Output pin.                                                            |  |

## **Pin Configuration**

2

# TSOPJW-12 (Top View)

| IN1 🔟 | 12 OUT  |

|-------|---------|

| IN1 2 | 11 OUT  |

| IN2 3 | 10 IIN1 |

| IN2 4 | 9 IIN2  |

| EN 5  | - SEL   |

| GND 6 | ⁻ GND   |

# Power Supply Selector Switch

## Absolute Maximum Ratings<sup>1</sup>

| Symbol            | Description                              | Value                     | Units |

|-------------------|------------------------------------------|---------------------------|-------|

| $V_{INX}$         | [IN1, IN2] to GND                        | -0.3 to 6.5               | V     |

| V <sub>N</sub>    | [OUT, EN, IIN1, IIN2, SEL] to GND        | $-0.3$ to $V_{INX} + 0.3$ | V     |

| T <sub>LEAD</sub> | Maximum Soldering Temperature (at Leads) | 300                       | °C    |

| $I_{OUT}$         | Maximum Output Current                   | 3                         | Ā     |

## Thermal Information<sup>2</sup>

| Symbol         | Description                          | Value      | Units |

|----------------|--------------------------------------|------------|-------|

| $\theta_{JA}$  | Maximum Thermal Resistance           | 160        | °C/W  |

| P <sub>D</sub> | Maximum Power Dissipation            | 625        | mW    |

| Tı             | Operating Junction Temperature Range | -40 to 150 | °C    |

<sup>1.</sup> Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum Rating should be applied at any one time.

<sup>2.</sup> Mounted on a FR4 board.

# Power Supply Selector Switch

## Electrical Characteristics<sup>1</sup>

$V_{INX}$  = 5V,  $T_A$  = -40 to +85°C, unless otherwise noted. Typical values are at  $T_A$  = 25°C.

| Symbol                        | Description                                                                                      | Conditions                                                   | Min | Тур  | Max  | Units |  |

|-------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----|------|------|-------|--|

| Operation                     |                                                                                                  |                                                              |     |      |      |       |  |

| $V_{IN1}$                     | IN1 Operating Voltage Range                                                                      |                                                              | 2.5 |      | 6    | V     |  |

| $V_{IN2}$                     | IN2 Operating Voltage Range                                                                      |                                                              | 2.5 |      | 6    | V     |  |

| $V_{UVLO\_IN1}$               | IN1 Under-Voltage Lockout                                                                        | Rising edge                                                  |     | 0.1  | 2.3  | V     |  |

| _                             |                                                                                                  | Hysteresis                                                   |     | 0.1  | 2.2  |       |  |

| $V_{\text{UVLO}\_\text{IN2}}$ | IN2 Under-Voltage Lockout                                                                        | Rising edge Hysteresis                                       |     | 0.1  | 2.3  | V     |  |

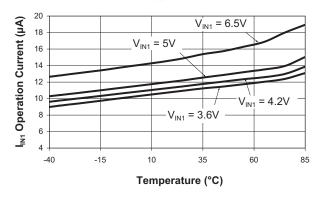

| I <sub>IN1 OP</sub>           | IN1 Normal Operating Current                                                                     | $V_{IN1} = 5V$ , $V_{\overline{EN}} = 0V$                    |     | 10   | 30   | μA    |  |

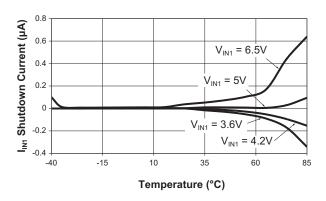

| I <sub>IN1 SHDN</sub>         | IN1 Shutdown Mode Current                                                                        | $V_{IN1} = V_{\overline{EN}} = 5V$ , OUT open                |     |      | 1    | μA    |  |

| I <sub>IN1_SLP</sub>          | IN1 Sleep Current                                                                                | $V_{IN1} = 2.5V$ , $V_{IN2} = 5V$ , $V_{\overline{EN}} = 0V$ |     | 1    | 5    | μA    |  |

| I <sub>IN2 OP</sub>           | IN2 Normal Operating Current                                                                     | $V_{IN2} = 5V$ , $V_{\overline{EN}} = 0V$                    |     | 10   | 30   | μA    |  |

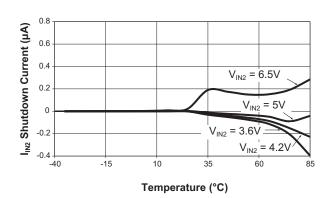

| $I_{\text{IN2\_SHDN}}$        | IN2 Shutdown Mode Current                                                                        | $V_{IN2} = V_{\overline{EN}} = 5V$ , OUT open                |     |      | 1    | μA    |  |

| I <sub>IN2_SLP</sub>          | IN2 Sleep Current                                                                                | $V_{IN1} = 5V, V_{IN2} = 2.5V, V_{\overline{EN}} = 0V$       |     | 1    | 5    | μA    |  |

| Power Sw                      | ritches                                                                                          |                                                              |     |      |      |       |  |

| В                             | INII to OUT FET On Designation                                                                   | $V_{IN1} = 5.0V$                                             |     | 0.12 | 0.15 | Ω     |  |

| R <sub>DS(ON) IN1</sub>       | IN1-to-OUT FET On-Resistance                                                                     | $V_{IN1} = 3.5V$                                             |     | 0.14 | 0.18 |       |  |

| D                             | IN2-to-OUT FET On-Resistance                                                                     | $V_{IN2} = 5.0V$                                             |     | 0.12 | 0.15 | Ω     |  |

| R <sub>DS(ON) IN2</sub>       |                                                                                                  | $V_{IN2} = 3.5V$                                             |     | 0.14 | 0.18 | 32    |  |

| $V_{DROOP\_OUT}$              | OUT Voltage Droop From the Lower Voltage of IN1 and IN2, When Switching Over Between IN1 and IN2 | $I_{O(OUT)} = 0.5A, C_{O(OUT)} = 10\mu F$                    |     | 150  |      | mV    |  |

| Current R                     | · · · · · · · · · · · · · · · · · · ·                                                            |                                                              |     |      |      |       |  |

| t <sub>SOFT START</sub>       | Soft-Start Delay                                                                                 | Delay of start from EN, or UVLO                              |     | 100  |      | μs    |  |

| I <sub>LIM_range</sub>        | IN1/IN2 Current Limit Range                                                                      |                                                              | 0.2 |      | 2.0  | A     |  |

| I <sub>LIM ACC</sub>          | IN1/IN2 Current Limit Accuracy                                                                   | $R_{IIN1/IIN2} = 100k\Omega$                                 | 0.8 | 1    | 1.2  | Α     |  |

| Logic Control / Protection    |                                                                                                  |                                                              |     |      |      |       |  |

| $V_{IH(\overline{EN})}$       | Logic High Threshold                                                                             |                                                              | 1.6 |      |      | V     |  |

| $V_{IL(\overline{EN})}$       | Logic Low Threshold                                                                              |                                                              |     |      | 0.4  | V     |  |

|                               | Chin Thormal Chutdown Tomporature                                                                | Threshold                                                    |     | 140  |      | °C    |  |

| T <sub>SHDN</sub>             | Chip Thermal Shutdown Temperature                                                                | Hysteresis                                                   |     | 15   |      | 10    |  |

<sup>1.</sup> The AAT4674 is guaranteed to meet performance specifications over the -40°C to +85°C operating temperature range and is assured by design, characterization, and correlation with statistical process controls.

## Power Supply Selector Switch

## **Typical Characteristics**

### I<sub>IN1</sub> Shutdown Current vs. Temperature

### I<sub>IN2</sub> Shutdown Current vs. Temperature

# $I_{IN1}$ Operation Current vs. Temperature $(I_{OUT} = 0A)$

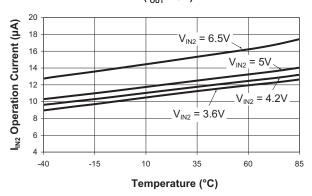

$I_{IN2}$  Operation Current vs. Temperature  $(I_{OUT} = 0A)$

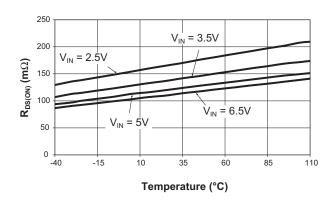

### R<sub>DS(ON)</sub> vs. Temperature

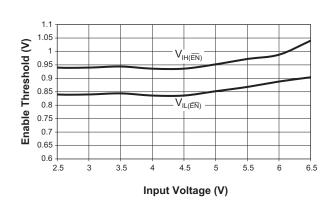

### **Enable Threshold vs. Input Voltage**

# **Power Supply Selector Switch**

## **Typical Characteristics**

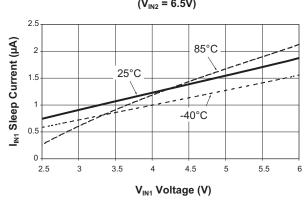

I<sub>IN1</sub> Sleep Current vs. V<sub>IN1</sub> Voltage (V<sub>IN2</sub> = 6.5V)

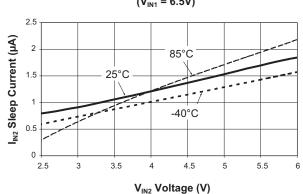

$\begin{array}{c} \textbf{I}_{\text{IN2}} \text{ Sleep Current vs. } \textbf{V}_{\text{IN2}} \text{ Voltage} \\ (\textbf{V}_{\text{IN1}} = 6.5 \text{V}) \end{array}$

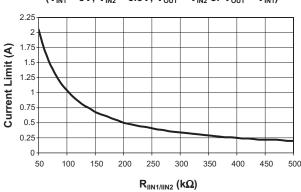

Current Limit vs.  $R_{IIN1/IIN2}$ ( $V_{IN1}$  = 5V;  $V_{IN2}$  = 3.3V;  $V_{OUT}$  =  $V_{IN2}$  or  $V_{OUT}$  =  $V_{IN1}$ )

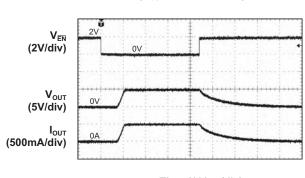

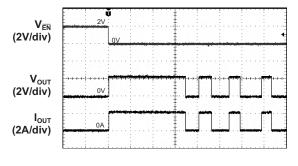

Turn-On/Off Response  $(R_{OUT} = 10\Omega; V_{IN} = 5V)$

Time (100µs/div)

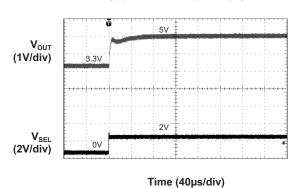

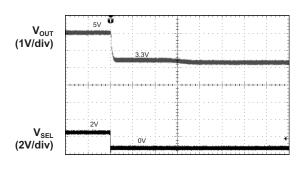

3.3V to 5V Transition Response ( $I_{OUT}$  = 500mA,  $C_{OUT}$  = 10 $\mu$ F)

5V to 3.3V Transition Response ( $I_{OUT}$  = 500mA,  $C_{OUT}$  = 10 $\mu$ F)

Time (40µs/div)

## Power Supply Selector Switch

## **Typical Characteristics**

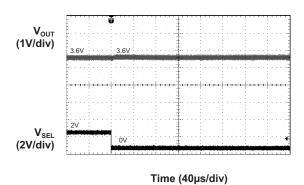

3.6V to 3.6V Transition Response (I<sub>OUT</sub> = 500mA, C<sub>OUT</sub> = 10µF)

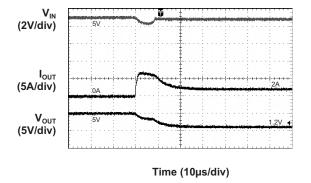

Short Circuit Through  $0.6\Omega$  Response

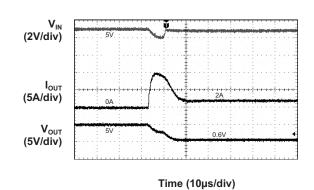

### Short Circuit Through 0.3Ω Response

# Thermal Shutdown Response (V<sub>IN</sub> = 5V)

Time (40ms/div)

## Power Supply Selector Switch

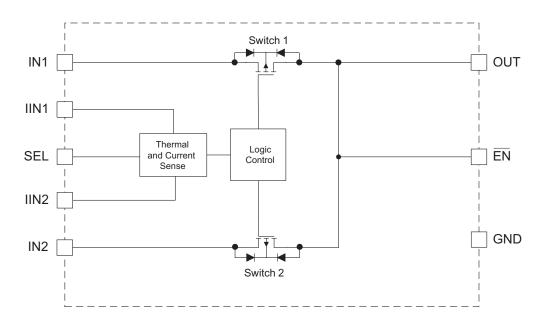

## **Functional Block Diagram**

### **Truth Table**

Y = Yes, N = No, X = don't care.

|                         | Input Conditions        | AAT4674 | AAT4674-1        |                  |  |

|-------------------------|-------------------------|---------|------------------|------------------|--|

| V <sub>IN1</sub> > UVLO | V <sub>IN2</sub> > UVLO | SEL     | V <sub>out</sub> | V <sub>out</sub> |  |

| N                       | N                       | X       | Floating         | Floating         |  |

| Y                       | N                       | X       | Floating         | V <sub>IN1</sub> |  |

| N                       | Y                       | X       | Floating         | V <sub>IN2</sub> |  |

| Y                       | Y                       | 0       | $V_{IN1}$        | $V_{IN1}$        |  |

| Y                       | Y                       | 1       | V <sub>IN2</sub> | VIND             |  |

## **Functional Description**

To power the output, both input supplies (IN1 and IN2) must be above the UVLO threshold. If either supply input is below the UVLO threshold then the output will float or, in the case of the AAT4674-1 the output will be the input supply that is above the UVLO threshold. If both supplies are above the UVLO threshold and the device is enabled, the AAT4674/AAT4674-1 will connect the supply from IN1 to OUT when the SEL pin is LOW (logic '0'), and when the SEL pin is HIGH (logic '1') then the supply on IN2 is connected to the OUT pin. Consult the above "Truth Table" for the summarized AA4674/4674-1 operational details.

The two internal power switches are current limited and the limiting thresholds can be programmed through the resistors on the IIN1 and IIN2 pins respectively.

## **Applications Information**

### **Input Capacitors**

A 1µF or greater capacitor is generally recommended between IN1 and GND ( $C_{\text{IN1}}$ ), and between IN2 and GND ( $C_{\text{IN2}}$ ). An input capacitor is not required for basic operation; however, it is useful in preventing load transients from affecting up-stream circuits. Ceramic, tantalum, or aluminum electrolytic capacitors may be selected for  $C_{\text{IN1}}/C_{\text{IN2}}$ . There is no specific capacitor equivalent series resistance (ESR) requirement for  $C_{\text{IN1}}/C_{\text{IN2}}$ . However, for higher current operation, ceramic capacitors are recommended for  $C_{\text{IN1}}/C_{\text{IN2}}$  due to their inherent capability over tantalum capacitors to withstand input current surges from low impedance sources such as batteries in portable devices.

### Power Supply Selector Switch

### **Output Capacitor**

A 1 $\mu$ F or greater capacitor is required between OUT and GND ( $C_{\text{OUT}}$ ). As with the input capacitor, there is no specific capacitor ESR requirement. If desired,  $C_{\text{OUT}}$  may be increased to accommodate any load transient condition.

### **EN** Input

The AAT4674/4674-1 is enabled when  $V_{EN}$  is  $\leq 0.4V$  (logic '0'), conversely the AAT4674/4674-1 is disabled when  $V_{EN}$  is  $\geq 1.6V$  (logic '1').

### **SEL Input**

When  $V_{\text{SEL}}$  is  $\leq 0.4V$  (logic '0') the output voltage equals power supply 1 input  $(V_{\text{OUT}} = V_{\text{IN1}})$ , and conversely when  $V_{\text{SEL}}$  is  $\geq 1.6V$  (logic '1') the output voltage equals power supply 2 input  $(V_{\text{OUT}} = V_{\text{IN2}})$ .

#### **Current Limit Resistor Selection**

The current limits for power supply 1 and power supply 2 inputs are set by resistors connected between IIN1/IIN2 and GND. The following equation can be used to select the appropriate resistor for a particular current limit:

$$I_{\text{CLINX}} = \left(\frac{V_{\text{IINX}}}{R_{\text{IINX}}}\right) \cdot 200k$$

$I_{CLINX}$  Current limit for IN1 and/or IN2 pins respectively  $V_{IINX}$  Internally Regulated Voltage [0.5V  $\pm$  20%] on the

IIN1 and IIN2 pins respectively

R<sub>IINX</sub> IIN1 and/or IIN2 Resistor

200k Internal Gain Factor

### **Design Example**

A particular application requires that the current limit for IN1 be set to 2A and the current limit for IN2 be set to 0.2A. What value of resistor is required for the IIN1 and IIN2 pins respectively?

For IN1 (power supply 1 input):

$$R_{IIN1} = \left(\frac{V_{IIN1}}{I_{CLIN1}}\right) \cdot 200k$$

$$= \left(\frac{0.5V}{2A}\right) \cdot 200k$$

$$= 50k\Omega (49.9k\Omega \text{ standard value})$$

For IN2 (power supply 2 input):

$$R_{IIN2} = \left(\frac{V_{IIN2}}{I_{CLIN2}}\right) \cdot 200k$$

$$= \left(\frac{0.5V}{0.2A}\right) \cdot 200k$$

=  $500k\Omega$  (499.9k $\Omega$  standard value)

### **Thermal Considerations**

Since the AAT4674/4674-1 have an internal current limit and over-temperature protection (thermal shutdown), junction temperature is rarely a concern. However, if the application requires large currents in a high temperature environment, it is possible that temperature rather than current limit will be the dominant regulating condition. In these applications, the maximum current available without risk of an over-temperature condition must be calculated. The maximum internal temperature while current limit is not active can be calculated using Equation 1 (Eq. 1).

Eq. 1:

$$T_{J(MAX)} = I_{MAX}^2 \cdot R_{DS(ON)(MAX)} \cdot R_{\theta JA} + T_{A(MAX)}$$

In Equation 1,  $I_{MAX}$  is the maximum current required by the load.  $R_{DS(ON)(MAX)}$  is the maximum rated  $R_{DS(ON)}$  of the AAT4674/4674-1 at high temperatures (consult the " $R_{DSON}$  vs. Temperature" performance graph in the "Typical Characteristics" section of this datasheet). For estimating the  $R_{DS(ON)(MAX)}$  use the data on the " $R_{DSON}$  vs Temperature" performance graph and increase the value from the performance graph by 50%.  $R_{\theta JA}$  is the thermal resistance between the AAT4674/4674-1 and the printed circuit board (PCB) onto which it is mounted;  $R_{\theta JA}$  is the thermal resistance of the TSOPJW-12 package.  $T_{A(MAX)}$  is the maximum ambient temperature that the PCB under the AAT4674/4674-1 would be if the AAT4674/4674-1 were not dissipating power. Equation 1 can be rearranged to solve for  $I_{MAX}$ , into Equation 2 (Eq. 2).

Eq. 2:

$$I_{MAX} = \sqrt{\frac{T_{SD(MIN)} - T_{A(MAX)}}{R_{DS(ON)(MAX)} \cdot R_{\Theta JA}}}$$

$T_{\text{SD(MIN)}}$  is the minimum temperature required to activate the AAT4674/4674-1 over-temperature protection (thermal shutdown). With typical specification of 140°C, 125°C is a safe minimum value to use.

### Power Supply Selector Switch

For example, for a 2.5V input power supply application that is specified to operate in 50°C environments where the PCB operates at temperatures as high as 85°C. The application is sealed and its PCB is small, causing  $R_{\text{BJA}}$  to be approximately 160°C/W. The  $R_{\text{DS(ON)}(\text{MAX})}$  is estimate to be  $300\text{m}\Omega$  (from the " $R_{\text{DS(ON)}}$  vs. Temperature" performance graph, where  $V_{\text{IN}}=2.5\text{V}$  at 85°C plus 50%). To find the maximum current ( $I_{\text{MAX}}$ ) for this application use Equation 2:

$$I_{MAX} = \sqrt{\frac{125^{\circ}\text{C} - 85^{\circ}\text{C}}{300\text{m}\Omega \cdot 160^{\circ}\text{C/W}}} = 0.913\text{A}$$

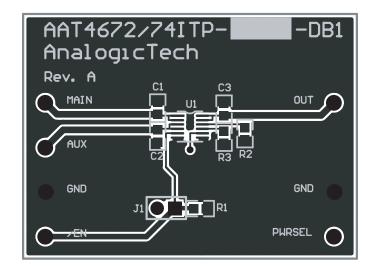

## PCB Layout Recommendations

For proper thermal management, to minimize PCB trace resistance, and to take advantage of the low  $R_{\rm DS(ON)}$  values of the two internal power switches in the AAT4674/4674-1, certain circuit board layout rules should be followed: IN1, IN2, and OUT should be routed using wider than normal traces. The two IN1 pins (1 and 2) and two IN2 pins (3 and 4) should be connected to the same wide PCB trace; and GND should be connected to a ground plane. For best performance, the input capacitors ( $C_{\rm IN1}/C_{\rm IN2}$ ) and output capacitors ( $C_{\rm OUT}$ ) should be placed as close to the package pins as possible. The AAT4674/4674-1 evaluation board layout follows the printed circuit board layout recommendations and can be used as an example of an optimal board layout.

## **Power Supply Selector Switch**

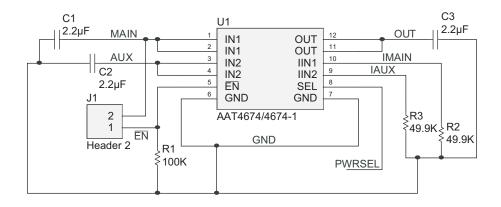

### **Evaluation Board Schematic**

Figure 1: AAT4674/AAT4674-1 Evaluation Board Schematic.

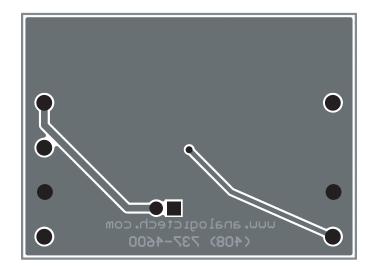

### **Evaluation Board Layout**

Figure 2: AAT4674/AAT4674-1 Evaluation Board Top Side Layout.

Figure 3: AAT4674/AAT4674-1 Evaluation Board Bottom Side Layout.

### Power Supply Selector Switch

### Ordering Information

| Package   | Marking <sup>1</sup> | Part Number (Tape and Reel) <sup>2</sup> |

|-----------|----------------------|------------------------------------------|

| TSOPJW-12 | ZVXYY                | AAT4674ITP-T1                            |

| TSOPJW-12 | YTXYY                | AAT4674ITP-1-T1                          |

All AnalogicTech products are offered in Pb-free packaging. The term "Pb-free" means semiconductor products that are in compliance with current RoHS standards, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. For more information, please visit our website at http://www.analogictech.com/about/quality.aspx.

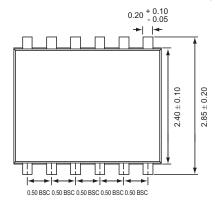

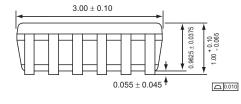

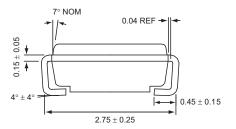

### **Package Information**

#### TSOPJW-12

All dimensions in millimeters.

- 1. XYY = assembly and date code.

- 2. Sample stock is generally held on part numbers listed in **BOLD**.

### Advanced Analogic Technologies, Inc.

3230 Scott Boulevard, Santa Clara, CA 95054 Phone (408) 737-4600 Fax (408) 737-4611

© Advanced Analogic Technologies, Inc.

(a) Advanced Analogic Technologies, Inc.

Analogic Tech cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in an AnalogicTech product. No circuit patent licenses, copyrights, mask work rights, or other intellectual property rights are implied. AnalogicTech reserves the right to make changes to their products or specifications or to discontinue any product or service without notice. Except as provided in AnalogicTech's terms and conditions of sale, AnalogicTech assumes no liability whatsoever, and AnalogicTech disclaims any express or implied warranty relating to the sale and/or use of AnalogicTech products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. Testing and other quality control techniques are utilized to the extent AnalogicTech deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed. AnalogicTech and the AnalogicTech logo are trademarks of Advanced Analogic Technologies Incorporated. All other hazards are appeared in this development are recitatived factorizations to the dependence of the interpretation bedden. brand and product names appearing in this document are registered trademarks or trademarks of their respective holders