# LMX5251 Bluetooth™ CMOS Radio

Check for Samples: LMX5251

## **FEATURES**

- **Bluetooth Version 1.1 Qualified**

- Flexible Radio Frequency (RF) to Baseband (BB) Interface

- LOW POWER

- Low Current Consumption

- Power Management Control Functions

- **HIGH PERFORMANCE**

- < -82 dBm Sensitivity

- Class 2/3 Operation

- ± 1/12 Bit Sampling Resolution

- Closed LoopM ΔΣ Modulation

- **HIGH INTEGRATION**

- Low IF (Intermediate Frequency) **Architecture with Digital Demodulation**

- **Integrated Radio Frequency Voltage** Controlled Oscillator (RFVCO)

- Dual on-chip Voltage Regulators:)

- Input Voltages 2.85V–3.6V

- Output Nominally 2.5VM

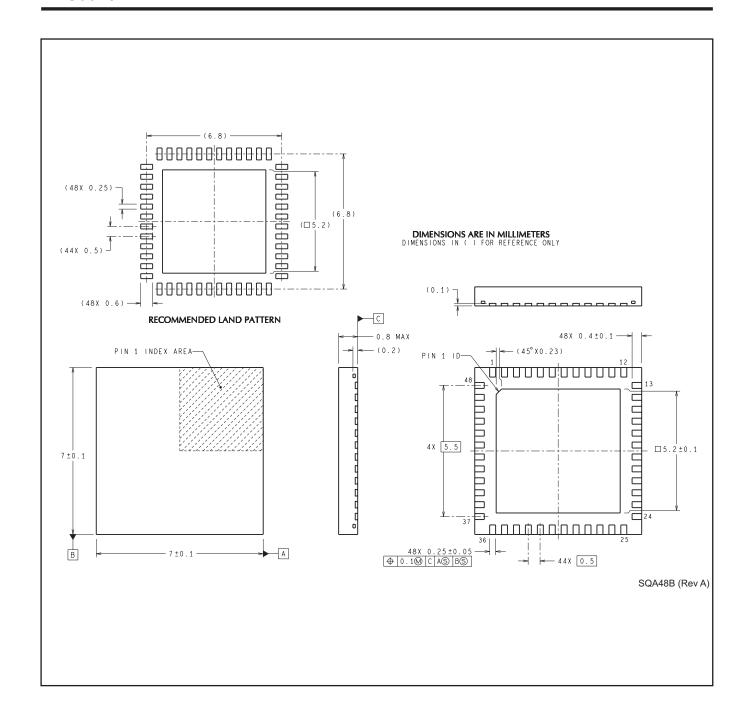

- 48-pin WQFN (Thin Quad Flatpack No lead) **Package**

- No Pb Leadframe LMX5251SQ NOPB

## **APPLICATIONS**

- **Bluetooth Compatible Interface Devices**

- Cellular and Cordless Phones, PDAs

- Desktop and Laptop PCs, Printers, Scanners

- Other Wireless-Interfaced Appliances

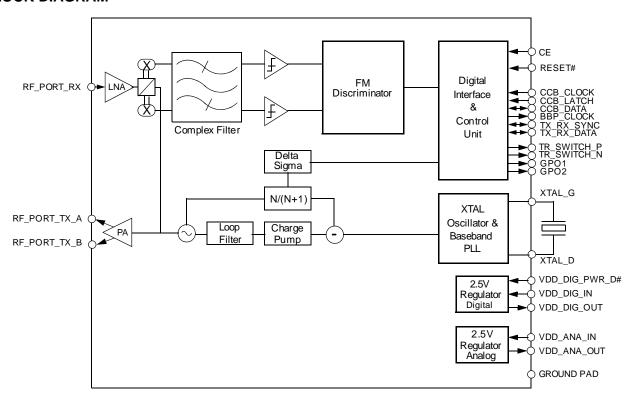

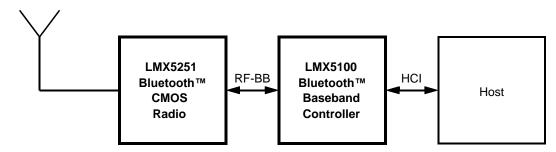

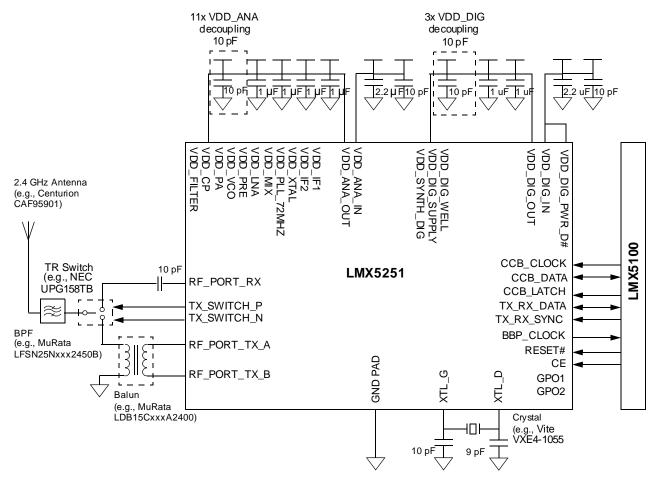

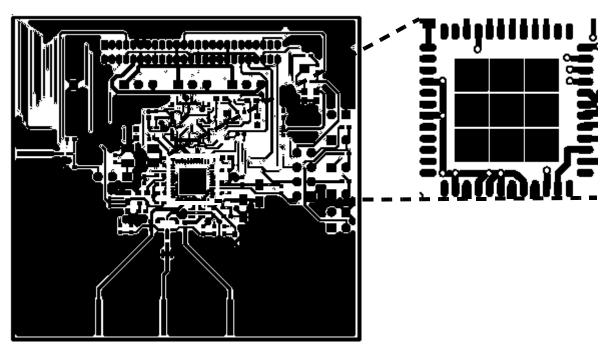

#### **BLOCK DIAGRAM**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. Bluetooth is a trademark of Bluetooth Sig, Inc.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## **DESCRIPTION**

The LMX5251 is a high performance, monolithic, radio transceiver optimized for Bluetooth<sup>™™</sup> communications systems. When used in conjunction with a Bluetooth baseband controller, a complete Bluetooth node with a Host Control Interface (HCI) can be implemented.

The LMX5251 radio architecture allows for minimal external components. The highly integrated design includes the Low Noise Amplifier (LNA), mixer, on-chip filters, 2.5 GHz delta-sigma phase-lock loop ( $\Delta\Sigma$  PLL), voltage controlled oscillator, modem functions, and dual power supply regulators. Digital modulation and demodulation techniques are utilized for a robust manufacturable design. Power management includes control over individual chip functions and internal voltage regulation for optimum performance.

The LMX5251 modem circuitry provides the data communication link to the Bluetooth baseband controller. The interface is flexible and works with solutions that require a standalone Bluetooth radio. The LMX5251 can be placed in Sleep mode (reducing system current consumption) and is optimized for low power operation. It operates from a single 2.85V to 3.6V power supply.

The LMX5251 is manufactured using a CMOS process and is available in a 48-pin WQFN (Thin Quad Flatpack, No lead) package. Die processing is also available through Texas Instruments Die Products Group.

The LMX5251 is the most recent revision of the LMX5250 and is completely interoperable with the LMX5100 Bluetooth Baseband Controller.

## **CONTENTS**

| FEATURES                                       | 1  |

|------------------------------------------------|----|

| APPLICATIONS                                   |    |

| DESCRIPTION                                    |    |

| ELECTRICAL SPECIFICATIONS                      | 6  |

| ABSOLUTE MAXIMUM RATINGS                       |    |

| RECOMMENDED OPERATING CONDITIONS               | 7  |

| POWER SUPPLY ELECTRICAL SPECIFICATIONS         |    |

| DC CHARACTERISTICS DIGITAL I/O                 | 7  |

| RECEIVER PERFORMANCE CHARACTERISTICS           |    |

| TRANSMITTER PERFORMANCE CHARACTERISTICS        |    |

| CRYSTAL/OSCILLATOR PERFORMANCE CHARACTERISTICS | ç  |

| AC CHARACTERISTICS SERIAL INTERFACE TIMING1    |    |

| PERFORMANCE PARAMETERS (TYPICAL)1              | 11 |

| FUNCTIONAL DESCRIPTION1                        | 13 |

| APPLICATION INFORMATION                        | 2( |

| Revision History                               | 32 |

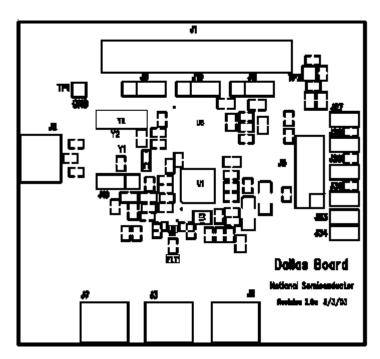

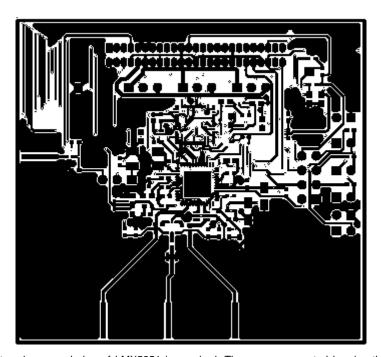

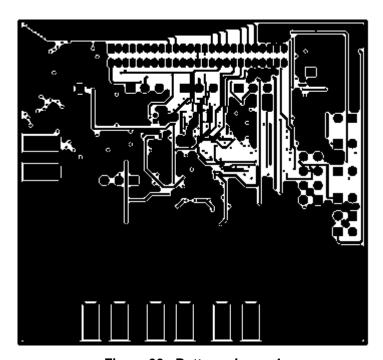

NOTE: Ground pad layout under ground slug of LMX5251 is required. These are connected by vias through all layers to ground plane. No pins on device are ground pins so center slug must be grounded. See detail in Figure 27 "Component Placement Layer 1 Ground Pad Detail".

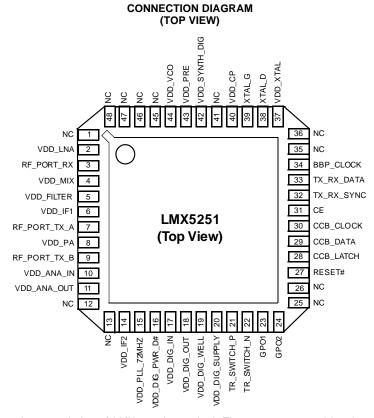

## **PIN FUNCTIONS**

|              |                                               |     | T T T T T T T T T T T T T T T T T T T                                                                                                                                                                                |

|--------------|-----------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN          | T                                             | 1/0 | DESCRIPTION                                                                                                                                                                                                          |

| NAME         | NO.                                           |     | DEGGINI HON                                                                                                                                                                                                          |

| NC           | 1, 12, 13,<br>25, 26, 35,<br>36, 41,<br>45–48 | -   | No Connect. Place pin but do not connect to VCC or Ground.                                                                                                                                                           |

| VDD_LNA      | 2                                             | PWR | <b>Power Supply for Analog Circuitry.</b> Must be connected to the VDD_ANA_OUT pin (pin 11) or external supply. An RF bypass capacitor should be placed as close as possible to this pin and be connected to Ground. |

| RF_PORT_RX   | 3                                             | I   | RF Input to Receiver.                                                                                                                                                                                                |

| VDD_MIX      | 4                                             | PWR | <b>Power Supply for Analog Circuitry.</b> Must be connected to the VDD_ANA_OUT pin (pin 11) or external supply. An RF bypass capacitor should be placed as close as possible to this pin and be connected to Ground. |

| VDD_FILTER   | 5                                             | PWR | Power Supply for Analog Circuitry. Must be connected to the VDD_ANA_OUT pin (pin 11) or external supply. An RF bypass capacitor should be placed as close as possible to this pin and be connected to Ground.        |

| VDD_IF1      | 6                                             | PWR | Power Supply for Analog Circuitry. Must be connected to the VDD_ANA_OUT pin (pin 11) or external supply. An RF bypass capacitor should be placed as close as possible to this pin and be connected to Ground.        |

| RF_PORT_TX_A | 7                                             | 0   | <b>Transmit Positive Differential Output.</b> Typically connected along with RF_PORT_TX_B to a balun and fed to the antenna.                                                                                         |

| VDD_PA       | 8                                             | PWR | Power Supply for Analog Circuitry. Must be connected to the VDD_ANA_OUT pin (pin 11) or external supply. An RF bypass capacitor should be placed as close as possible to this pin and be connected to Ground.        |

Copyright © 2004–2013, Texas Instruments Incorporated

# **PIN FUNCTIONS (continued)**

| PIN            |     |     | 1 IN 1 ONO FIGHE (COMMITTEE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME           | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RF_PORT_TX_B   | 9   | 0   | <b>Transmit Inverted Differential Output.</b> Typically connected along with RF_PORT_TX_A to a balun and fed to the antenna.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VDD_ANA_IN     | 10  | PWR | 2.85V to 3.6V Input for the Internal Power Supply Regulator for the RF Circuitry. Powered down when CE (pin 31) is held low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VDD_ANA_OUT    | 11  | PWR | Voltage Regulator Output/Power Supply for Analog Circuitry. The bypass capacitor should be placed as close as possible to this pin and be connected to Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VDD_IF2        | 14  | PWR | <b>Power Supply for Analog Circuitry.</b> Must be connected to the VDD_ANA_OUT pin (pin 11) or external supply. An RF bypass capacitor should be placed as close as possible to this pin and be connected to Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VDD_PLL_72MHZ  | 15  | PWR | <b>Power Supply for Analog Circuitry.</b> Must be connected to the VDD_ANA_OUT pin (pin 11) or external supply. An RF bypass capacitor should be placed as close as possible to this pin and be connected to Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VDD_DIG_PWR_D# | 16  | I   | Power Down for the Internal Power Supply Regulator for the Digital Circuitry. Digital regulator is powered down when low. Default operation is on, internal pull-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VDD_DIG_IN     | 17  | PWR | 2.85V to 3.6V Input for the Internal Power Supply Regulator for the Digital Circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VDD_DIG_OUT    | 18  | PWR | <b>Voltage Regulator Output/Power Supply for Digital Circuitry.</b> A bypass capacitor should be placed as close as possible to this pin and be connected to Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VDD_DIG_WELL   | 19  | PWR | <b>Power Supply for Digital Circuitry.</b> Must be connected to the VDD_DIG_OUT pin (pin 18) or external supply. A bypass capacitor should be placed as close as possible to this pin and be connected to Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VDD_DIG_SUPPLY | 20  | PWR | <b>Power Supply for Digital Circuitry.</b> Must be connected to the VDD_DIG_OUT pin (pin 18) or external supply. A bypass capacitor should be placed as close as possible to this pin and be connected to Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TR_SWITCH_P    | 21  | 0   | Output Control for RF T/R Switch. The complement of TR_SWITCH_N. When the LMX5251 is transmitting, TR_SWITCH_P is high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TR_SWITCH_N    | 22  | 0   | Output Control for RF T/R Switch. The complement of TR_SWITCH_P. When the LMX5251 is receiving, TR_SWITCH_N is high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| GPO1           | 23  | 0   | <b>General Purpose Output 1.</b> The multifunction output state is programmed by setting an internal register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GPO2           | 24  | 0   | <b>General Purpose Output 2.</b> The multifunction output state is programmed by setting an internal register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RESET#         | 27  | I   | Master Power on Inverted Reset Input. Internal registers revert to default values while RESET# is low. The power control register default state enables only the crystal oscillator and BBP_CLOCK blocks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

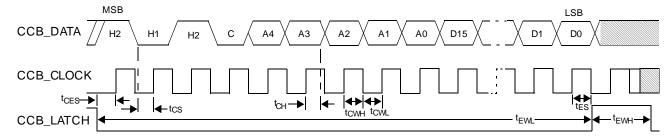

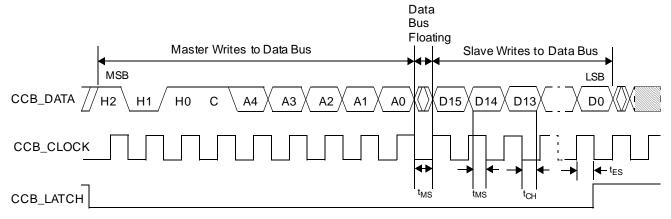

| CCB_LATCH      | 28  | I   | Load Enable Signal of the Serial Interface. During write operations (baseband controller writes into LMX5251 registers) the data received by the shift register of the LMX5251 is copied into the address register on the next rising edge of CCB_CLOCK after the CCB_LATCH signal has transitioned to high. During read operations (read from LMX5251 registers) the LMX5251 releases the CCB_DATA line on the next rising edge of CCB_CLOCK after the CCB_LATCH signal has transitioned to high. Reference serial port timing Figure 19 and Figure 20.                                                                                                                                                          |

| CCB_DATA       | 29  | I/O | Multiplexed Serial Data Receive and Transmit Signal Path. For a write operation, data is clocked into the LMX5251 shift register in the direction from the most significant bit (MSB) to the least significant bit (LSB). The data is shifted out of the baseband controller on the falling edge of CCB_CLOCK, and sampled by the LMX5251 (CCB_DATA) on the rising edge of CCB_CLOCK. For a read operation, data is clocked out of the LMX5251 shift register in the direction from MSB to LSB. The data is shifted out of the LMX5251 (CCB_DATA) on the rising edge of CCB_CLOCK, and sampled by the baseband controller on the falling edge of CCB_CLOCK. Reference serial port timing Figure 19 and Figure 20. |

| CCB_CLOCK      | 30  | I   | Serial Interface Shift Clock Signal. The baseband controller always acts as the master of the serial interface and therefore always provides the shift clock. This clock can be asynchronous with the BBP_CLOCK and is assumed to be gated by the baseband controller. Reference serial port timing Figure 19 and Figure 20.                                                                                                                                                                                                                                                                                                                                                                                      |

| CE             | 31  | I   | Chip Enable Input. All analog blocks and the analog regulator are off and there is no BBP_CLOCK signal. All digital blocks and the digital regulator are on.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TX_RX_SYNC     | 32  | I/O | Transmit and Receive Slot Timing Synchronization.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# **PIN FUNCTIONS (continued)**

| PIN           |     | 1/0 | DECORPORION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|---------------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME          | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| TX_RX_DATA    | 33  | I/O | Multiplexed Transmit and Receive Bluetooth Data. In receive mode (Bluetooth data direction from LMX5251 to baseband controller), this signal is provided by the LMX5251 demodulator (RX_DATA) to the baseband coNtroller data receiver oversampled at a 12x multiple of the 1.0 Mbit/s rate.                                                                                                                                                                                                        |  |  |

|               |     |     | In transmit mode, (Bluetooth data direction from baseband controller to LMX5251) this signal is provided by the baseband controller packet generator to the LMX5251 modulator (TX_DATA) at a 1.0 Mb/s rate. A pulse on this bus provided by the baseband controller prior to the beginning of data transmission is used to synchronize the LMX5251 to the baseband controller to an internal 1.0 MHz transmit clock timing.                                                                         |  |  |

| BBP_CLOCK     | 34  | 0   | <b>Buffered 12.000 MHz Clock.</b> This 12 MHz clock is provided by the LMX5251 and is used by the baseband controller as the fast system clock (main clock). The 12 MHz clock is also used in the LMX5251 demodulator and baseband controller data receiver as the sampling clock (12 times over-sampling) for the Bluetooth data. During Bluetooth low power modes, the XTAL oscillator and BBP_CLOCK output of the LMX5251 can be disabled. Upon RESET# being low, this pin is in TRI-STATE mode. |  |  |

| VDD_XTAL      | 37  | PWR | <b>Power Supply for Analog Circuitry.</b> Must be connected to the VDD_ANA_OUT pin (pin 11) or external supply. An RF bypass capacitor should be placed as close as possible to this pin and be connected to Ground.                                                                                                                                                                                                                                                                                |  |  |

| XTAL_D        | 38  | I   | Crystal Drain Oscillator or Positive Clock Input. Typically connected along with XTAL_G to an external surface mount AT cut crystal. Can also be configured as a frequency input when using an external crystal oscillator. When configured as a frequency input, it is typically connected to Ground with a 100 pF capacitor.                                                                                                                                                                      |  |  |

| XTAL_G        | 39  | I   | Crystal Gate Oscillator or Negative Clock Input. Typically connected along with XTAL_D to an external surface mount AT cut crystal. Can also be configured as a frequency input when using an external crystal oscillator. When configured as a frequency input, is typically connected to an external Temperature Compensated Crystal Oscillator (TCXO) through an Alternating Current (AC) coupling capacitor.                                                                                    |  |  |

| VDD_CP        | 40  | PWR | Power Supply for Analog Circuitry. Must be connected to the VDD_ANA_OUT pin (pin 11) or external supply. An RF bypass capacitor should be placed as close as possible to this pin and be connected to Ground.                                                                                                                                                                                                                                                                                       |  |  |

| VDD_SYNTH_DIG | 42  | PWR | Power Supply for Digital Circuitry. Must be connected to the VDD_DIG_OUT pin (pin 18) or external supply. A bypass capacitor should be placed as close as possible to this pin and be connected to Ground.                                                                                                                                                                                                                                                                                          |  |  |

| VDD_PRE       | 43  | PWR | <b>Power Supply for Analog Circuitry.</b> Must be connected to the VDD_ANA_OUT pin (pin 11) or external supply. An RF bypass capacitor should be placed as close as possible to this pin and be connected to Ground.                                                                                                                                                                                                                                                                                |  |  |

| VDD_VCO       | 44  | PWR | <b>Power Supply for Analog Circuitry.</b> Must be connected to the VDD_ANA_OUT pin (pin 11) or external supply. An RF bypass capacitor should be placed as close as possible to this pin and be connected to Ground.                                                                                                                                                                                                                                                                                |  |  |

Copyright © 2004–2013, Texas Instruments Incorporated Submit Documentation Feedback

Product Folder Links: LMX5251

#### **ELECTRICAL SPECIFICATIONS**

#### **GENERAL SPECIFICATIONS**

The ABSOLUTE MAXIMUM RATINGS table indicate limits beyond which damage to the device may occur. The RECOMMENDED OPERATING CONDITIONS table indicate conditions for which the device is intended to be functional, but do not specify specific performance limits.

This device is a high performance RF integrated circuit and is ESD sensitive. Handling and assembly of this device should be performed at ESD free workstations.

The following conditions are true unless otherwise stated in the tables below:

- $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$

- VDD\_ANA\_IN and VDD\_DIG\_IN = 3.3V

- RF system performance specifications are specified on Texas Instruments Dallas Board rev 2.0a reference design platform.

- Reference Dallas Board rev 2.0a schematic for test point references.

#### **ABSOLUTE MAXIMUM RATINGS**

|                    |                                       | MIN  | MAX                 | UNIT |

|--------------------|---------------------------------------|------|---------------------|------|

| VDD_ANA_IN         | Analog LDO voltage input              | -0.2 | 3.6                 | V    |

| VDD_DIG_IN         | Digital LDO voltage input             | -0.2 | 3.6                 | V    |

| VDD_XXXXX          | All other power supply voltage inputs | -0.2 | 2.75                | V    |

| V <sub>I</sub>     | Voltage on any pin with GND = 0V      | -0.2 | VDD + 0.2           | V    |

| PinRF              | RF Input power                        |      | +15                 | dBm  |

| T <sub>S</sub>     | Storage temperature range             | -65  | +150                | °C   |

| $T_L$              | Lead temperature (solder 4 sec)       |      | +235                | °C   |

| T <sub>NOPBL</sub> | No Pb lead temperature (solder 4 sec) |      | +260                | °C   |

| ESD-HBM            | ESD – Human Body Model                |      | 2000 <sup>(1)</sup> | V    |

| ESD-MM             | ESD – Machine Model                   |      | 200                 | V    |

(1) A 2000V ESD rating applies to all pins except VDD\_IF1(pin 6) = 1500V.

#### RECOMMENDED OPERATING CONDITIONS

|                |                                            | MIN  | TYP <sup>(1)</sup> | MAX  | UNIT |

|----------------|--------------------------------------------|------|--------------------|------|------|

| VDD_ANA_IN     |                                            | 2.85 | 3.3                | 3.6  | V    |

| VDD_LNA        |                                            |      |                    |      |      |

| VDD_FILTER     |                                            |      |                    |      |      |

| VDD_IF1        |                                            |      |                    |      |      |

| VDD_PA         | Analog power supply voltage <sup>(2)</sup> |      |                    |      |      |

| VDD_IF2        |                                            |      |                    |      |      |

| VDD_PLL        |                                            | 2.25 | 2.5                | 2.75 | V    |

| VDD_MIX        |                                            |      |                    |      |      |

| VDD_XTAL       |                                            |      |                    |      |      |

| VDD_CP         |                                            |      |                    |      |      |

| VDD_PRE        |                                            |      |                    |      |      |

| VDD_VCO        |                                            |      |                    |      |      |

| VDD_DIG_IN     |                                            | 2.85 | 3.3                | 3.6  | V    |

| VDD_DIG_WELL   | Digital power supply voltage (2)           |      |                    |      |      |

| VDD_DIG_SUPPLY |                                            | 2.25 | 2.5                | 2.75 | V    |

| VDD_SYNTH_D    |                                            |      |                    |      |      |

| T <sub>S</sub> | Operating temperature range                | -40  |                    | 85   | °C   |

- (1) Typical operating conditions are at 3.3V operating voltage and 25°C ambient temperature.

- (2) Maximum voltage difference between input voltage for analog VDD and digital VDD is 500 mV.

## POWER SUPPLY REQUIREMENTS(1)

|                                      | PARAMETER                                                   | MIN TYP <sup>(2)</sup> | MAX | UNIT |

|--------------------------------------|-------------------------------------------------------------|------------------------|-----|------|

| I <sub>CC</sub> -RX                  | Receive power supply current (receive in Continuous mode)   | 62                     | 78  | mA   |

| I <sub>CC</sub> -TX                  | Transmit power supply current (transmit in Continuous mode) | 56                     | 68  | mA   |

| I <sub>CC</sub> -PWDN <sup>(3)</sup> | Power-down current                                          | 24                     | 200 | μΑ   |

- (1) Power supply requirements based on Class II output power.

- (2) Typical operating conditions are at 2.85V operating voltage and 25°C ambient temperature.

- (3) CE and V<sub>DD</sub>\_DIG\_PWR\_D# low.

## POWER SUPPLY ELECTRICAL SPECIFICATIONS

|                            | PARAMETER                                              | MIN  | TYP <sup>(1)</sup> | MAX  | UNIT |

|----------------------------|--------------------------------------------------------|------|--------------------|------|------|

| ANALOG AND DIGITAL LDOS    |                                                        |      |                    |      |      |

| VDD_ANA_IN<br>VDD_DIG_IN   | Analog and digital voltage input range (2)(3)          | 2.85 | 3.3                | 3.6  | V    |

| VDD_ANA_OUT<br>VDD_DIG_OUT | Analog and digital voltage output range <sup>(4)</sup> | 2.41 | 2.54               | 2.69 | V    |

- (1) Typical operating conditions are at 3.3V operating voltage and 25°C ambient temperature.

- (2) Maximum voltage difference between input voltage for analog VDD and digital VDD is 500 mV.

- (3) Maximum allowed input voltage supply ripple is 100mVp-p.

- (4) Set in factory at 2.5V nominal output.

## DC CHARACTERISTICS DIGITAL I/O

|                 | PARAMETER                 | CONDITION                     | MIN                  | MAX                  | UNIT     |

|-----------------|---------------------------|-------------------------------|----------------------|----------------------|----------|

| $V_{IH}$        | High-level input voltage  | VDD DIG IO = 2.85V            | 0.8 <sub>IOVCC</sub> |                      | <b>V</b> |

| $V_{IL}$        | Low-level input voltage   | VDD_DIG_IO = 2.65V            |                      | 0.2 <sub>IOVCC</sub> | <b>V</b> |

| I <sub>IH</sub> | High-level input current  | $V_{IH} = VDD_DIG_IO = 2.85V$ | -1                   | 1                    | μΑ       |

| $I_{IL}^{(1)}$  | Low-level input current   | V <sub>IL</sub> = 0           | -1                   | 1                    | μΑ       |

| $V_{OL}$        | Low-level output voltage  | $I_{OL} = 100 \mu A$          |                      | 0.2                  | ٧        |

| V <sub>OH</sub> | High-level output voltage | I <sub>OH</sub> = 100 μA      | V <sub>DD</sub> -0.2 |                      | V        |

(1) Limit for  $I_{IL}$  for the pins Reset, CE and VDD\_DIG\_PWR\_D# is  $\pm 3 uA.$

## RF PERFORMANCE CHARACTERISTICS

In the performance characteristics tables the following applies:

- 1. All tests performed based on Bluetooth Test Specification rev 0.91.

- 2. All tests at antenna port unless otherwise specified.

- 3. VDD = 3.3V unless otherwise specified.

- 4.  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$

- 5. RF system performance specifications are specified on Texas Instruments Dallas Board rev 2.0a reference design platform.

- 6. Reference Dallas Board rev 2.0a schematic for test point references.

### RECEIVER PERFORMANCE CHARACTERISTICS

|                                    | PARAMETER                                                            | CONDITION                                                                   |            | MIN | TYP <sup>(1)</sup> | MAX | UNIT |

|------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------|------------|-----|--------------------|-----|------|

|                                    |                                                                      |                                                                             | 2.402 GHz  |     | -79                | -72 | dBm  |

| RX <sub>sense</sub> <sup>(2)</sup> | Receive sensitivity                                                  | BER < 0.001                                                                 | 2.441 GHz  |     | -79                | -72 | dBm  |

|                                    |                                                                      |                                                                             | 2.480 GHz  |     | -79                | -72 | dBm  |

| PinRF                              | Maximum input level                                                  |                                                                             |            | -20 | 0                  |     | dBm  |

| C/I <sub>CCI</sub>                 | Carrier to interferer ratio in the presence of co-channel interferer | P <sub>in</sub> RF = -60 dBm, BER < 0.001                                   |            |     | 9                  | 11  | dB   |

|                                    | Carrier to interferer ratio in the                                   | $\Delta F_{ACI} = \pm 1 \text{ MHz}, P_{in}RF = -60 \text{ dBm}, B$         | ER < 0.001 |     | -3                 | 0   | dB   |

| C/I <sub>ACI</sub>                 | presence of adjacent channel                                         | $\Delta F_{ACI} = + 2 \text{ MHz}, P_{in}RF = -60 \text{ dBm}, B$           | ER < 0.001 |     | -42                | -30 | dB   |

|                                    | interferer                                                           | $\Delta F_{ACI} = + 3 \text{ MHz}, P_{in}RF = -67 \text{ dBm}, BER < 0.001$ |            |     | -46                | -40 | dB   |

| C/I <sub>IMAGE</sub>               | Carrier to interferer ratio in the presence of image interferer      | $\Delta$ F= -2 MHz, P <sub>in</sub> RF = -67 dBm, BER                       | < 0.001    |     | -20                | -9  | dB   |

| C/I <sub>IMAGE</sub> 1MHz          | Carrier to interferer ratio in the presence of image-1mHz interferer | $\Delta f = -3$ MHz, $P_{in}RF = -67$ dBm, BER                              | < 0.001    |     | -32                | -20 | dB   |

| IMP <sup>(3)</sup>                 | Intermodulation performance                                          | $F_1 = + 3 \text{ MHz}, F_2 = + 6 \text{ MHz}, P_{in}RF =$                  | -64 dBm    | -39 | -31                |     | dBm  |

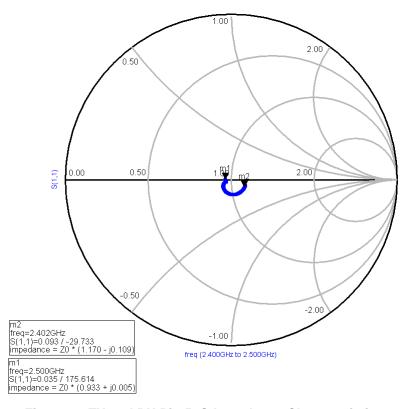

| Z <sub>RFIN</sub> <sup>(4)</sup>   | Input impedance of RF port (RF_inout)                                | Single input impedance, F <sub>in</sub> = 2.5 GHz                           |            |     | 50                 |     | Ω    |

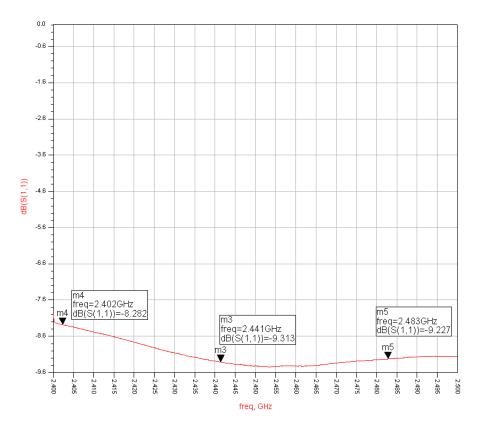

| Return Loss <sup>(5)</sup>         | Return Loss                                                          |                                                                             |            |     |                    | -8  | dB   |

|                                    |                                                                      | P <sub>in</sub> RF = -10 dBm, 30 MHz < F <sub>CWI</sub> < 2<br>BER < 0.001  | GHz,       | -10 |                    |     | dBm  |

| ООВ                                | Out Of Band Blocking                                                 | P <sub>in</sub> RF = -27 dBm, 2000 MHz < F <sub>CWI</sub> < BER < 0.001     | 2399 MHz,  | -27 |                    |     | dBm  |

|                                    | Performance                                                          | P <sub>in</sub> RF = -27 dBm, 2498 MHz < F <sub>CWI</sub> < BER < 0.001     | 3000 MHz,  | -27 |                    |     | dBm  |

|                                    |                                                                      | P <sub>in</sub> RF = -10 dBm, 3000 MHz < F <sub>CWI</sub> < BER < 0.001     | 12.75 GHz, | -10 |                    |     | dBm  |

- (1) Typical operating conditions are at 3.3V operating voltage and 25°C ambient temperature.

- (2) The receiver sensitivity is measure at the device interface.

- (3) The  $f_0 = -64$  dBm Bluetooth modulated signal,  $f_1 = -39$ dbm sine wave,  $f_2 = -39$  dBm Bluetooth modulated signal,  $f_0 = 2f_1 f_2$ , and  $|f_2 f_1| = n \times 1$ MHz, where n is 3, 4, or 5. For the typical case, n = 3.

- (4) Reference Smith chart Figure 4.

- (5) Reference chart Figure 5.

## TRANSMITTER PERFORMANCE CHARACTERISTICS

|                                    | PARAMETER             | CONDITION | MIN | TYP <sup>(1)</sup> | MAX | UNIT |

|------------------------------------|-----------------------|-----------|-----|--------------------|-----|------|

|                                    |                       | 2.402 GHz | -1  | 3                  | 7   | dBm  |

| P <sub>OUT</sub> RF <sup>(2)</sup> | Transmit output power | 2.441 GHz | -1  | 3                  | 7   | dBm  |

|                                    |                       | 2.480 GHz | -1  | 3                  |     | dBm  |

| Power Density                      | Power density         |           | -4  | 1                  | 2   | dBm  |

(1) Typical operating conditions are at 3.3V operating voltage and 25°C ambient temperature.

(2) The output power is measure at the device interface.

## TRANSMITTER PERFORMANCE CHARACTERISTICS (continued)

|                                                                        | PARAMETER                                                 | CONDITION                                                                       | MIN | TYP <sup>(1)</sup> | MAX | UNIT |

|------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------|-----|--------------------|-----|------|

| MOD ΔF1 <sub>AVG</sub>                                                 | Modulation characteristics                                | Data = 00001111                                                                 | 140 | 165                | 175 | kHz  |

| MOD ΔF2 <sub>MAX</sub> (3)                                             | Woodiation characteristics                                | Data = 10101010                                                                 | 115 | 125                |     | kHz  |

| $\Delta$ F2 <sub>AVG</sub> / $\Delta$ F1 <sub>AVG</sub> <sup>(4)</sup> | Modulation characteristics                                |                                                                                 | 0.8 |                    |     |      |

|                                                                        |                                                           | + 500 kHz                                                                       |     |                    | -20 | dBc  |

| ACP <sup>(5)</sup>                                                     | Adjacent channel power (In-band spurious)                 | M N   = 2                                                                       | -50 | -48                | -20 | dBm  |

|                                                                        |                                                           | M N   > 3                                                                       | -53 | <b>-</b> 51        | -40 | dBm  |

| P <sub>OUT</sub> 2×fo <sup>(6)</sup>                                   | PA 2 <sup>nd</sup> Harmonic Suppression                   | Maximum gain setting:<br>f <sub>0</sub> = 2402 MHz, P <sub>out</sub> = 4804 MHz |     | <b>-77</b>         |     | dB   |

| P <sub>OUT</sub> 3*fo <sup>(3)</sup>                                   | PA 3 <sup>rd</sup> Harmonic Suppression                   | Maximum gain setting:<br>f <sub>0</sub> = 2402 MHz, P <sub>out</sub> = 7206 MHz |     | -98                |     | dB   |

| Z <sub>RFOUT</sub> <sup>(7)</sup>                                      | RF Output Impedance/Input Impedance of RF Port (RF_inout) | P <sub>out</sub> at 2.5 GHz                                                     |     | 50                 |     | Ω    |

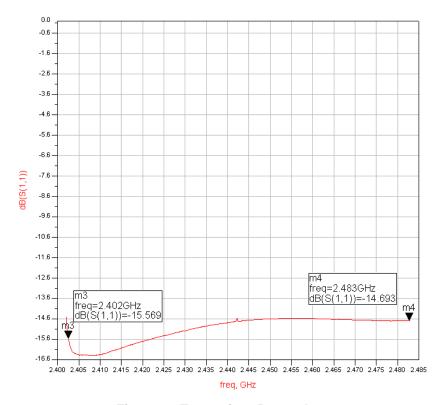

| Return Loss <sup>(8)</sup>                                             | Return Loss                                               |                                                                                 |     |                    | -14 | dB   |

- 3)  $\Delta$ F2max > 115 kHz for at least 99.9% of all  $\Delta$ f2max.

- (4) Modulation index set between 0.28 and 0.35.

- (5) Not tested in production.

- (6) Out-of-Band spurs only exist at 2<sup>nd</sup> and 3<sup>rd</sup> harmonics of the CW frequency for each channel. Performance of the radio is significantly better than BT 1.1 specification.

- (7) Reference Smith chart Figure 4.

- (8) Reference chart Figure 6.

## SYNTHESIZER PERFORMANCE CHARACTERISTICS(1)

|                       | PARAMETER                           | CONDITION               | MIN  | TYP | MAX  | UNIT     |

|-----------------------|-------------------------------------|-------------------------|------|-----|------|----------|

| f <sub>VCO</sub>      | VCO Frequency range                 |                         | 2402 |     | 2480 | MHz      |

| t <sub>LOCK</sub>     | Lock time                           | f <sub>0</sub> ± 20 kHz |      | 120 |      | μs       |

| $\Delta f_0$ offset   | Initial carrier frequency tolerance | During preamble         | -75  | 0   | 75   | kHz      |

|                       |                                     | DH1 data packet         | -25  | 0   | 25   | kHz      |

| Af aluift             | laitial corrier fragues and drift   | DH3 data packet         | -40  | 0   | 40   | kHz      |

| ∆f <sub>0</sub> drift | Initial carrier frequency drift     | DH5 data packet         | -40  | 0   | 40   | kHz      |

|                       |                                     | Drift Rate              | -20  | 0   | 20   | kHz/50µs |

| t <sub>D</sub> -Tx    | Transmitter delay time              | From Tx data to antenna |      | 4   |      | μs       |

<sup>(1)</sup> Frequency accuracy dependent on crystal or oscillator chosen. Crystal/oscillator must have cumulative accuracy specifications of not more than ±20 ppm to meet the Bluetooth specification.

## CRYSTAL/OSCILLATOR PERFORMANCE CHARACTERISTICS

|                                 | PARAMETER                       | TEST CONDITIONS                                                                        | MIN | TYP | MAX  | UNIT   |

|---------------------------------|---------------------------------|----------------------------------------------------------------------------------------|-----|-----|------|--------|

| fosc                            | Crystal oscillator frequency    |                                                                                        | 10  | 12  | 26   | MHz    |

| f <sub>ACC</sub> <sup>(1)</sup> | Frequency accuracy              | Cumulative over operating temperature range                                            | -20 |     | 20   | ppm    |

| t <sub>OSC-ON</sub>             | Oscillator turn-on time         | VCC applied, $f_{OSC}$ = 12 MHz, $c_{ext}$ = 0.1 $\mu F$ , Settled to within $f_{ACC}$ |     | 4   |      | ms     |

| Vosc                            | Oscillator input voltage        | External XO input                                                                      | 0.6 |     | 2    | Vpp    |

| ESR                             | Equivalent series resistance    |                                                                                        |     | 50  | 100  | Ω      |

| D <sub>CYCLE</sub>              | Duty cycle                      |                                                                                        | 49% |     | 51%  |        |

| Б                               | Phase noise                     | 100Hz                                                                                  |     |     | -105 | dBc/Hz |

| P <sub>NOISE</sub>              | Phase hoise                     | 1000Hz                                                                                 |     |     | -125 | dBc/Hz |

| B <sub>BCLK</sub>               | Baseband clock output frequency |                                                                                        |     | 12  |      | MHz    |

<sup>(1)</sup> Frequency accuracy dependent on crystal or oscillator chosen. Crystal/oscillator must have cumulative accuracy specifications of ±15 ppm to provide margin for frequency drift with aging and temperature.

Product Folder Links: LMX5251

## **AC CHARACTERISTICS SERIAL INTERFACE TIMING**

|                   | PARAMETER                      | CONDITION                       | MIN | TYP | MAX | UNIT |

|-------------------|--------------------------------|---------------------------------|-----|-----|-----|------|

| t <sub>CS</sub>   | Data to clock setup time       |                                 | 10  |     |     | ns   |

| t <sub>CH</sub>   | Data to clock hold time        |                                 | 5   |     |     | ns   |

| t <sub>CWH</sub>  | Clock pulse width high         |                                 | 20  |     |     | ns   |

| $t_{CWL}$         | Clock pulse width low          |                                 | 20  |     |     | ns   |

| t <sub>ES</sub>   | Clock to enable setup time     |                                 | 10  |     |     | ns   |

| t <sub>CES</sub>  | Enable to clock setup time     |                                 | 20  |     |     | ns   |

| t <sub>EWH</sub>  | Enable pulse width high        | Con Coriol Bort Timing Diagrams | 20  |     |     | ns   |

| t <sub>EWL</sub>  | Enable pulse width low         | See Serial Port Timing Diagrams | 200 |     |     | ns   |

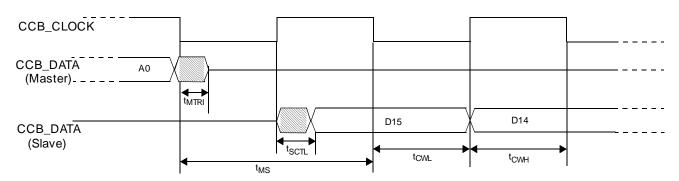

| t <sub>MS</sub>   | Master to slave transfer time  |                                 |     | 70  |     | ns   |

| t <sub>MTRI</sub> | Master to TRI-STATE setup time |                                 | -5  |     | 10  | ns   |

| t <sub>SCTL</sub> | Slave control setup time       |                                 | 0   |     | 10  | ns   |

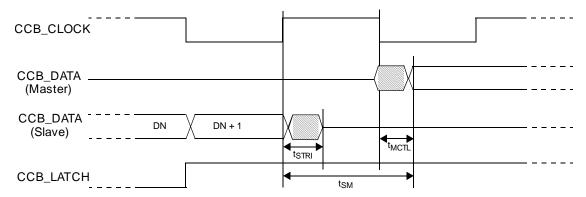

| t <sub>SM</sub>   | Slave to master return time    |                                 |     | 60  |     | ns   |

| t <sub>STRI</sub> | Slave to TRI-STATE setup time  |                                 | 0   |     | 10  | ns   |

| t <sub>MCTL</sub> | Master control setup time      |                                 | 5   |     | 10  | ns   |

# PERFORMANCE PARAMETERS (TYPICAL)

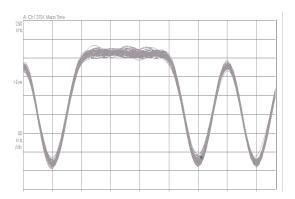

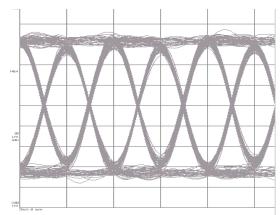

Figure 1. Modulation

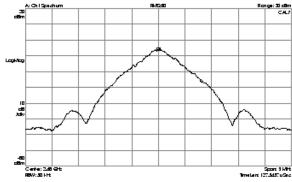

Figure 2. Transmit Spectrum

Figure 3. Corresponding Eye Diagram

Figure 4. TX and RX Pin  $50\Omega$  Impedance Characteristics

Figure 5. Receiver Return Loss

Submit Documentation Feedback

Copyright © 2004–2013, Texas Instruments Incorporated

Figure 6. Transmitter Return Loss

### **FUNCTIONAL DESCRIPTION**

The LMX5251 is a high performance, monolithic, radio transceiver optimized for Bluetooth communications systems. When used in conjunction with a Bluetooth baseband controller (e.g., LMX5100), a complete Bluetooth node with a Host Control Interface (HCI) can be implemented.

The LMX5251 radio architecture allows for minimal external components. The highly integrated design includes the low noise amplifier (LNA), mixer, on-chip filters, 2.5 GHz  $\Delta\Sigma$  PLL, voltage controlled oscillator (VCO), power amplifier (PA) driver, and modem functions. Digital modulation and demodulation techniques are utilized for a robust manufacturable design. Power management includes control over individual chip functions and internal voltage regulation for optimum performance.

The LMX5251 is optimized for low power operation, while maintaining sensitivity performance. The main external components required consist of a crystal (or other clock source) and assorted de-coupling capacitors to form a complete Class 2 Bluetooth radio transceiver. Optional components, based on the requirements of a particular application may include a band select filter, T/R switch, and a differential to single ended balun (discrete or microstrip). The T/R switch and balun are required only if one antenna is used instead of two antennas.

#### Radio Receiver

The signal path of the RX architecture contains an internal LNA and quadrature RF downconverting mixer at 2.5 GHz. A low intermediate frequency (IF) receiver provides high performance at low cost and low current consumption. The IF demodulator is implemented digitally in combination with a limiting amplifier.

## **Low Noise Amplifier**

The on-board low noise amplifier (LNA) is a single-ended structure designed with a  $50\Omega$  input impedance for simple capacitive matching. The LNA is closely integrated with the mixer providing low noise and good immunity from blocking signals.

#### **RX Mixer**

The receive mixer is an image reject ring diode type mixer. An internal low noise gain block is incorporated prior to the mixer to achieve extremely low noise performance. A differential IF output improves noise immunity while maintaining a high intercept point.

#### **Channel Select Filter**

The IF circuitry is followed by an integrated complex active bandpass filter that provides the required channel selectivity and image rejection. The I and Q outputs of the filter are then converted to the digital domain using a limiter, discriminator, and A/D converter.

#### Limiter

The limiter circuit consists of I and Q limiting amplifiers that provide the remaining gain in the receiver such that an acceptable signal level exists at the frequency modulation (FM) discriminator. Limiting amplification of the downconverted wanted signal minimizes the input range requirements of the A/D converter.

## **FM Discriminator**

The limited signal is translated to digital format using an analog frequency shift keying (FSK) demodulator and A/D converter. The A/D extracts the RX signal at a sample rate of 72.0 MHz.

## **Receive Signal Strength Indicator**

The receive signal strength indicator (RSSI) signal is derived from the input level to the limiter and covers a range low detector level = -59dBm and high detector level = -38dBm. The information is typically fed back to the baseband controller via the serial interface.

#### **Radio Transmitter**

The signal path of the TX architecture contains an internal modulator for 1 Mb/s GFSK (Gaussian Frequency Shift Keying) modulation of the 2.5 GHz VCO. Closed loop  $\Delta\Sigma$  modulation is chosen, since it is the most low power solution. The integrated pre-amplifier provides output levels sufficient for Class 2 Bluetooth operation.

#### **Modulator**

The encrypted, whitened, transmit data stream is supplied by the baseband controller to the LMX5251 via the TX\_RX\_DATA pin (pin 33). An internal digital Gaussian filter provides the FSK modulation waveform. A modulation input to the completely integrated 2.5 GHz  $\Delta\Sigma$  PLL provides a consistent modulation deviation. This eliminates the risks of open loop modulation such as frequency drift and frequency offset.

### **Transmit Frequency Output**

The transmit RF output is differential, and typically connected to the antenna through a passive balun.

## **Frequency Synthesizers**

The 2.4 to 2.5 GHz RF range is provided by an on-chip voltage controlled oscillator (VCO). A programmable 2.5 GHz  $\Delta\Sigma$  PLL selects the channel frequency. An internal crystal oscillator can be configured with a 10 to 26 MHz crystal, or for TCXO frequency input. Internal dividers provide internal clocks and clock outputs to the baseband controller.

## **Voltage Controlled Oscillator**

The transmit VCO is configured differentially, with an internal tank circuit, and tuning varactor. The input modulated signal is supplied from the internal  $\Delta\Sigma$  PLL.

Product Folder Links : LMX5251

### **Crystal Circuit**

Due to the need for clock accuracy, the LMX5251 has a dedicated crystal oscillator. The LMX5251 uses the crystal to supply a 12 MHz clock source to the baseband controller. The 12 MHz is buffered, providing a receive data clock to the baseband controller. It is also possible to configure the crystal oscillator for input only when another high quality crystal oscillator is available in the system. The LMX5251 can accommodate crystals from 10 to 26 MHz in increments of 10 kHz.

## **External Crystal Oscillators**

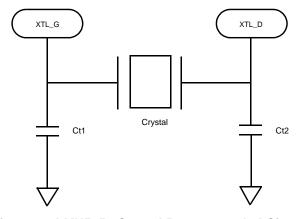

The LMX5251 each contain a crystal driver circuit. This circuit operates with an external crystal and capacitors to form an oscillator. (See Figure 7 and Figure 23). The LMX5251 also can operate with an external TCXO (Temperature Compensated Crystal Oscillator).

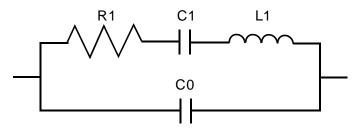

#### Crystal

The crystal appears inductive near its resonant frequency. It forms a resonant circuit with its load capacitors. The resonant frequency may be trimmed with the crystal load capacitance.

#### 1. Load Capacitance

For resonance at the correct frequency, the crystal should be loaded with its specified load capacitance, which is the value of capacitance used in conjunction with the crystal unit. Load capacitance is a parameter specified by the crystal, typically expressed in pF. The crystal circuit shown in Figure 8 is composed of:

- C1 (motional capacitance)

- R1 (motional resistance)

- L1 (motional inductance)

- C0 (static or shunt capacitance)

The LMX5251 provide some of the load with internal capacitors  $C_{int}$ . The remainder must come from the external capacitors labeled Ct1 and Ct2 as shown in Figure 7. Ct1 and Ct2 should have the same the value for best noise performance. Crystal load capacitance ( $C_{I}$ ) is calculated as the following:

$$C_1 = C_{int} + Ct1//Ct2$$

The  $C_L$  above does not include the crystal internal selfcapacitance C0 as shown in Figure 8, so the total capacitance is:

$$C_{total} = C_L + C0$$

Figure 7. LMX5251 Crystal Recommended Circuit

Figure 8. Crystal Equivalent Circuit

## 2. Crystal Pullability

Pullability is another important parameter for a crystal, which is the change in frequency of a crystal with units of ppm/pF, either from the natural resonant frequency to a load resonant frequency, or from one load resonant frequency to another. The frequency can be pulled in a parallel resonant circuit by changing the value of load capacitance. A decrease in load capacitance causes an increase in frequency, and an increase in load capacitance causes a decrease in frequency.

## 3. Frequency Tuning

Frequency Tuning is achieved by adjusting the crystal load capacitance with external capacitors. It is a Bluetooth requirement that the frequency is always within ±20 ppm. Crystal/oscillator must have cumulative accuracy specifications of ±15 ppm to provide margin for frequency drift with ageing and temperature.

#### 4. Vite Crystal

The VXE4-1055 is a 12 MHz SMT crystal from Vite. Texas Instruments is using this crystal with the LMX5251. Table 1 shows the specification of VXE4-1055.

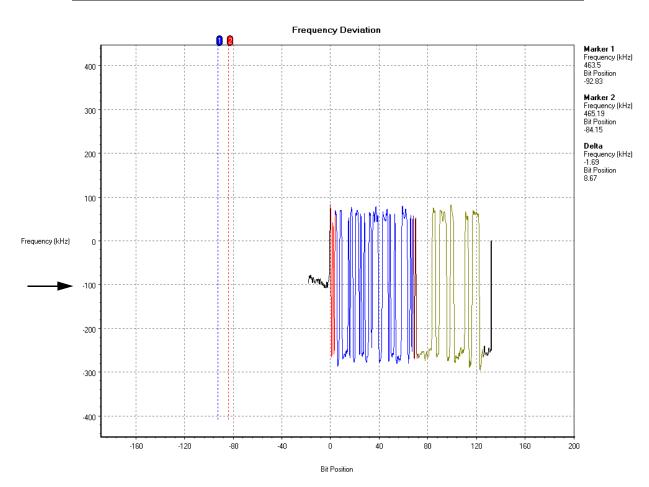

Since the internal capacitance of the crystal circuit is 4-5 pF and the load capacitance is 9 pF, 10 pF is a good starting point for both Ct1 and Ct2. The 2480 MHz RF frequency offset is then tested. Figure 9 shows the RF frequency offset test results.

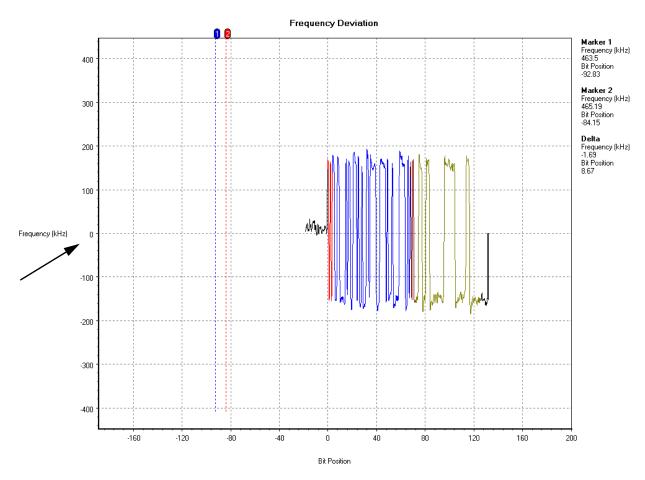

Figure 9 shows the results are 100 kHz off the center frequency, which is –4 ppm. The pullability of the crystal is 24 ppm/pF, so the load capacitance must be decreased by about 0.2 pF. By changing Ct1 or Ct2 to 9 pF, the total load capacitance is increased by 0.26 pF. Figure 10 shows the frequency offset test results. The frequency offset is now zero with Ct1 = 9 pF, Ct2 = 10 pF.

## 5. Kineski KSS CX-4025S

The LMX5251 has also been tested with the Kineski KSS CX-4025S. See Table 2.

Table 1. VXE4-1055-12M000

| SPECIFICATION       | VALUE                                                 |

|---------------------|-------------------------------------------------------|

| Package             | 6.0x3.5x1.1 mm 4 pads                                 |

| Frequency           | 12.000 MHz                                            |

| Mode                | Fundamental                                           |

| Stability           | ±18 ppm at -20 to +70°C (inclusive of all conditions) |

| Load Capacitance    | 9 pF                                                  |

| ESR                 | 40 Ω max, 20 Ω typ                                    |

| Shunt Capacitance   | 7 pF max                                              |

| Drive Level         | 10 to 100 μW                                          |

| Pullability         | 24 ppm/pF min                                         |

| Storage Temperature | -40 to +85°C                                          |

## **Table 2. KSS CX-4025S**

| SPECIFICATION       | VALUE                                                 |

|---------------------|-------------------------------------------------------|

| Package             | 4.0x2.5x0.75 mm 4 pads                                |

| Frequency           | 12.000 MHz                                            |

| Mode                | Fundamental                                           |

| Stability           | ±20 ppm at −30 to +80°C (inclusive of all conditions) |

| Load Capacitance    | 12pF                                                  |

| ESR                 | 80 $\Omega$ max, 20 $\Omega$ typ                      |

| Shunt Capacitance   | 3 pF max                                              |

| Drive Level         | 100 μW max                                            |

| Storage Temperature | -40 to +85°C                                          |

Figure 9. Frequency Offset with 10 pF Capacitors

Figure 10. Frequency Offset with 9 pF//10 pF Capacitors

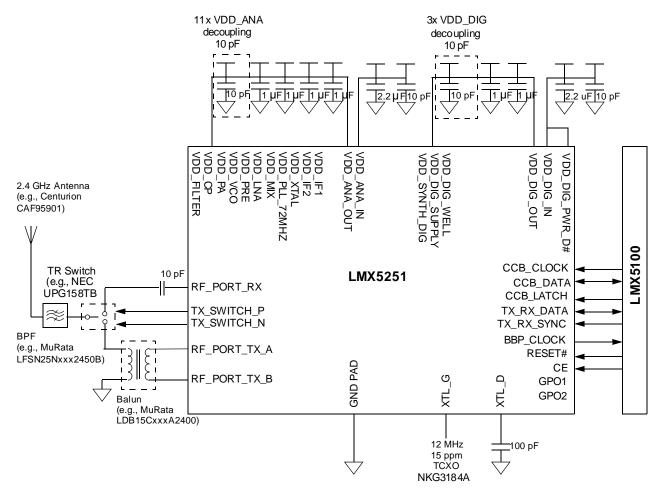

## **TCXO (Temperature Compensated Crystal Oscillator)**

The LMX5251 also can operate with an external TCXO (Temperature Compensated Crystal Oscillator). The TCXO signal is directly connected to the XTL\_G, shown in Figure 24.

- 1. Input Impedance

- The LMX5251 XTL G pin has in input impedance of 2pF capacitance in parallel with >400k $\Omega$  resistance.

- 2. NKG3184A TCXO

The LMX5251 has also been tested with the NKG3184A TCXO. See Table 3.

Table 3. TCXO NKG3184A

| SPECIFICATION       | VALUE                                                 |

|---------------------|-------------------------------------------------------|

| Package             | 5.0x3.2x1.4 mm 4 pads                                 |

| Frequency           | 12.000 MHz                                            |

| Stability           | ±18 ppm at -30 to +85°C (inclusive of all conditions) |

| Output Load         | 10kΩ // 13pF                                          |

| Current Consumption | 2.0mA                                                 |

| Output Level        | 0.3Vp-p to 2.0Vp-p                                    |

| Storage Temperature | -40 to +85°C                                          |

| DC Cut Capacitor    | Included in VC-TCXO                                   |

Submit Documentation Feedback

Copyright © 2004–2013, Texas Instruments Incorporated

## **Multiple Crystal Support**

The LMX5251 Bluetooth Radio IC can operate using a large range of crystal frequencies. The on-chip  $\Delta\Sigma$  PLL can accommodate crystal frequencies or clock sources from 10 to 26 MHz. In addition, the LMX5251 can generate a 12 MHz Baseband Controller Clock (BBP\_CLOCK) using its on-board  $\Delta\Sigma$  PLL. For baseband controllers requiring a frequency clock other than 12 MHz, the BBP\_CLOCK can be switched to generate a digital signal at the crystal frequency.

### **Theory of Operation**

For 10 to 20 MHz crystals, the LMX5251 doubles the crystal frequency for use on the chip. It generates an internal 12 MHz clock with 24-bit accuracy for its internal processing using one PLL. In addition, it must generate an RF signal for transmit and receive using another PLL with 24-bit accuracy. For 20 to 26 MHz crystals, the LMX5251 does not double the crystal frequency, but still generates the 12 MHz internal clock and RF signal with 24-bit accuracy. The baseband controller must supply the LMX5251 with two correct 24-bit codes so the LMX5251 will generate the 12 MHz internal clock as well as the RF signal correctly:

- Clock\_Code\_12MHz\_PLL = 72 x (10<sup>6</sup>) x (2<sup>16</sup>) / crystal

- Clock Code RF PLL = (2<sup>16</sup>) x crystal / (10<sup>6</sup>)

#### **Serial Interface**

The serial interface for the LMX5251 is a 3-wire data clock latch in slave configuration. The interface can also support bidirectional data transfer mode. An option to provide fast write-only programmability is also included. The serial interface is used to program all of the various control registers and state machines in the LMX5251. The read back mode is enabled through a control bit provided by the baseband controller.

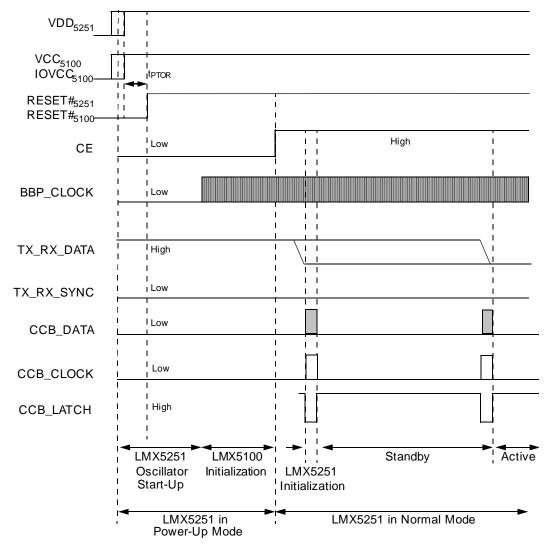

#### **Power Control**

The power control information for the LMX5251 is stored in dedicated power control registers, which configure the state for the various circuit blocks as long as VDD\_ANA\_IN is applied. In addition, a hardwire control pin, CE, is available for enabling the entire chip for RX, TX, and Standby modes. While RESET# is low, the LMX5251 registers are reset to the default values. In normal mode, the LMX5251 powers up according to the state of the mode and power control register bits. The default condition powers down all circuit blocks except for the crystal oscillator, crystal oscillator voltage regulator, and baseband controller interface. The RX or TX mode configuration is then programmed via the serial interface.

## **Voltage Reulation**

Voltage is regulated using two 100 mA linear voltage regulators producing the following voltages:

- Input Range: 2.85V to 3.6V

- Output: 2.5V

The LMX5251 crystal oscillator is forced on by the use of the TX\_RX\_DATA pin. When RESET# is brought high, the TX\_RX\_DATA pin is also held high by the baseband controller. This allows for a baseband controller bootup sequence. The default state of the crystal oscillator will start up and provide an output to the BBP\_CLOCK pin once the level has surpassed a minimum threshold. Once the baseband controller is stable, the TX\_RX\_DATA pin reverts to normal operation.

#### **Internal Pull-Ups/Downs**

LMX5251 has four pads that have either pull-ups or pull downs. Reference Table 4 for details.

#### Table 4. Internal Pull-Ups/Downs

| NAME             | DIRECTION | DESCRIPTION                                                                                                                                                        |

|------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CE               | Pull-up   | Upon power-up, the LMX5251 generates a 12 MHz baseband clock in default configuration.                                                                             |

| RESET#           | Pull-up   | Upon power-up, RESET# is low, and the LMX5251 registers are reset to the default values. When RESET# transitions low to high, the LMX5251 starts normal operation. |

| VDD_DIG_PWR_DWN# | Pull-up   | Upon power-up, held high to enable digital LDO regulator.                                                                                                          |

| BBP_CLOCK        | Pull-down | Upon power-up, a 12 MHz clock is provided by the LMX5251 to the baseband controller. In low power modes, the BBP_CLOCK output of the LMX5251 can be disabled.      |

Product Folder Links :LMX5251

#### APPLICATION INFORMATION

## **Typical Application Block Diagrams**

Figure 11. System Application Diagram

## LMX5100/LMX5251 Interface

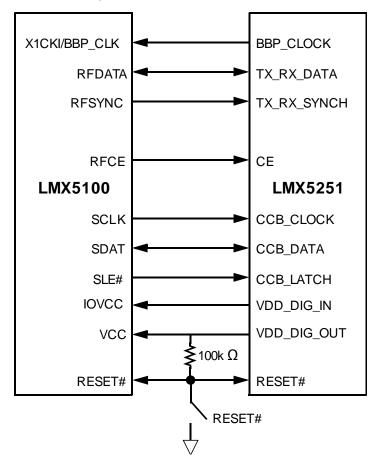

This section describes the interface signals between the LMX5251 and the LMX5100. The LMX5251 interfaces to the LMX5100 via an 8-pin interface, called the RF interface. Figure 12shows how the LMX5100 interfaces to the LMX5251 Bluetooth CMOS Radio chip.

Figure 12. LMX5100/LMX5251 Interface

#### **RF Interface**

The LMX5251 and the LMX5100 communicate with each other via an 8-pin digital interface. The RF interface signals can be grouped as:

- Modem Signals (BBP\_CLOCK, TX\_RX\_DATA, and TX\_RX\_SYNC)

- Chip Enable Control Signal (CE)

- Serial Interface Signals (CCB CLOCK, CCB DATA and CCB LATCH)

**BBP\_CLOCK (Pin 34):** The BBP\_CLOCK pin is the output pin for the 12 MHz clock signal to the LMX5100. This 12 MHz clock is provided by the LMX5251 and is used by the LMX5100 as the fast system clock (main clock) as well as the sampling clock (12 times over sampling) for the Bluetooth data, transferred via the TX\_RX\_DATA pin. During Bluetooth power-down phases, the clock output of the LMX5251 can be disabled by driving the CE pin of the RF interface with a logic low level. However, the RF interface is only allowed to control the clock while the power management module of the LMX5100 has granted "Hardware Clock Control" to the Bluetooth LLC.

**TX\_RX\_DATA (Pin 33):** The TX\_RX\_DATA pin is the multiplexed Bluetooth data receive and transmit pin. The data is provided at a bit rate of 1 Mbit/s and 12 times over sampled corresponding to the 12 MHz BBP\_CLOCK. The TX\_RX\_DATA pin is a dedicated RF interface pin. This pin is driven to a logic high level after reset.

**TX\_RX\_SYNC** (Pin 32): In receive mode (data direction from LMX5251 to LMX5100), this pin acts as the frequency correction/DC compensation circuit control output to the LMX5251. The TX\_RX\_SYNC pin is driven low throughout the correlation phase, and brought high when synchronization to the received access code is achieved.

In transmit mode (data direction from LMX5100 to LMX5251) this pin is used to enable the RF output of the LMX5251. When the TX\_RX\_SYNC pin is driven high, the RF transmitter circuit of the LMX5251 is enabled, corresponding to the settings of the power control register in the LMX5251.

**CE (Pin 31):** The CE pin is the chip enable input from the LMX5100 to LMX5251. When the CE pin is driven high, the LMX5251 is powered-up according to the settings of its power control registers. When the CE pin is low, the LMX5251 is powered-down. However, the serial interface is still operational and the LMX5100 can still access the LMX5251 internal control registers.

**CCB\_CLOCK (Pin 30):** The CCB\_CLOCK pin is the serial interface shift clock output. The LMX5100 always acts as the master of the serial interface and therefore always provides the shift clock to the LMX5251.

CCB\_DATA (Pin 29): The CCB\_DATA pin is the multiplexed serial data receive and transmit path from/to the LMX5100.

CCB\_LATCH(Pin 28): The CCB\_LATCH pin is the serial load enable input of the serial interface of the LMX5251.

During write operations (write to LMX5251 registers), the data received by the shift register of the LMX5251 is latched into the address register on the next rising edge of CCB\_CLOCK after the CCB\_LATCH signal is driven high.

During read operations (read from LMX5251 registers), the LMX5251 releases the CCB\_DATA line on the next rising edge of CCB\_CLOCK after the CCB\_LATCH signal is driven high.

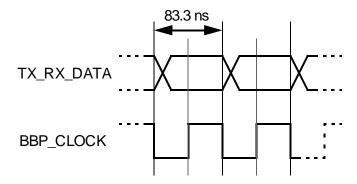

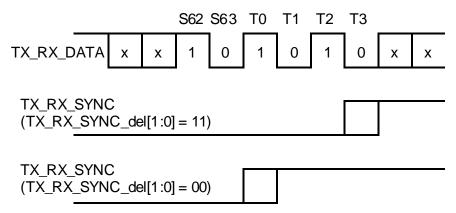

### **Receive and Transmit Data Timing**

All timing for receive and transmit data exchange is derived from the 12 MHz BBP\_CLOCK (pin 34) output of the LMX5251. The LMX5251 always uses the negative edge, and the baseband controller always uses the positive edge of the BBP\_CLOCK signal. For receive mode, the LMX5251 controls the TX\_RX\_DATA bus, and asserts the data from the incoming Bluetooth RF packet onto the TX\_RX\_DATA pin (pin 33) at the falling edge of the BBP\_CLOCK. The baseband controller samples the TX\_RX\_DATA at the rising edge of BBP\_CLOCK to allow for bus transition time and clock skew. The timing diagram for TX\_RX\_DATA is shown in Figure 13 and Figure 14.

LMX5251 asserts TX\_RX\_DATA; Baseband Controller samples TX\_RX\_DATA.

Figure 13. Bluetooth Receive Data Timing

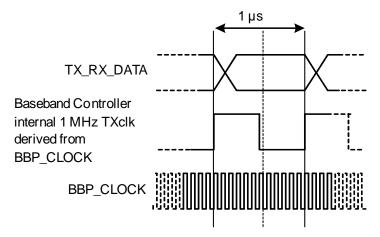

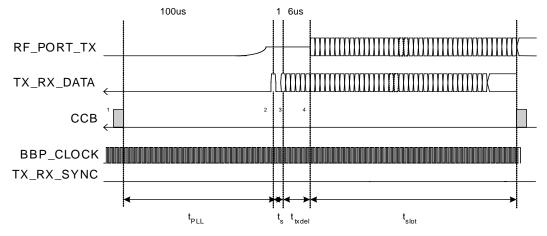

During transmit mode, the baseband controller controls the TX\_RX\_DATA line, and asserts the data from the outgoing Bluetooth RF packet onto TX\_RX\_DATA at the rising edge of the BBP\_CLOCK. The LMX5251 samples the RX\_DATA at the falling edge of BBP\_CLOCK after a six BBP\_CLOCK period delay, corresponding to a half symbol time delay to allow for sampling at the middle of the data bit.

Baseband Controller asserts TX\_RX\_DATA; LMX5251 samples TX\_RX\_DATA

Figure 14. Bluetooth Transmit Data Timing

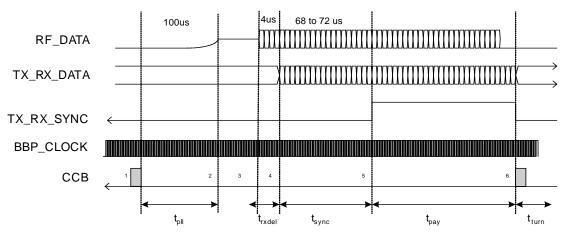

### **Receive Mode Slot Timing**

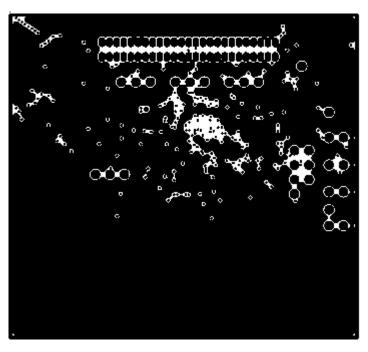

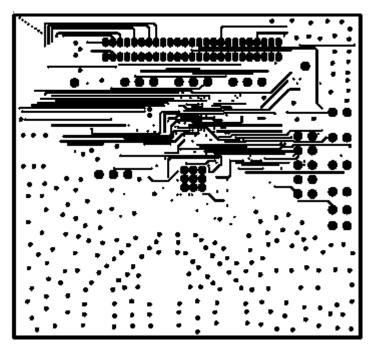

Prior to initiating the receive mode, the crystal oscillator must be turned on and settled such that the BBP\_CLOCK output is present. The baseband controller programs the LMX5251 receiver (RX) mode and frequency information via the serial interface, at which point the LMX5251 PLL begins acquiring the correct RX frequency channel. After  $\sim$ 100  $\mu$ s, the receive chain powers up. RX data is then clocked to the baseband controller. The serial port is used to program the LMX5251 out of receive mode.