# AK130/131

# TCM Integrated Transceiver

### Features

- Completely integrated baseband transceiver for 2-wire twisted pair applications

- 2B+1D+1M channels of PCM-BUS framed data, using time compression multiplexing

- Data rate: 160kbps (2B+1D+1M)

- □ Loop coverage, AK130: 1 km (3300 feet) / AK131: 2 km (6500 feet)

- Pin compatible between AK130 and AK131

- Low amplitude pulse-shaped Alternate Mark Inversion (AMI) coding for reduced spectral radiation

- Differential receiver architecture for highly reliable data recovery

- $\square$  Bit error rate less than 10<sup>-7</sup>

- PCM and Microprocessor ports that are pin selectable for single or combined port operation

- Operates on a single +5 V power supply and draws only 75 mW active power (typ)

- □ Package: 24 pin SOP

Block Diagram 니마 XTAL0 AMI Line Driver MS 0 LOH MS1 Pulse AMI Input Framer F0o Shaping Coder LOL E2o Timing and **E4**0 Control FSYNC1 LIH Data Output AMI FSYNC2 Decoder Recovery Frame ᇿ USTO B1 and B2 DSTi Channel Data DSTo D and M Channel Data Port AD(3-0) RD WR CS

Fig-1 Block Diagram

|            |       |     |    |   | _ |   |   | _   |   |   |   |   |   |   |  |

|------------|-------|-----|----|---|---|---|---|-----|---|---|---|---|---|---|--|

| <b>^</b> - | -     |     | A  | D |   | - |   | -   | : | n |   | : | - | - |  |

| u e        | - N ( | e r | aı |   | 9 | S | C | r – | I | P | τ |   | 0 | n |  |

|            |       |     |    |   |   |   |   |     |   |   |   |   |   |   |  |

The AK130/131 is a fully integrated transceiver for high-speed data transmission over unshielded twisted-pair subscriber loops. The device transmits at 160 kbps (line rate 512 kbps) over a single twisted pair wire, using a Time Compression Multiplex (TCM) transmission scheme.

The AK130/131 provides transparent, burst mode transmission of 2B+1D+1M channels in subscriber loop applications, typically KTS or PBX systems. It operates up to 1 km (AK130) / 2 km (AK131) on 0.5 mm (24 AWG) LOCAP station cable. The AK130/131 is designed for use in Slave-only, Terminal Equipment (TE) and is suited for use with most industry standard codecs. It uses a 2048 kbps synchronous serial PCM-BUS.

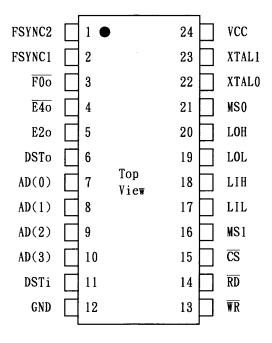

#### Pin assignment

#### Ordering information

| AK130-VS | 0 ∼ 70 °C | 24 pin SOP |

|----------|-----------|------------|

| AK131-VS | 0 ~ 70 ℃  | 24 pin SOP |

# Pin / Function

| Pin # | Symbol    | I/0 | Function                                                      |

|-------|-----------|-----|---------------------------------------------------------------|

| 1     | FSYNC2    | 0   | With F1-type sync (MS0=1), these pins go low to indicate      |

|       |           |     | that the associated B channel is active on the PCM-BUS.       |

|       |           |     |                                                               |

| 2     | FSYNC1    | 0   | With FS-type sync (MSO=0), a 244 ns-wide positive pulse is    |

| _     |           |     | output on these pins, 488 ns before start of the associated   |

|       |           | -   | B channel.                                                    |

|       |           |     |                                                               |

|       |           |     | With HFS-type sync (MS0=E2o), a 244 ns-wide positive pulse    |

|       |           |     | is output on these pins, 244 ns before start of the           |

|       |           |     | associated B channel.                                         |

| 3     | F0o       | 0   | An 8 kHz, 244-ns wide active low pulse output, indicating     |

|       | 100       |     | the start of the device's active channel times.               |

| 4     | E4o       | 0   | A 4.096MHz output clock derived from the crystal oscillator.  |

| 5     | E20       | 0   | A 2.048MHz output clock derived from the crystal oscillator.  |

| 6     | DSTo      | 0   | A 2.048 Mbps serial PCM-BUS output. In single port mode,      |

|       | 0010      |     | this bus contains the B, D, and M channel data received from  |

|       |           |     | the line input. In the combined port mode only the B          |

|       |           |     | channel data is carried on the PCM-BUS.                       |

| 7     | AD(0)     | I/0 | Bidirectional microprocessor data bus. These lines are        |

| 8     | AD(1)     | I/0 | inactive in the single port mode. In the combined port mode   |

| 9     | AD(2)     | I/0 | they carry D and M channel data.                              |

| 10    | AD(3)     | I/0 |                                                               |

| 10    | DSTi      | I   | Input line for the 2.048 Mbps serial PCM-BUS. In single       |

|       | 2011      |     | port mode, this bus contains the B, D, and M channel data to  |

|       |           |     | be transmitted on the line. In the combined port mode only    |

|       |           |     | the B channel data is carried on the PCM-BUS.                 |

| 12    | GND       | -   | Ground.                                                       |

| 13    | WR        | Ι   | Active low input to enable microprocessor port write.         |

| 14    | RD        | Ι   | Active low input to enable microprocessor port read.          |

| 15    | <u>CS</u> | Ι   | Active low chip select signal to enable microprocessor port.  |

| 16    | MS1       | I   | A high on this pin selects the single port mode. In single    |

| -     |           |     | port mode, D, M, and B channel data are carried on the        |

|       |           |     | PCM-BUS. A low in this pin selects the combined port mode.    |

|       |           |     | In this mode D and M channel data are carried by the          |

|       |           |     | microprocessor port, and B channel data is carried by the     |

|       |           |     | PCM port.                                                     |

| 17    | LIL       | Ι   | Differential Receive Inputs. These inputs are insensitive     |

| 18    | LIH       | I   | to the polarity of the receive signal.                        |

| 19    | LOL       | 0   | Differential Driver Outputs. Idle level at these outputs is   |

| 20    | LOH       | 0   | VCC/2. A positive mark results in a voltage of $VCC/2 + 1.25$ |

|       |           | -   | V at LOH and VCC/2 - 1.25 V at LOL.                           |

| 21    | MSO       | Ι   | Frame Sync Select Signal. When MS0=1, AK130/131 produces      |

|       |           | -   | F1-type frame sync signals on FSYNC1 and FSYNC2. When         |

|       |           |     | MS0=0, $AK130/131$ produces FS-type frame sync signals. When  |

|       |           |     | MSO is connected to the E20 pin, AK130/131 produces HFS-type  |

|       |           |     | frame sync signals.                                           |

|       |           |     |                                                               |

## [AK130/131]

# ASAHI KASEI

| Pin # | Symbol | I/0 | Function                                                                                                                                                                                   |

|-------|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22    | XTAL0  | Ι   | Crystal oscillator or external clock input (8.192 MHz). If<br>an external TTL clock is used, it must be coupled through a<br>$0.1\mu$ F capacitor. An external CMOS clock may be connected |

| 23    | XTAL1  | 0   | directly.<br>Crystal oscillator output. This pin is not connected if an<br>external clock is used.                                                                                         |

| 24    | VCC    |     | +5 VDC power supply input.                                                                                                                                                                 |

# Absolute Maximum Ratings

| Parameter                 | Symbol           | min       | max            | units |

|---------------------------|------------------|-----------|----------------|-------|

| Supply Voltage            | Vcc              | -0.3      | 7.0            | V     |

| Voltage on any I/O pin    | V <sub>I/0</sub> | GND - 0.3 | $V_{cc} + 0.3$ | V     |

| Current on any I/O pin    | I1/0             | -50       | 50             | mA    |

| Package power dissipation | PD               |           | 600            | mW    |

| Storage Temperature       | Tstg             | -65       | 150            | °C    |

Warning:Exceeding absolute maximum ratings may cause permanent damage.<br/>Normal operation is not guaranteed at these extremes.

|  | Operat | ing Co | onditions |  |

|--|--------|--------|-----------|--|

|--|--------|--------|-----------|--|

Voltages are with respect to ground (GND) unless otherwise stated.

Typical figures are at 25 °C and are for design aid only, not guaranteed and not subject to production testing.

| Parameter             | Symbol | min  | typ | max  | unit | Condition |

|-----------------------|--------|------|-----|------|------|-----------|

| Supply Voltage        | Vcc    | 4.75 | 5   | 5.25 | V    |           |

| Operating Temperature | Тор    | 0    |     | 70   | °C   |           |

#### ASAHI KASEI

DC Electrical Characteristics – Clocked operation over recommended temperature and power supply ranges.

| Parameter                                       | Symbol          | min | typ | max  | unit | Condition               |

|-------------------------------------------------|-----------------|-----|-----|------|------|-------------------------|

| <pre>Supply current(Transmitting a space)</pre> | Icc             | -   | -   | 11.5 | mA   | 15pF load               |

| Supply current(Transmitting a mark)             | Icc             | -   | -   | 15   | mA   | 15pF load               |

| Input high voltage                              | VIH             | 2.0 | -   |      | V    | Note-2                  |

| Input low voltage                               | V <sub>IL</sub> | -   | -   | 0.8  | V    | Note-2                  |

| Output high voltage                             | Vон             | 2.4 | -   | -    | V    | Iон=40 µ А              |

| Output low voltage                              | Vol             | -   | -   | 0.4  | V    | I <sub>0L</sub> =1.6mA  |

| Output high voltage                             | Vон             | 4.6 | -   | -    | V    | I <sub>он</sub> =10 µ А |

| Output low voltage                              | Vol             | -   | -   | 0.4  | V    | $I_{OL}$ = 10 $\mu$ A   |

| Output high current                             | Іон             | -   | -   | 40   | μA   | $V_{OH} = 2.4V$         |

| Output low current                              | Iol             | -   | -   | 1.6  | mA   | $V_{0L} = 0.4V$         |

| Input leakage current (Note-1)                  | ILL             | -   | ±1  | ±10  | μA   | Note-3                  |

Note-1: And output buffer leakage, when tristated. Note-2: Digital input Note-3: Input between VCC and GND

AC Electrical Characteristics – Clock timing (Note-1); Crystal or Digital Clock Input

| Parameter           | Symbol | min | typ   | max   | unit | Condition |

|---------------------|--------|-----|-------|-------|------|-----------|

| Operating frequency | fc     | -   | 8.192 | -     | MHz  |           |

| Frequency tolerance | Tc     | -   | -     | ±1000 | ppm  |           |

| Clock duty cycle    |        | 40  | 50    | 60    | %    |           |

Note-1: TTL clock signals on XTAL0 must be coupled through a 0.1  $\mu$  F capacitor.

### Analog Characteristics

| Parameter                            | Symbol          | min  | typ | max  | unit | Condition |

|--------------------------------------|-----------------|------|-----|------|------|-----------|

| Transmit differential amplitude      | VAO             | 2.2  | 2.5 | 2.8  | Vp   | RL=800Ω   |

| Transmit common mode offset          | XCMR            | 0    | -   | ± 75 | mV   | Note-1    |

| Transmit pulse output rise/fall time | TDRF            | -    | -   | 400  | ns   |           |

| Receive differential input amplitude | V <sub>AI</sub> | 0.35 | -   | 1.5  | V    |           |

Note-1: Relative to VCC/2

<0081-E-01>

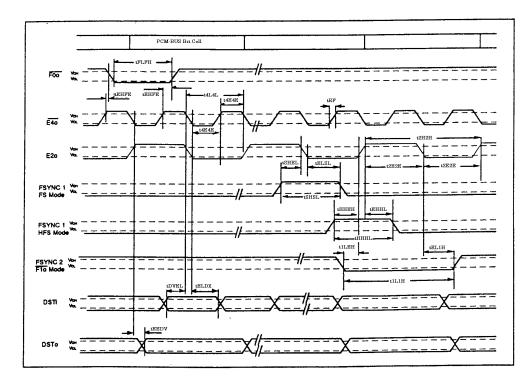

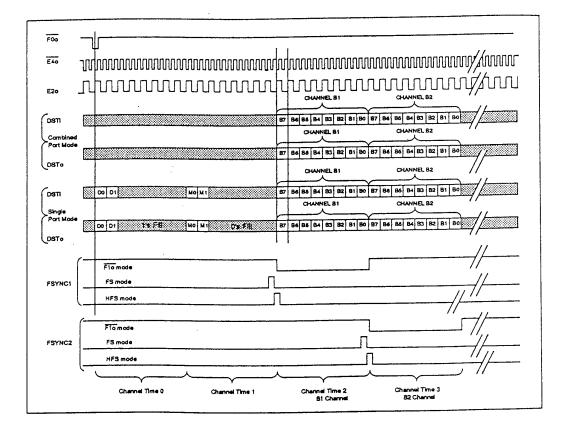

## AC Electrical Characteristics: PCM-BUS Timing (See Fig-2)

Timing figures are over recommended temperature and power supply voltages.

| Parameter                            | Symbol | min | typ  | max | unit | Condition |

|--------------------------------------|--------|-----|------|-----|------|-----------|

| FOo output pulse width               | tFLFH  | -   | 244  | -   | ns   | 15pF Load |

| E4o to F0o delay                     | tEHFE  | -20 |      | 20  | ns   | 15pF Load |

| E4o output clock period              | t4L4L  | -   | 244  | -   | ns   | 15pF Load |

| E4o pulse width high or low          | t4E4E  | -   | 122  | -   | ns   | 15pF Load |

| E2o output clock period              | t2H2H  | -   | 488  | -   | ns   | 15pF Load |

| E2o pulse width high or low          | t2E2E  | -   | 244  | ~   | ns   | 15pF Load |

| FSYNC, FOo, E4o, E2o transition time | tRF    | -   | -    | 11  | ns   | 15pF Load |

| FS pulse to E2o clock transition     | tSHEL  | 50  | -    | -   | ns   | 15pF Load |

| E20 fall to FS pulse fall            | tELSL  | 100 | -    | -   | ns   | 15pF Load |

| FS mode pulse width                  | tSHSL  | -   | 244  | -   | ns   | 15pF Load |

| HFS pulse to E2o clock transition    | tHHEH  | 50  | -    | -   | ns   | 15pF Load |

| E20 rise to HFS pulse fall           | tEHHL  | 100 | -    | -   | ns   | 15pF Load |

| HFS mode pulse width                 | tHHHL  | -   | 244  | -   | ns   | 15pF Load |

| Flo pulse to E2o clock transition    | t1LEH  | 50  | -    | -   | ns   | 15pF Load |

| E2o fall to F1o pulse rise           | tEL1H  | 100 | -    | -   | ns   | 15pF Load |

| Flo mode pulse width                 | t1L1H  | -   | 3906 | -   | ns   | 15pF Load |

| Serial input setup time              | tDVEL  | 30  | -    | -   | ns   |           |

| Serial input hold time               | tELDX  | 50  | -    | -   | ns   |           |

| Serial output delay                  | tEEDV  | -   | -    | 125 | ns   | 15pF Load |

Fig-2 PCM-BUS Timing

### ASAHI KASEI

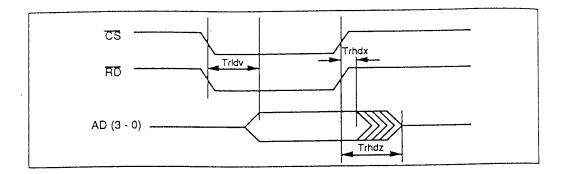

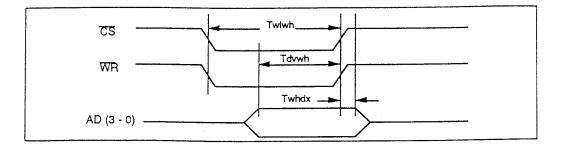

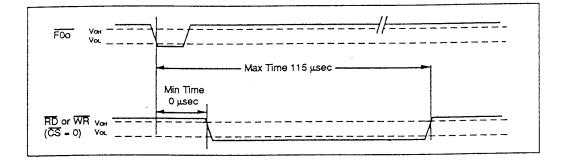

# AC Electrical Characteristics: Microprocessor Port Timing (See Fig-3 and Fig-4)

Timing figures are over recommended temperature and power supply voltages.

| Parameter                              | Symbol | Min | Max | Unit | Condition |

|----------------------------------------|--------|-----|-----|------|-----------|

| Data hold after Read or Chip Select    | Trhdx  | 0   | -   | ns   | 15pF Load |

| Data float after Read or Chip Select   | Trhdz  | -   | 90  | ns   | 15pF Load |

| Read or Chip Select to valid data      | Trldv  | -   | 90  | ns   | 15pF Load |

| Data setup before Write or Chip Select | Tdvwh  | 40  | -   | ns   | 15pF Load |

| Data hold after Write or Chip Select   | Twhdx  | 15  | -   | ns   | 15pF Load |

| Minimum pulse width CS and WR          | Twlwh  | 80  | -   | ns   | 15pF Load |

Fig-3 Microprocessor Port Read Cycle Timing

Fig-4 Microprocessor Port Write Cycle Timing

The AK130/131 is a high-speed 2-wire TCM transceiver for PBX and KTS systems. It provides 160 kbps for transparent transmission of 2B+D+M channels. It is clocked to produce self-contained AMI pulses at a line rate of 512 kbps. Designed for Terminal Equipment (TE) (Slave only), the AK130/131 allows effective full-duplex transmission of high-speed digital data over existing twisted-pair installations. The AK130/131 can operate over most customer premises wiring, ranging from 19 to 26 AWG. In typical systems (24 AWG), the AK130 is effective in subscriber loops of up to 1 km (3300 feet), and the AK131 is effective in subscriber loops of up to 2 km (6500 feet).

The transmitter incorporates an 800  $\Omega$  fully differential line driver that, when coupled through two 200  $\Omega$  series termination resistors and a 2:1 step-down transformer, produces a peak line signal of 625 mV on a 100  $\Omega$  line from a single +5 V power supply. It uses AMI line coding for minimum spectral radiation and reduce RFI.

The receiver uses a fully differential architecture to reduce the effect of impulsive noise. The adaptive data slicers and peak detectors (AK130), or the adaptive equalizer (AK131), ensure optimum signal-to-noise ratio regardless of received signal strength. These design allow data recovery with a Bit Error Rate of less than  $10^{-7}$  over the specific operating conditions.

The system interface includes a simple PCM port and a microprocessor port. The PCM port is compatible with a variety of codecs and data codecs, including the MT896x, MT8950, TP305x and TP306x. The PCM port is also compatible with the MT8994B and MT8995B integrated digital telephone chips, and remains active even if no data is received from the line. The microprocessor port is compatible with both multiplexed and non-multiplexed microprocessor buses.

Fig-1 is a simplified block diagram of the AK130/131. The signal received from the twisted-pair line is applied to the AK130/131 at LIH and LIL. This differential signal is processed, through the adaptive data slicer and peak detectors (AK130), or the adaptive equalizer (AK131), and then routed to the data recovery section. The recovered data signal is passed to the AMI decoder. Decoded data is then processed through the output framer to the PCM-BUS or microprocessor port registers.

#### Internal Timing

The AK130/131 incorporates an on-chip 8.192 MHz crystal oscillator which generates all internal clocks. It also produces two output clocks E40 (4.096 MHz) and E20 (2.048 MHz). These clocks can be used directly as input clocks for peripheral devices such as codecs or integrated digital telephone chips.

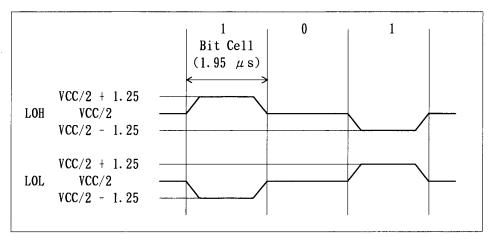

#### Line Code

The AK130/131 transmits data encoded in self-contained AMI pulses at an effective line rate of 512 kbps. A mark is defined as a voltage differential between LOH and LOL, rather than a specific ground-referenced voltage. LOH and LOL are both held at VCC/2 for a space. See Fig-5.

Fig-5 Self-Contained Rectangular AMI Bits

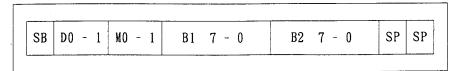

### TCM Frame Format

The AK130/131 transmits and receives high speed digital data over twisted-pair loops using the 23-bit frame format shown in Fig-6. The 20 data bits are framed by the Start Bit (SB) on one end and two Space Bits (SP) on the other end. The 8 kHz line provides 160 kbps for transparent transmission of two 64 kbps B channels, one 16 kbps D channel and one 16 kbps control and maintenance channel (M channel). Both the D and M channel data are available either on the PCM-BUS or through the microprocessor port. B channel data is available only on the PCM-BUS.

#### Operating Modes

The AK130/131 operates in both single and combined port modes. Mode of operation is set by the MS1 level. When MS1 is set to 1, the AK130/131 operates in the single port mode and the microprocessor port is inactive. When MS1 is set to 0, the AK130/131 operates in the combined port mode with both the PCM-BUS and the microprocessor port active.

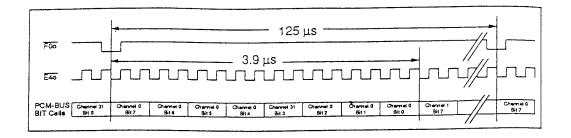

### PCM-BUS

One system interface to the AK130/131 is the flexible PCM-BUS. The PCM-BUS is a synchronous time-division multiplexed serial bus with data streams operating at 2048 kbps. The serial streams are divided into 125  $\mu$  sec frames made up of 32 8-bit channels. Synchronization is achieved with an 8 kHz frame pulse (F00) which identifies the framing boundaries as shown in Fig-7. Data is clocked into the device on the falling edge of the E40 clock, halfway into the bit cell. Data is clocked out on the falling edge of the E40 clock at the start of the bit cell.

The AK130/131 uses only four of the 32 channels available in each PCM-BUS frame. In single port mode, the D channel occupies time slot 0; the M channel occupies time slot 1; and the B1 and B2 channels occupy time slot 2 and 3, respectively, as shown in Fig-8. In combined port mode, time slots 0 and 1 are not used; the B1 and B2 channels occupy time slots 2 and 3.

FSYNC1 and FSYNC2 can be set to F1-, FS- or HFS-type sync pulses by the MS0 pin.

Fig-6 TCM Frame Format

Fig-7 PCM-BUS Stream Format Diagram

Fig-8 PCM-BUS Allocation

#### ASAHI KASEI

#### Microprocessor Port Operation

The microprocessor port is active only in combined port operation. This mode is selected by setting the MS1 pin low. In this mode the two bits from the D channel and the two bits from the M channel are accessed in a common 4-bits nibble. The bandwidth of the two channels can be combined to form an uncommitted 32 kbps channel, or divided into sub-rate channels to meet specific applications. The bit order in the microprocessor port is as follows:

| AD(3) | AD(2) | AD(1) | AD(0) |  |

|-------|-------|-------|-------|--|

| D 1   | DO    | M 1   | MO    |  |

Since only one register is accessible for reading or writing, no address or ALE signal is required. Data is accessed with either a normal bus read or write operation, or a port read or write operation during the 115  $\mu$  s period following the F0o pulse as shown in Fig-9. The AK130/131 microprocessor port includes an active low Chip Select (CS) to allow an external microprocessor to interface with other peripherals.

Fig-9 Microprocessor Port Read/Write Access

#### Applications

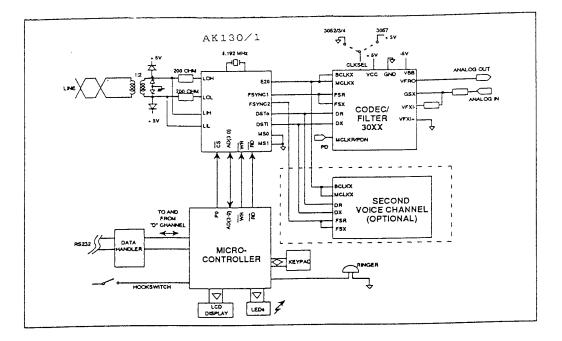

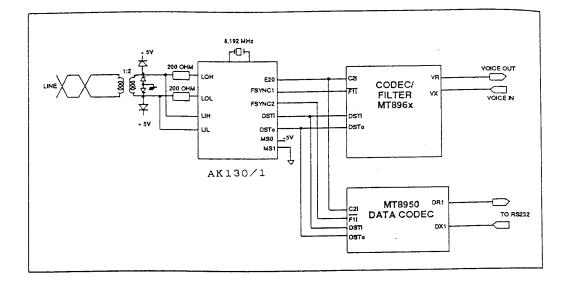

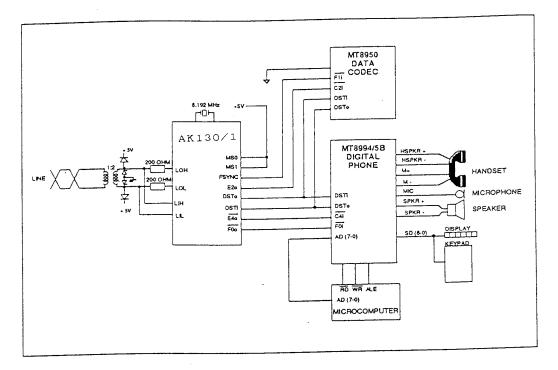

Fig-10 through Fig-12 illustrate typical applications for Voice Terminal, Data and Voice Terminals, and Digital Telephone Set, respectively.

Fig-10 Typical Application - Single or Dual Voice Terminal

Fig-11 Typical Application - Data and Voice Terminal

Fig-12 Typical Application - Voice and Data Digital Telephone Set

|           | 1 - 1 |     | -  |     | ~ ~  |  |

|-----------|-------|-----|----|-----|------|--|

| Packaging | lnf   | 0 F | та | 1 1 | 0 11 |  |

|           |       | • • |    | •   |      |  |

|           |       |     |    |     |      |  |

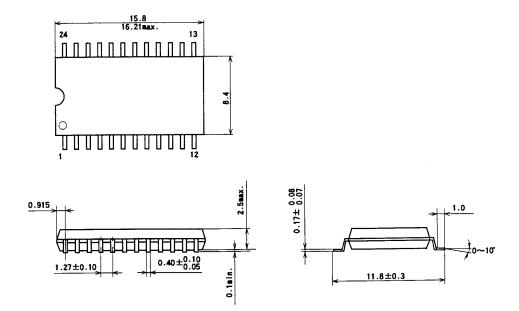

■ 24 pin SOP

### **IMPORTANT NOTICE**

- These products and their specifications are subject to change without notice. Before considering any use or application, consult the Asahi Kasei Microsystems Co., Ltd. (AKM) sales office or authorized distributor concerning their current status.

- AKM assumes no liability for infringement of any patent, intellectual property, or other right in the application or use of any information contained herein.

- Any export of these products, or devices or systems containing them, may require an export license or other official approval under the law and regulations of the country of export pertaining to customs and tariffs, currency exchange, or strategic materials.

- AKM products are neither intended nor authorized for use as critical components in any safety, life support, or other hazard related device or system, and AKM assumes no responsibility relating to any such use, except with the express written consent of the Representative Director of AKM. As used here:

- (a) A hazard related device or system is one designed or intended for life support or maintenance of safety or for applications in medicine, aerospace, nuclear energy, or other fields, in which its failure to function or perform may reasonably be expected to result in loss of life or in significant injury or damage to person or property.

- (b) A critical component is one whose failure to function or perform may reasonably be expected to result, whether directly or indirectly, in the loss of the safety or effectiveness of the device or system containing it, and which must therefore meet very high standards of performance and reliability.

- It is the responsibility of the buyer or distributor of an AKM product who distributes, disposes of, or otherwise places the product with a third party to notify that party in advance of the above content and conditions, and the buyer or distributor agrees to assume any and all responsibility and liability for and hold AKM harmless from any and all claims arising from the use of said product in the absence of such notification.