## NTE6664 Integrated Circuit 64K-Bit Dynamic RAM

#### **Description:**

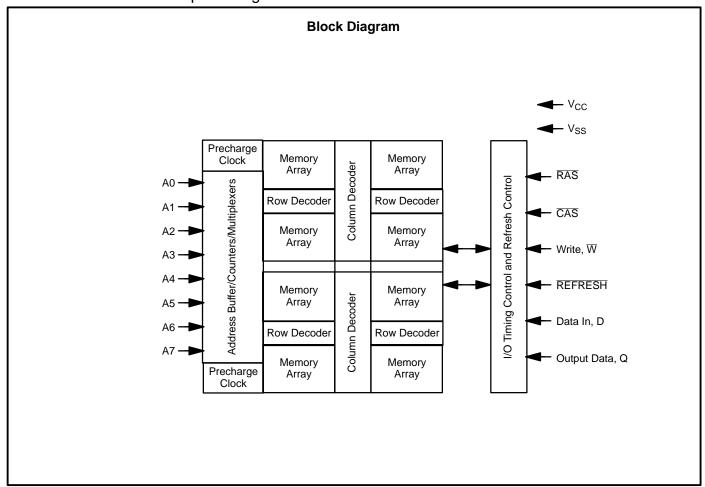

The NTE6664 is a 65,536 Bit, high–speed, dynamic Random Access Memory. Organized as 65,536 one–bit words and fabricated using HMOS high–performance N–Channel silicon–gate technology, this 5V only dynamic RAM combines high performance with low cost and improved reliability.

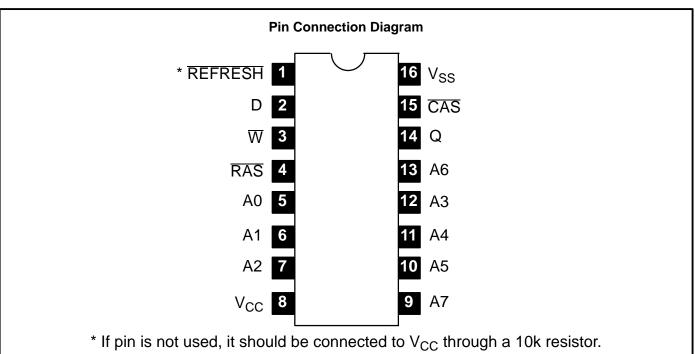

By multiplying row— and column— address inputs, the NTE6664 requires only eight address lines and permits packaging in a standard 16—Lead DIP package. Complete address decoding is done on chip with address latches incorporated. Data out is controlled by CAS allowing for greater system flexibility.

All inputs and outputs, including clocks, are fully TTL compatible. The NTE6664 incorporates a one-transistor cell design and dynamic storage techniques. In addition to the RAS—only refresh mode, the refresh control function available on Pin1 provides two additional modes of refresh, automatic and self refresh.

#### Features:

- Single +5V Operation (±10%)

- Maximum Access Time: 150ns

- Low Power Dissipation:

302.5mW Max (Active)

22mW Max (Standby)

- Three State Data Output

- Early–Write Common I/O Capability

- 128 Cycle, 2ms Refresh

- Control on Pin1 for Automatic or Self Refresh

- RAS-Only Refresh Mode

- CAS Controlled Output

- Fast Page Mode Cycle Time

- Low Soft Error Rate: < 0.1% per 1000 Hrs</li>

#### Absolute Maximum Ratings: (Note 1)

| Voltage on V <sub>CC</sub> Supply Relative to V <sub>SS</sub> , V <sub>CC</sub>                             | –2 to +7V        |

|-------------------------------------------------------------------------------------------------------------|------------------|

| Voltage Relative to V <sub>SS</sub> for Any Pin Except V <sub>CC</sub> , V <sub>in</sub> , V <sub>out</sub> | –1 to +7V        |

| Data Out Current (Short Circuit), I <sub>out</sub>                                                          | 50mA             |

| Power Dissipation, P <sub>D</sub>                                                                           | 1W               |

| Operating Temperature Range, T <sub>A</sub>                                                                 | 0 to +70°C       |

| Storage Temperature Range, T <sub>stg</sub>                                                                 | . −65° to +150°C |

Note 1. Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect the device reliability.

### **Recommended Operating Conditions:** (Note 2, T<sub>A</sub> = 0 to +70°C unless otherwise specified)

| Parameter                                | Symbol          | Min  | Тур | Max | Unit |

|------------------------------------------|-----------------|------|-----|-----|------|

| Supply Voltage (Operating Voltage Range) | V <sub>CC</sub> | 4.5  | 5.0 | 5.5 | V    |

|                                          | $V_{SS}$        | 0    | 0   | 0   | V    |

| Logic 1 Voltage, All Inputs              | $V_{IH}$        | 2.4  | -   | 6.5 | V    |

| Logic 0 Voltage, All Inputs (Note 3)     | $V_{IL}$        | -1.0 | _   | 0.8 | V    |

- Note 2. All voltages referenced to V<sub>SS</sub>.

- Note 3. The device will withstand undershoots to the -2V level with a maximum pulse width 0f 20ns at the -1.5V level. This is periodically sampled rather than 100% tested.

### **DC Characteristics:** $(V_{CC} = 5V \pm 10\%, T_A = 0 \text{ to } +70^{\circ}\text{C} \text{ unless otherwise specified})$

| Parameter                                                           | Symbol              | Test Conditions                             | Min | Тур | Max | Unit |

|---------------------------------------------------------------------|---------------------|---------------------------------------------|-----|-----|-----|------|

| V <sub>CC</sub> Power Supply Current                                | I <sub>CC1</sub>    | t <sub>RC</sub> = 270ns, Note 4             | _   | _   | 55  | mA   |

| V <sub>CC</sub> Power Supply Current (Standby)                      | I <sub>CC2</sub>    | RAS = CAS = V <sub>IH</sub>                 | _   | _   | 4   | mΑ   |

| V <sub>CC</sub> Power Supply Current During RAS only Refresh Cycles | I <sub>CC3</sub>    | t <sub>RC</sub> = 270ns, Note 4             | -   | _   | 45  | mA   |

| Input Leakage Current Any Input Except REFRESH                      | I <sub>lkg(L)</sub> | $V_{SS} < V_{in} < V_{CC}$                  | -   | _   | 10  | μΑ   |

| REFRESH Input Current                                               | I <sub>lkg(F)</sub> | $V_{SS} < V_{in} < V_{CC}$                  | _   | _   | 20  | μΑ   |

| Output Leakage Current                                              | I <sub>lkg(O)</sub> | CAS at Logic 1, 0 ≤ V <sub>out</sub> ≤ 5.5V | _   | _   | 10  | μΑ   |

| Output Logic 1 Voltage                                              | V <sub>OH</sub>     | $I_{out} = -4mA$                            | 2.4 | _   | _   | V    |

| Output Logic 0 Voltage                                              | V <sub>OL</sub>     | I <sub>out</sub> = 4mA                      | _   | _   | 0.4 | V    |

Note 4. Current is a function of cycle rate and output loading; maximum current is measured at the fastest cycle rate with the output open.

# <u>Capacitance:</u> $(V_{CC} = 5V \pm 10\%, f = 1MHz, T_A = +25^{\circ}C, Note 5, Periodically Sampled Rather Than 100% Tested)$

| Parameter                                                | Symbol           | Test Conditions                         | Min | Тур    | Max    | Unit |

|----------------------------------------------------------|------------------|-----------------------------------------|-----|--------|--------|------|

| Input Capacitance A0 – A7, D<br>RAS, CAS, WRITE, REFRESH | C <sub>in</sub>  |                                         | 1 1 | 3<br>6 | 5<br>8 | pF   |

| Output Capacitance Q                                     | C <sub>out</sub> | CAS = V <sub>IH</sub> to Disable Output | -   | 5      | 7      | pF   |

Note 5. Capacitance measured with a Boonton Meter or effective capacitance calculated from the equation:  $C = I\Delta t/\Delta V$ .

# Read, Write, and Read–Modify–Write Cycles: $(V_{CC} = 5V \pm 10\%, T_A = 0 \text{ to } +70^{\circ}\text{C} \text{ unless otherwise specified, Notes 6, 7, and 8)}$

| Parameter                        | Symbol           | Test Conditions  | Min | Тур | Max   | Unit |

|----------------------------------|------------------|------------------|-----|-----|-------|------|

| Random Read or Write Cycle Time  | t <sub>RC</sub>  | Note 9, Note 10  | 270 | _   | _     | ns   |

| Read–Write Cycle Time            | t <sub>RWC</sub> | Note 9, Note 10  | 280 | _   | _     | ns   |

| Access Time from RAS             | t <sub>RAC</sub> | Note 11, Note 13 | _   | _   | 150   | ns   |

| Access Time from CAS             | t <sub>CAC</sub> | Note 12, Note 13 | _   | _   | 75    | ns   |

| Output Buffer and Turn–Off Delay | t <sub>OFF</sub> | Note 19          | 0   | _   | 30    | ns   |

| RAS Precharge Time               | t <sub>RP</sub>  |                  | 100 | _   | _     | ns   |

| RAS Pulse Width                  | t <sub>RAS</sub> |                  | 150 | _   | 10000 | ns   |

| CAS Pulse Width                  | tcas             |                  | 75  | _   | 10000 | ns   |

Read, Write, and Read–Modify–Write Cycles (Cont'd):  $(V_{CC} = 5V \pm 10\%, T_A = 0 \text{ to } +70^{\circ}\text{C}$  unless otherwise specified, Notes 6, 7, and 8)

| Parameter                                           | Symbol            | Test Conditions | Min  | Тур | Max  | Unit |

|-----------------------------------------------------|-------------------|-----------------|------|-----|------|------|

| RAS to CAS Delay Time                               | t <sub>RCD</sub>  | Note 14         | 25   | _   | 75   | ns   |

| Row Address Setup Time                              | t <sub>ASR</sub>  |                 | 0    | -   | _    | ns   |

| Row Address Hold Time                               | t <sub>RAH</sub>  |                 | 20   | -   | _    | ns   |

| Column Address Setup Time                           | t <sub>ASC</sub>  |                 | 0    | -   | _    | ns   |

| Column Address Hold Time                            | t <sub>CAH</sub>  |                 | 35   | _   | _    | ns   |

| Column Address Hold Time Referenced to RAS          | t <sub>AR</sub>   | Note 18         | 95   | -   | _    | ns   |

| Transition Time (Rise and Fall)                     | t <sub>T</sub>    |                 | 3    | _   | 50   | ns   |

| Read Command Setup Time                             | t <sub>RCS</sub>  |                 | 0    | _   | _    | ns   |

| Read Command Hold Time Referenced to CAS            | t <sub>RCH</sub>  | Note 15         | 0    | _   | _    | ns   |

| Read Command Hold Time Referenced to RAS            | t <sub>RRH</sub>  | Note 15         | 0    | _   | _    | ns   |

| Write Command Hold Time                             | t <sub>WCH</sub>  |                 | 35   | -   | _    | ns   |

| Write Command Hold Time Referenced to RAS           | t <sub>WCR</sub>  | Note 18         | 95   | _   | _    | ns   |

| Write Command Pulse Width                           | t <sub>WP</sub>   |                 | 35   | _   | _    | ns   |

| Write Command to RAS Lead Time                      | t <sub>RWL</sub>  |                 | 45   | _   | _    | ns   |

| Write Command to CAS Lead Time                      | t <sub>CWL</sub>  |                 | 45   | _   | _    | ns   |

| Data in Setup Time                                  | t <sub>DS</sub>   | Note 16         | 0    | _   | _    | ns   |

| Data in Hold Time                                   | t <sub>DH</sub>   | Note 16         | 35   | _   | _    | ns   |

| Data in Hold Time Referenced to RAS                 | t <sub>DHR</sub>  | Note 18         | 95   | _   | _    | ns   |

| CAS to RAS Precharge Time                           | t <sub>CRP</sub>  |                 | -10  | _   | _    | ns   |

| RAS Hold Time                                       | t <sub>RSH</sub>  |                 | 75   | _   | _    | ns   |

| Refresh Period                                      | t <sub>RFSH</sub> |                 | _    | _   | 2    | ms   |

| Write Command Setup Time                            | t <sub>WCS</sub>  | Note 17         | -10  | -   | _    | ns   |

| CAS to Write Delay                                  | t <sub>CWD</sub>  | Note 17         | 45   | _   | _    | ns   |

| RAS to Write Delay                                  | t <sub>RWD</sub>  | Note 17         | 120  | -   | _    | ns   |

| CAS Hold Time                                       | t <sub>CSH</sub>  |                 | 150  | -   | _    | ns   |

| CAS Precharge Time (Page Mode Cycle Only)           | t <sub>CP</sub>   |                 | 60   | -   | _    | ns   |

| Page Mode Cycle Time                                | t <sub>PC</sub>   |                 | 145  | _   | _    | ns   |

| RAS to REFRESH Delay                                | t <sub>RFD</sub>  |                 | -10  | -   | _    | ns   |

| REFRESH Period (Battery Backup Mode)                | t <sub>FBP</sub>  |                 | 2000 | -   | _    | ns   |

| REFRESH to RAS Precharge Time (Battery Backup Mode) | t <sub>FBR</sub>  |                 | 320  | _   | _    | ns   |

| REFRESH Cycle Time (Auto Pulse Mode)                | t <sub>FC</sub>   |                 | 270  | _   | _    | ns   |

| REFRESH Pulse Period (Auto Period Mode)             | t <sub>FP</sub>   |                 | 60   | _   | 2000 | ns   |

| REFRESH to RAS Setup Time (Auto Pulse Mode)         | t <sub>FSR</sub>  |                 | -30  | _   | _    | ns   |

| REFRESH to RAS Delay Time (Auto Pulse Mode)         | t <sub>FRD</sub>  |                 | 320  | _   | _    | ns   |

| REFRESH Inactive Time                               | t <sub>FI</sub>   |                 | 60   | _   | _    | ns   |

| RAS to REFRESH Lead Time                            | t <sub>FRL</sub>  |                 | 370  | _   | _    | ns   |

| RAS Inactive Time During REFRESH                    | t <sub>FRI</sub>  |                 | 370  | -   | -    | ns   |

- Note 6.  $V_{IH}$  min and  $V_{IL}$  max are reference levels for measuring timing of input signals. Transition times are measured between  $V_{IH}$  and  $V_{IL}$ .

- Note 7. An initial pause of 100μs is required after power–up followed by 8 RAS cycles before proper device operation is guaranteed.

- Note 8. The transition time specification applies for all input signals. In addition to meeting the transition rate specification, all input signals must transmit between  $V_{IH}$  and  $V_{IH}$  (or between  $V_{IL}$  and  $V_{IH}$ ) in a monotonic manner.

- Note 9. The specification for  $t_{RC}(min)$  and  $t_{RMW}(min)$  are used only to indicate cycle time at which proper operation over the full temperature range (0°C  $\leq$  T<sub>A</sub>  $\leq$  +70°C) is assured.

- Note 10. AC measurements  $t_T = 5$ ns.

- Note 11. Assumes that  $t_{RCD} \le t_{RCD}(max)$ .

- Note 12. Assumes that  $t_{RCD} \ge t_{RCD}(max)$ .

- Note 13. Measured with a current load equivalent to 2 TTL ( $-200\mu A$ , +4mA) loads and 100pF with the data output trip points set at  $V_{OH} = 2V$  and  $V_{OL} = 0.8V$ .

- Note 14. Operation within the  $t_{RCD}(max)$  limit ensures that  $t_{RAC}(max)$  can be met,  $t_{RCD}(max)$  is specified as a reference point only; if  $t_{RCD}$  is greater than the specified  $t_{RCD}(max)$  limit, then access time is controlled exclusively by  $t_{CAC}$ .

- Note 15. Either t<sub>RRH</sub> or t<sub>RCH</sub> must be satisfied for a read cycle.

- Note 16. These parameters are referenced to CAS leading edge in random write cycles and to WRITE leading edge in delayed write or read–modify–write cycles.

- Note 17.  $t_{WCS}$ ,  $t_{CWD}$ , and  $t_{RWD}$  are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only; if  $t_{WCS} \ge t_{WCS}$ (min), the cycle is an early write cycle and the data out pin will remain open circuit (high impedance) throughout the entire cycle; if  $t_{CWD} \ge t_{CWD}$ (min) and  $t_{RWD} \ge t_{RWD}$ (min), the cycle is read–write cycle and the data out will contain data read from the selected cell; if neither of the above sets of conditions is satisfied, the condition of the data out (at access time) is indeterminate.

- Note 19. t<sub>OFF</sub>(max) defines the time at which the output achieves the open circuit condition and is not referenced to output voltage levels.