Rev. V2

**Buffer Amplifier** 37.0-40.0 GHz Mimix Broadband

#### **Features**

- 21.0 dB Small Signal Gain

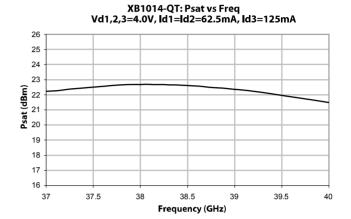

- +22.0 dBm Psat

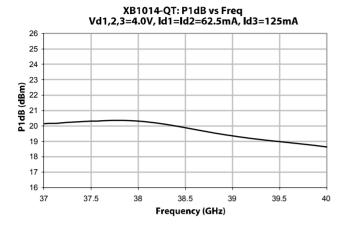

- +20.0 dBm P1dB

- +30.5 dBm Output IP3

- Variable Gain with Adjustable Bias

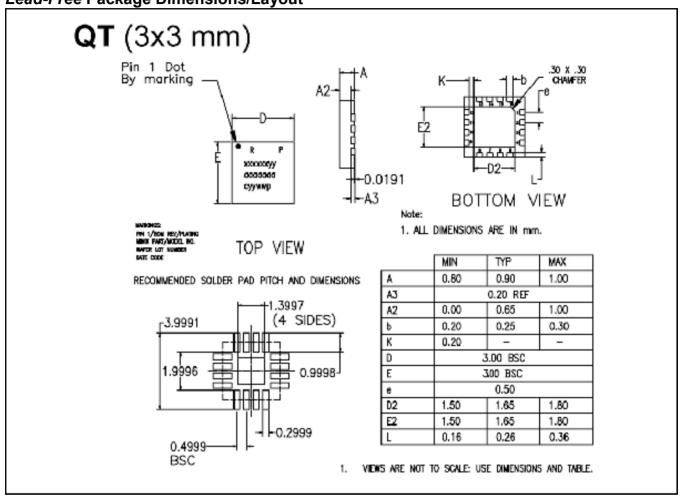

- Lead-free 4 mm 16-lead PQFN Package

- 100% RF, DC and Output Power Testing

- RoHS\* Compliant and 260°C Reflow Compatible

### **Description**

M/A-COM Tech's three stage 37.0-40.0 GHz GaAs MMIC buffer amplifier has a small signal gain of 21.0 dB and 20.0 dBm P1dB output compression point. The device also provides variable gain regulation with adjustable bias. The device is ideally suited as an LO or RF buffer stage with broadband performance at a very low cost. The device comes in an RoHS compliant 3x3mm QFN surface mount package offering excellent RF and thermal properties. This device has been designed for use in GHz Point-to-Point Microwave applications.

### **Ordering Information**

| Part Number    | Package          |  |  |

|----------------|------------------|--|--|

| XB1014-QT-0G00 | bulk quantity    |  |  |

| XB1014-QT-0G0T | tape and reel    |  |  |

| XB1014-QT-EV1  | evaluation board |  |  |

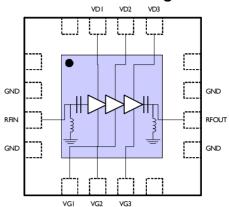

### **Functional Block Diagram/Board Layout**

### **Pin Configuration**

| Pin No. | Function    | Pin No. | No. Function |  |  |

|---------|-------------|---------|--------------|--|--|

| 3       | RF Input    | 10      | RF Output    |  |  |

| 5       | Gate 1 Bias | 13      | Drain 3 Bias |  |  |

| 6       | Gate 2 Bias | 14      | Drain 2 Bias |  |  |

| 7       | Gate 3 Bias | 15      | Drain 1 Bias |  |  |

# Absolute Maximum Ratings<sup>1, 2</sup>

| Parameter                                     | Absolute Max.                        |  |  |  |  |  |

|-----------------------------------------------|--------------------------------------|--|--|--|--|--|

| Supply Voltage (Vd1,2,3)                      | +4.3 V                               |  |  |  |  |  |

| Supply Voltage (Vg1,2,3)                      | -1.5V < Vg < 0V                      |  |  |  |  |  |

| Input Power (Pin)                             | +20 dBm                              |  |  |  |  |  |

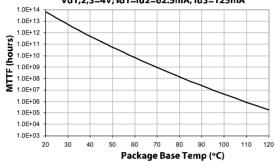

| Abs. Max Junction/Channel Temp                | MTTF Graph <sup>1</sup>              |  |  |  |  |  |

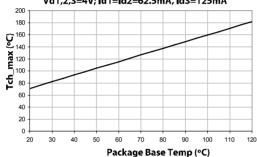

| Max. Operating Junction/Channel Temp          | 150 °C                               |  |  |  |  |  |

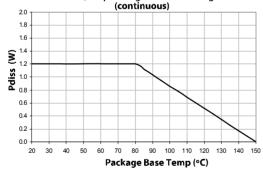

| Continuous Power Dissipation (Pdiss) at 85 °C | 1.2 W                                |  |  |  |  |  |

| Thermal Resistance                            | 47 °C/W                              |  |  |  |  |  |

| Operating Temperature (Ta)                    | -55 °C to MTTF<br>Graph <sup>1</sup> |  |  |  |  |  |

| Storage Temperature (Tstg)                    | -65 °C to +165 °C                    |  |  |  |  |  |

| Mounting Temperature                          | See solder reflow profile            |  |  |  |  |  |

| ESD Min Machine Model (MM)                    | Class A                              |  |  |  |  |  |

| ESD Min Human Body Model (HBM)                | Class 1A                             |  |  |  |  |  |

| MSL Level                                     | MSL1                                 |  |  |  |  |  |

Channel temperature directly affects a device's MTTF. Channel temperature should be kept as low as possible to maximize lifetime

For saturated performance it is recommended that the sum of (2\*Vdd + abs(Vgg)) <9V

Buffer Amplifier

Rev. V2

37.0-40.0 GHz

Mimi× Broadband

## **Electrical Specifications: 37-40 GHz (Ambient Temperature T = 25°C)**

| Parameter                                     | Units | Min. | Тур. | Max. |

|-----------------------------------------------|-------|------|------|------|

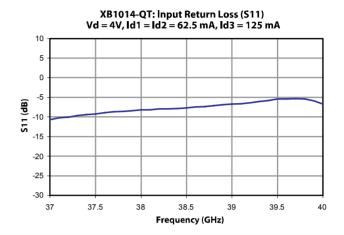

| Input Return Loss (S11)                       | dB    | -    | 7.0  | 40.0 |

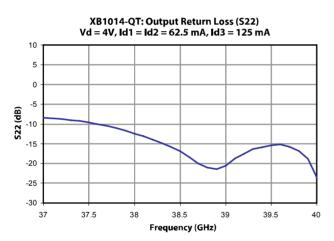

| Output Return Loss (S22)                      | dB    | -    | 10.0 | 1    |

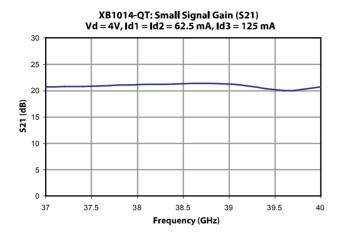

| Small Signal Gain (S21)                       | dB    | 17.0 | 21.0 | -    |

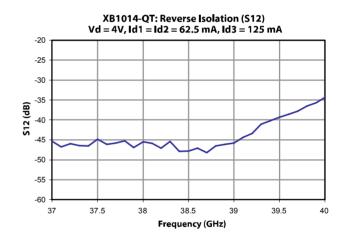

| Reverse isolation (S12)                       | dB    | -    | 40.0 | 24.5 |

| Output Power for 1dB Compression Point (P1dB) | dBm   | -    | 20.0 | -    |

| Saturated Output Power (Psat)                 | dBm   | 19.5 | 22.0 | -    |

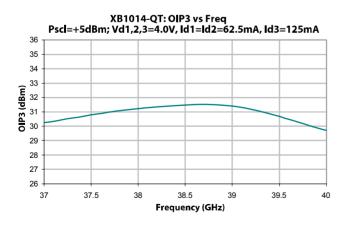

| Output IP3 (Psci = 4 dBm)                     | dBm   | 27.0 | 30.5 | -    |

| Drain Bias Voltage (Vd1,2,3)                  | V     | -    | 4.0  | 4.0  |

| Gate Bias Voltage (Vg1,2,3)                   | V     | -1.0 | -0.3 | -0.1 |

| Supply Current (ld1,2,3)                      | mA    | -    | 250  | 300  |

<sup>•</sup> India Tel: +91.80.43537383 • China

<sup>•</sup> China Tel: +86.21.2407.1588

Buffer Amplifier

Rev. V2

37.0-40.0 GHz

Mimi× Broadband

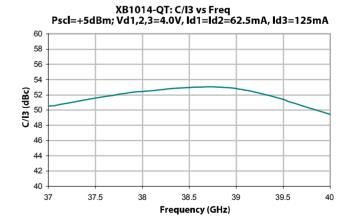

### **Typical Performance Curves**

typical. Mechanical outline has been fixed. Engineering samples and/or test data may be available.

**Buffer Amplifier** Rev. V2 37.0-40.0 GHz Mimix Broadband

## **Typical Performance Curves (cont.)**

**Buffer Amplifier** 37.0-40.0 GHz Mimix Broadband

#### **MTTF**

#### XB1014-QT: MTTF hours vs. Package Base Temperature Vd1,2,3=4V; ld1=ld2=62.5mA, ld3=125mA

#### XB1014-QT: Tch (max) vs. Package Base Temperature Vd1,2,3=4V; Id1=Id2=62.5mA, Id3=125mA

#### XB1014-QT: Operating Power De-rating Curve

Buffer Amplifier

Rev. V2

37.0-40.0 GHz

Mimi× Broadband

App Note [1] Biasing - It is recommended to bias the amplifier with Vd=4.0V and IdTOTAL=250mA. It is also recommended to use active biasing to keep the currents constant as the RF power and temperature vary; this gives the most reproducible results. Depending on the supply voltage available and the power dissipation constraints, the bias circuit may be a single transistor or a low power operational amplifier, with a low value resistor in series with the drain supply used to sense the current. The gate of the pHEMT is controlled to maintain correct drain current and thus drain voltage. The typical gate voltage needed to do this is -0.3V. Typically the gate is protected with Silicon diodes to limit the applied voltage. Also, make sure to sequence the applied voltage to ensure negative gate bias is available before applying the positive drain supply.

**App Note [2] Bias Arrangement -** Each DC pin (Vd and Vg) needs to have DC bypass capacitance (100pF/10nF/1uF) as close to the package as possible.

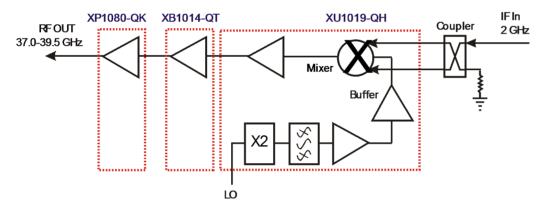

### **Typical Application**

MMIC-based 37.0-40.0 GHz Transmitter Block Diagram

Buffer Amplifier

37.0-40.0 GHz

Rev. V2

Mimi× Broadband

## **Handling Procedures**

Please observe the following precautions to avoid damage:

### **Static Sensitivity**

Gallium Arsenide Integrated Circuits are sensitive to electrostatic discharge (ESD) and can be damaged by static electricity. Proper ESD control techniques should be used when handling these class 2 devices.

typical. Mechanical outline has been fixed. Engineering samples and/or test data may be available.

<sup>•</sup> North America Tel: 800.366.2266 • Europe Tel: +353.21.244.6400 • India Tel: +91.80.43537383 • China Tel: +86.21.2407.1588