## ASSP (for Mobile Terminals)

# Power Management IC for Mobile Terminals 3ch DC/DC Converter + 4ch LDO

### MB39C316

### **■ DESCRIPTION**

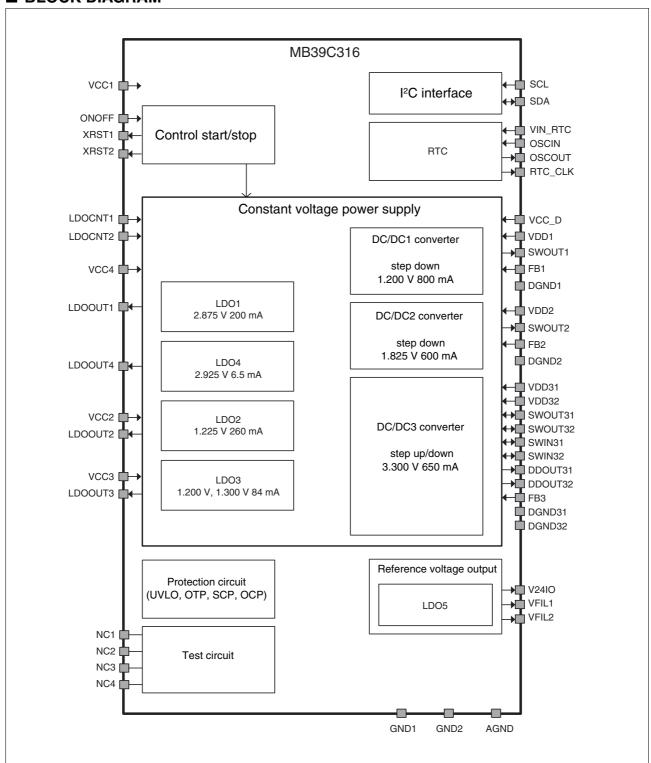

The MB39C316 is equipped with the 3 ch DC/DC converter and the 4 ch linear regulator (LDO), and is the power supply LSI for mobile terminals which operate in the range of power supply voltage with 1-cell Li-ion power by 1ch high efficiency voltage step-up/down DC/DC.

The MB39C316 contains the 2ch synchronous rectification DC/DC converter with current mode system and the 1ch voltage step-up/down DC/DC converter. Detecting load current by each DC/DC converter alternates the Normal mode (PWM) with the ECO mode (PFM) automatically.

MB39C316 has the built-in 4ch LDO which is suitable to supply voltage to the system block and the built-in 1ch LDO which generates stable internal reference voltage.

It is possible to control a notice of internal condition, the power supply and reset in order to support the communication interface which is compliant with the I<sup>2</sup>C bus standard.

### **■ FEATURES**

Input voltage range

Step-down regulators

Step-up/down regulator

Linear regulator (LDO)

2.7 V to 5.5 V

2 channels

1 channel

4 channels

- Possible to select output voltage: LDO3 1.2 V/1.3 V (register setting)

- On/Off control of LDO and DC/DC converter by external signals and register settings

- Compliant with I2C bus standard (Max 400 kbps)

- Possible to output the 32.768 kHz clock by connecting crystal oscillator

- Protection function: Over current protection (OCP), Output short circuit protection (SCP),

Under voltage lock out protection (UVLO), Over temperature protection (OTP)

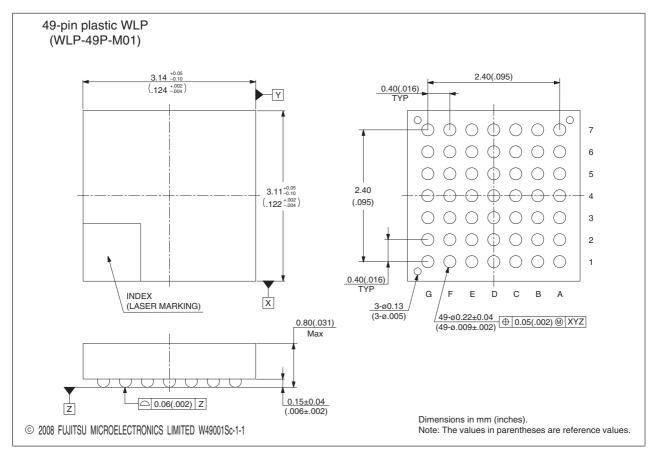

• Package : 49 pin, WL-CSP (3.14 mm × 3.11 mm × 0.8 mm)

### **■ APPLICATIONS**

- · Mobile WiMAX terminals

- Other mobile terminals etc.

### **■ PIN ASSIGNMENT**

| I III ASSIC |        |         | (B      | OTTOM VIE | EW)     |         |         |   |

|-------------|--------|---------|---------|-----------|---------|---------|---------|---|

| -           | G      | F       | E       | D         | С       | В       | Α       |   |

| 7           | NC3    | VDD31   | SWOUT31 | DGND31    | SWIN31  | DDOUT31 | NC2     | 7 |

| 6           | FB3    | VDD32   | SWOUT32 | DGND32    | SWIN32  | DDOUT32 | OSCIN   | 6 |

| 5           | AGND   | VCC_D   | LDOCNT1 | LDOCNT2   | VIN_RTC | GND1    | OSCOUT  | 5 |

| 4           | SWOUT1 | VDD1    | FB1     | SCL       | V24IO   | VFIL2   | VFIL1   | 4 |

| 3           | DGND1  | DGND2   | FB2     | SDA       | ONOFF   | VCC1    | LDOOUT2 | 3 |

| 2           | SWOUT2 | VDD2    | XRST2   | GND2      | VCC4    | VCC2    | VCC3    | 2 |

| 1           | NC4    | RTC_CLK | XRST1   | LDOOUT4   | LDOOUT1 | LDOOUT3 | NC1     | 1 |

| L           | G      | F       | Е       | D         | С       | В       | А       |   |

|             |        |         |         |           |         |         |         |   |

### **■ PIN DISCRIPTIONS**

|                     |    |         |     | Descriptions                                                      |

|---------------------|----|---------|-----|-------------------------------------------------------------------|

| <u> </u>            | В3 | VCC1    | I   | Power supply input, Power supply input pin for LDO2, LDO3 control |

|                     | B2 | VCC2    | I   | Power supply input pin for LDO2 power                             |

|                     | A2 | VCC3    | I   | Power supply input pin for LDO3 power                             |

| Evtornol            | C2 | VCC4    | I   | Power supply input pin for LDO1, LDO4 control/power               |

| External _<br>power | F5 | VCC_D   | I   | Power supply input pin for DC/DC converter control                |

| supply              | F4 | VDD1    | I   | Power supply input pin for DC/DC1 converter power                 |

|                     | F2 | VDD2    | I   | Power supply input pin for DC/DC2 converter power                 |

| _                   | F7 | VDD31   | I   | Power supply input pin 1 for DC/DC3 converter power               |

| _                   | F6 | VDD32   | ı   | Power supply input pin 2 for DC/DC3 converter power               |

| _                   | C5 | VIN_RTC | I   | Power supply input pin for RTC                                    |

|                     | E5 | LDOCNT1 | I   | LDO output control input pin 1                                    |

| _                   | D5 | LDOCNT2 | I   | LDO output control input pin 2                                    |

| _                   | D1 | LDOOUT4 | 0   | LDO4 output pin ( + 2.9 V)                                        |

| _                   | B1 | LDOOUT3 | 0   | LDO3 output pin ( + 1.2 V/1.3 V)                                  |

| _                   | C1 | LDOOUT1 | 0   | LDO1 output pin ( + 2.9 V)                                        |

| _                   | A3 | LDOOUT2 | 0   | LDO2 output pin ( + 1.2 V)                                        |

| _                   | G4 | SWOUT1  | 0   | DC/DC1 converter inductance connection output pin                 |

| Constant            | E4 | FB1     | I   | DC/DC1 converter output voltage feedback input pin (1.2 V)        |

| voltage             |    | SWOUT2  | 0   | DC/DC2 converter inductance connection output pin                 |

| power<br>supply     | E3 | FB2     | ı   | DC/DC2 converter output voltage feedback input pin (1.8 V)        |

|                     | E7 | SWOUT31 |     | DC/DC3 converter inductance connection pin 1                      |

| _                   | E6 | SWOUT32 |     | DC/DC3 converter inductance connection pin 2                      |

| _                   | C7 | SWIN31  |     | DC/DC3 converter inductance connection pin 1                      |

| _                   | C6 | SWIN32  |     | DC/DC3 converter inductance connection pin 2                      |

| _                   | B7 | DDOUT31 | 0   | DC/DC3 converter output pin 1                                     |

| _                   | B6 | DDOUT32 | 0   | DC/DC3 converter output pin 2                                     |

| _                   | G6 | FB3     | ı   | DC/DC3 converter output voltage feedback input pin (3.3 V)        |

| I <sup>2</sup> C    | D4 | SCL     | ı   | I <sup>2</sup> C interface clock input pin                        |

| interface           | D3 | SDA     | I/O | I <sup>2</sup> C interface data I/O pin                           |

|                     | A6 | OSCIN   | I   | Input pin for crystal oscillator connection                       |

| RTC                 | A5 | OSCOUT  | 0   | Output pin for crystal oscillator connection                      |

| _                   | F1 | RTC_CLK | 0   | 32.768 kHz Clock output pin                                       |

|                     | C3 | ONOFF   | I   | Enable pin for the MB39C316                                       |

| Start/Stop          | E1 | XRST1   | 0   | Reset output pin 1                                                |

|                     | E2 | XRST2   | 0   | Reset output pin 2                                                |

|                     | C4 | V24IO   | 0   | Power supply output pin for internal 2.4 V I/O                    |

| Reference           | A4 | VFIL1   | 0   | Reference voltage output pin 1 (0.47 µF connected )               |

| voltage             | B4 | VFIL2   | 0   | Reference voltage output pin 2 (0.47 µF connected )               |

(Continued)

3

### (Continued)

4

| Continue |         | 1        |     | T                                                                   |

|----------|---------|----------|-----|---------------------------------------------------------------------|

| Block    | Pin No. | Pin name | I/O | Descriptions                                                        |

|          | A1      | NC1      | _   | Pin for TEST (Set to Non Connect. Prohibited to connect to others.) |

| TEST     | A7      | NC2      | _   | Pin for TEST (Set to Non Connect. Prohibited to connect to others.) |

| 1231     | G7      | NC3      | _   | Pin for TEST (Set to Non Connect. Prohibited to connect to others.) |

|          | G1      | NC4      | _   | Pin for TEST (Set to Non Connect. Prohibited to connect to others.) |

|          | B5      | GND1     | _   | Ground pin (COMMON, RTC)                                            |

|          | D2      | GND2     | _   | Ground pin (LDO, INPUT_IF, OUTPUT_IF)                               |

|          | G5      | AGND     | _   | Ground pin (DC/DC converter control block)                          |

| GND      | G3      | DGND1    | _   | DC/DC1 converter ground pin                                         |

|          | F3      | DGND2    | _   | DC/DC2 converter ground pin                                         |

|          | D7      | DGND31   | _   | DC/DC3 converter ground pin 1                                       |

|          | D6      | DGND32   | _   | DC/DC3 converter ground pin 2                                       |

### **■ BLOCK DIAGRAM**

### ■ ABSOLUTE MAXIMUM RATINGS

| Parameter                     | Symbol   | Condition                                | Rat          | ing         | Unit  |

|-------------------------------|----------|------------------------------------------|--------------|-------------|-------|

| Parameter                     | Syllibol | Condition                                | Min          | Max         | Ollit |

|                               | Vmax1    | VCC1, VCC_D, VDD1,<br>VDD2, VDD31, VDD32 | - 0.3        | + 6.0       | V     |

| Power supply voltage          | Vmax2    | VCC2, VCC3                               | - 0.3        | + 6.0       | V     |

|                               | Vmax3    | VCC4                                     | - 0.3        | + 6.0       | V     |

|                               | Vmax4    | VIN_RTC                                  | - 0.3        | + 3.6       | V     |

|                               | Vinmax1  | LDOCNT1, LDOCNT2, SCL, SDA               | - 0.3        | Vvcc3 + 0.3 | V     |

| Input voltage                 | Vinmax2  | ONOFF, FB1, FB2, FB3                     | - 0.3        | Vvcc1 + 0.3 | V     |

|                               | Vinmax3  | OSCIN                                    | - 0.3        | Vrtc        | V     |

| Storage temperature range     | Tstg     | _                                        | - 55         | + 125       | °C    |

| ESD withstand voltage         | Vesdh    | Human Body Model<br>(100 pF, 1.5 kΩ)     | - 1000       | + 1000      | V     |

| withstand voltage             | Vesdm    | Machine Model (200 pF, 0 $\Omega$ )      | <b>– 100</b> | + 100       | ٧     |

| latch-up<br>withstand voltage | Vlatchup | EIA/JEDEC Standard                       | <b>– 150</b> | + 150       | mA    |

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

### ■ RECOMMENDED OPERATION CONDITIONS

| Doromotor                   | Cumbal | Condition                                |       | Value |         | Heit |

|-----------------------------|--------|------------------------------------------|-------|-------|---------|------|

| Parameter                   | Symbol | Condition                                | Min   | Тур   | Max     | Unit |

| Power supply voltage        | Vvcc1  | VCC1, VCC_D, VDD1,<br>VDD2, VDD31, VDD32 | 2.7   | 3.3   | 5.5     | V    |

|                             | Vvcc2  | VCC2, VCC3                               | 1.75  | _     | 1.90    | V    |

|                             | Vvcc3  | VCC4                                     | 3.2   | _     | 5.5     | V    |

|                             | Vrtc   | VIN_RTC                                  | 2.325 | _     | 2.475   | V    |

|                             | VIvcc1 | ONOFF                                    | 0.0   |       | Vvcc1   | V    |

|                             | VIvcc3 | LDOCNT1, LDOCNT2, SCL, SDA               | 0.0   | _     | Vvcc3   | V    |

| Input voltage               | VIdd1  | FB1                                      | 0.0   | _     | Voutdd1 | V    |

|                             | Vldd2  | FB2                                      | 0.0   | _     | Voutdd2 | V    |

|                             | VIdd3  | FB3                                      | 0.0   | _     | Voutdd3 | V    |

|                             | VIrtc  | OSCIN                                    | 0.0   | _     | Vrtc    | V    |

| Operating temperature range | Ta     | _                                        | - 30  | _     | + 85    | °C   |

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

> Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure. No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

### **■ ELECTRICAL CHARACTERISTICS**

### 1. DC characteristics

(Ta = - 30 °C to + 85 °C, Vvcc1 = 2.7 V to 5.5 V ,Vvcc3 = 3.2 V to 5.5 V, Vvcc2 = 1.75 V to 1.90 V,Vrtc = 2.325 V to 2.475 V)

|      | Parameter              |           | Condition                                    | _              |       | Value |       | Unit  |

|------|------------------------|-----------|----------------------------------------------|----------------|-------|-------|-------|-------|

|      | Parameter              | Symbol    | Condition                                    | 1              | Min   | Тур   | Max   | Unit  |

|      | Output voltage         | Voutld1   | lout = 0 to lomax                            |                | 2.800 | 2.875 | 3.000 | V     |

|      | Maximum output current | loutld1   | _                                            | _              |       |       | _     | mA    |

|      | Input stability        | Vlineld1  | lout = - 10 mA                               | lout = - 10 mA |       | 5     | _     | mV    |

|      | Load stability         | Vloadld1  | lout = 0 to lomax                            |                |       | 20    | _     | mV    |

|      | Ripple removal         | RR1kld1   | Vinput = 0.2 Vpp,                            | f = 1 kHz      |       | 60    | _     | dB    |

| LDO1 | ratio                  | RR10kld1  | Vvcc1 = 3.3 V,<br>lout = lomax/2             | f = 10 kHz     |       | 40    |       | dB    |

|      | Output noise voltage   | Vnoiseld1 | f = 10 Hz to 100 kHz<br>lout = 10 mA to loma |                | 30    | 45    | μVrms |       |

|      | Rise time              | Trld1     | Vvcc1 = 3.3 V, lout =<br>Vout = 90%          | _              | 200   | _     | μs    |       |

|      | Fall time              | Tfld1     | Vvcc1 = 3.3 V, lout =<br>Vout = 10%          | _              | 70    | _     | μs    |       |

|      | Output voltage         | Voutld2   | lout = 0 to lomax                            | 1.150          | 1.225 | 1.300 | V     |       |

|      | Maximum output current | loutld2   | _                                            |                | 260   |       | _     | mA    |

|      | Input stability        | Vlineld2  | lout = - 10mA                                |                | _     | 5     | _     | mV    |

|      | Load stability         | Vloadld2  | lout = 0 to lomax                            |                | _     | 25    | _     | mV    |

|      | Ripple removal         | RR1kld2   | Vinput = 0.2 Vpp,                            | f = 1 kHz      | _     | 60    |       | dB    |

| LDO2 | ratio                  | RR10kld2  | Vvcc1, lout = 1 mA<br>to lomax               | f = 10 kHz     | _     | 40    | _     | dB    |

|      | Output noise voltage   | Vnoiseld2 | f = 10 Hz to 100 kHz<br>lout = 10 mA to loma |                |       | 30    | 45    | μVrms |

|      | Rise time              | Trld2     | Vvcc1, lout = 0 mA,<br>Vout = 90%            |                |       | 70    |       | μs    |

|      | Fall time              | Tfld2     | Vvcc1, lout = 0 mA,<br>Vout = 10%            |                | _     | 150   | _     | μs    |

8

|      | Davamatav              | Comple    | Condition                                                         |       | Value |       | Unit  |

|------|------------------------|-----------|-------------------------------------------------------------------|-------|-------|-------|-------|

| •    | Parameter              | Symbol    | Condition                                                         | Min   | Тур   | Max   | Unit  |

|      | Output voltage         | Voutld3   | lout = 0 to lomax, VSEL_SYN = "0" ( register 02 <sub>H</sub> [0]) | 1.100 | 1.200 | 1.300 | V     |

|      | Output voltage         | Voulido   | lout = 0 to lomax, VSEL_SYN = "1" ( register 02⊦[0])              | 1.200 | 1.300 | 1.400 | V     |

|      | Maximum output current | loutld3   | _                                                                 | 84    |       |       | mA    |

|      | Input stability        | Vlineld3  | lout = - 10 mA                                                    |       | 5     | _     | mV    |

|      | Load stability         | Vloadld3  | lout = 0 to lomax                                                 |       | 20    |       | mV    |

| LDO3 | Ripple removal         | RR1kld3   | Vinput = 0.2 Vpp, f = 1 kHz                                       | _     | 60    | _     | dB    |

|      | ratio                  | RR10kld3  | Vvcc1, lout = 1mA to lomax $f = 10 \text{ kHz}$                   |       | 40    |       | dB    |

|      | Output noise voltage   | Vnoiseld3 | f = 10 Hz to 100 kHz,<br>lout = 10 mA to lomax                    | _     | 30    | 40    | μVrms |

|      | Rise time              | Trld3     | Vvcc1, lout = 0 mA,<br>Vout = 90%                                 |       | 60    |       | μs    |

|      | Fall time              | Tfld3     | Vvcc1, lout = 0 mA,<br>Vout = 10%                                 | _     | 150   | _     | μs    |

|      | Output voltage         | Voutld4   | lout = 0 to lomax                                                 | 2.850 | 2.925 | 3.000 | V     |

|      | Maximum output current | loutld4   | _                                                                 | 6.5   | _     | _     | mA    |

|      | Input stability        | Vlineld4  | lout = - 6.5 mA                                                   |       | 5     | _     | mV    |

|      | Load stability         | Vloadld4  | lout = 0 to lomax                                                 |       | 5     | _     | mV    |

|      | Ripple removal         | RR1kld4   | Vinput = $0.2 \text{ Vpp}$ , $f = 1 \text{ kHz}$                  |       | 60    |       | dB    |

| LDO4 | ratio                  | RR10kld4  | Vvcc1 = Vvcc3 = 3.3 V, $Iout = 1 mA to Iomax$ $f = 10 kHz$        | _     | 40    |       | dB    |

|      | Output noise voltage   | Vnoiseld4 | f = 10 Hz to 100 kHz,<br>lout = 1 mA to lomax                     | _     | 30    | 40    | μVrms |

|      | Rise time              | Trld4     | Vvcc1 = Vvcc3 = 3.3 V,<br>lout = 0 mA, Vout = 90%                 |       | 130   | _     | μs    |

|      | Fall time              | Tfld4     | Vvcc1 = Vvcc3 = 3.3 V,<br>lout = 0 mA, Vout = 10%                 |       | 70    |       | μs    |

| D-        |                        | Councile of | O a malital a m                |       | Value |       | 11   |

|-----------|------------------------|-------------|--------------------------------|-------|-------|-------|------|

| Pa        | rameter                | Symbol      | Condition                      | Min   | Тур   | Max   | Unit |

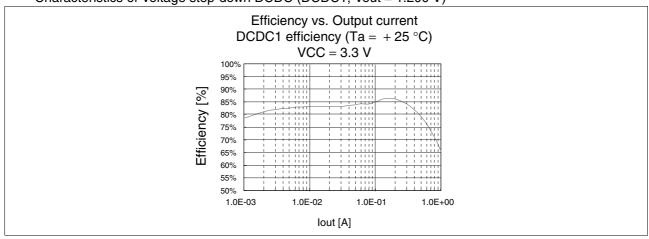

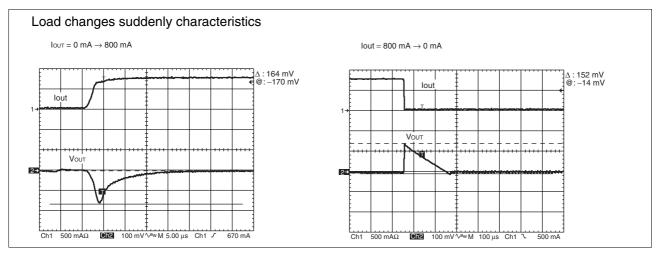

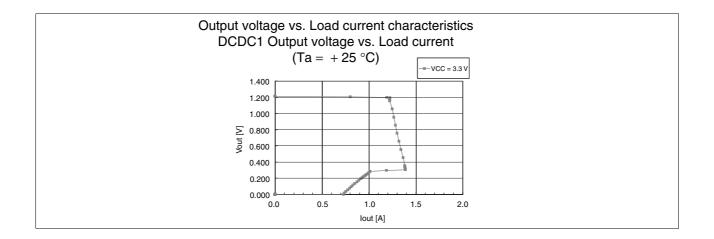

|           | Output voltage         | Voutdd1     | lout = 0 to lomax              | 1.100 | 1.200 | 1.300 | V    |

|           | Maximum output current | loutdd1     | _                              | 800   | _     | _     | mA   |

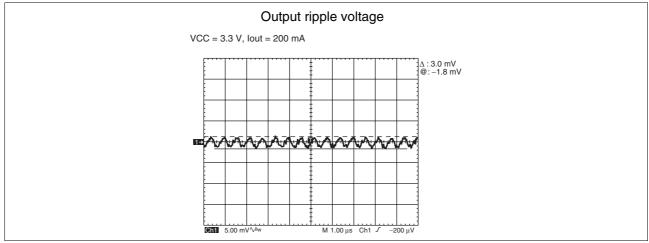

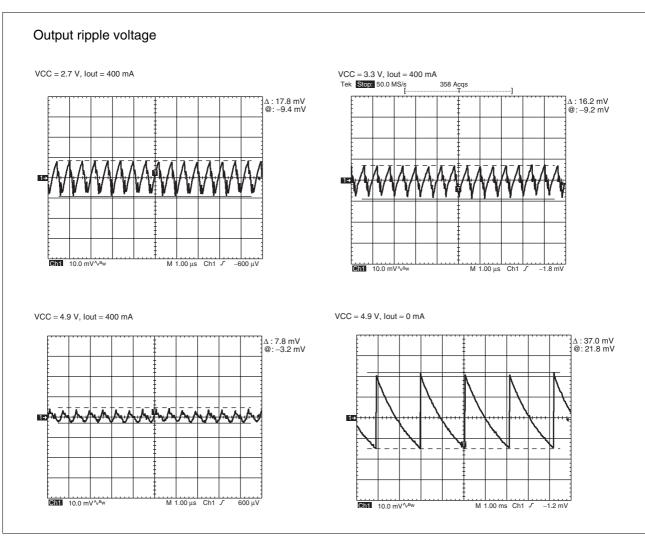

|           | Output ripple voltage  | Vrpldd11    | lout = 0 to lomax              | _     | 15    | _     | mV   |

| DC/DC1    | Input stability        | Vlinedd1    | Vvcc1 = 2.7 V to 5.5 V         |       | 10    |       | mV   |

| converter | Load stability         | Vloaddd1    | lout = - 1 mA to lomax         |       | _     | 20    | mV   |

|           | Oscillation frequency  | Fdd1        | PWM mode                       | _     | 1.7   | _     | MHz  |

|           | Efficiency             | ηdd1        | Vvcc1 = 3.3 V, lout = - 200 mA | 75    | 85    |       | %    |

|           | Rise time              | Trdd1       | Vvcc1 = 3.3 V, lout = 0 mA     |       | 50    | _     | μs   |

|           | Fall time              | Tfdd1       | Vvcc1 = 3.3 V, lout = 0 mA     |       | 200   | _     | μs   |

|           | Output voltage         | Voutdd2     | lout = 0 to lomax              | 1.750 | 1.825 | 1.900 | V    |

|           | Maximum output current | loutdd2     | _                              | 600   |       |       | mA   |

|           | Output ripple voltage  | Vrpldd21    | lout = 0 to lomax              |       | 15    |       | mV   |

| DC/DC2    | Input stability        | Vlinedd2    | Vvcc1 = 2.7 V to 5.5 V         |       | 10    | _     | mV   |

| converter | Load stability         | Vloaddd2    | lout = - 1 mA to lomax         |       | _     | 20    | mV   |

|           | Oscillation frequency  | Fdd2        | PWM mode                       |       | 1.7   |       | MHz  |

|           | efficiency             | ηdd2        | Vvcc1 = 3.3 V, lout = - 200 mA | 80    | 90    | _     | %    |

|           | Rise time              | Trdd2       | Vvcc1 = 3.3 V, lout = 0 mA     |       | 50    |       | μs   |

|           | Fall time              | Tfdd2       | Vvcc1 = 3.3 V, lout = 0 mA     | _     | 200   | _     | μs   |

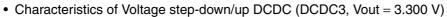

|           | Output voltage         | Voutdd3     | lout = 0 to lomax              | 3.200 | 3.300 | 3.400 | V    |

|           | Maximum output current | loutdd3     | _                              | 650   |       |       | mA   |

|           | Output ripple voltage  | Vrpldd31    | lout = 0 to lomax              | _     | 60    | _     | mV   |

| DC/DC3    | Input stability        | Vlinedd3    | Vvcc1 = 2.7 V to 5.5 V         |       | 10    |       | mV   |

| converter | Load stability         | Vloaddd3    | lout = - 1 mA to lomax         | _     | _     | 30    | mV   |

|           | Oscillation frequency  | Fdd3        | PWM mode                       | _     | 1.7   | _     | MHz  |

|           | efficiency             | ηdd3        | Vvcc1 = 3.3 V, lout = - 200 mA | 80    | 90    | _     | %    |

|           | Rise time              | Trdd3       | Vvcc1 = 3.3 V, lout = 0 mA     | _     | 100   | _     | μs   |

|           | Fall time              | Tfdd3       | Vvcc1 = 3.3 V, lout = 0 mA     |       | 120   | _     | μs   |

| (Continued)                           |                                                          |          |                                 |                 | Value |                 |                                       |

|---------------------------------------|----------------------------------------------------------|----------|---------------------------------|-----------------|-------|-----------------|---------------------------------------|

| Pai                                   | ameter                                                   | Symbol   | Condition                       | Min             | Тур   | Max             | Unit                                  |

|                                       |                                                          | 17:14    |                                 |                 | тур   | 0.3×            | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

|                                       |                                                          | Vil1     | ONOFF                           | 0.0             |       | Vvcc1           | V                                     |

|                                       | Input voltage                                            | Vih1     |                                 | 0.7 ×<br>Vvcc1  |       | Vvcc1           | V                                     |

|                                       | input voltage                                            | Vil2     | LDOCNT1, LDOCNT2                | 0.0             | _     | 0.3 ×<br>Vvcc3  | V                                     |

|                                       |                                                          | Vih2     | LDOOM11, LDOOM12                | 0.7 ×<br>Vvcc3  | _     | Vvcc3           | V                                     |

| Start/stop<br>control block           | Output                                                   | Vol1     | XRST1, XRST2, lout = 1 mA       | 0.0             |       | 0.15 ×<br>Vvcc3 | V                                     |

| Common Brook                          | voltage                                                  | Voh1     | XRST1, XRST2, lout = -1 mA      | 0.85 ×<br>Vvcc3 |       | Vvcc3           | V                                     |

|                                       | VCC1<br>power supply<br>detection voltage                | Vdetvon  | VCC1 rise = 0.1 V/10 μs         | 2.55            | 2.6   | 2.65            | V                                     |

|                                       | VCC1<br>Voltage for<br>power supply<br>cut-off detection | Vdetvoff | VCC1 fall = 0.3 V/10 μs         | 2.3             | 2.4   | 2.5             | V                                     |

|                                       | Output voltage                                           | Vol32k   | RTC_CLK, lout = 0.5 mA          |                 |       | 0.15 ×<br>Vrtc  | V                                     |

| RTC block                             |                                                          | Voh32k   | RTC_CLK, lout = - 0.5 mA        | 0.85 ×<br>Vrtc  |       | Vrtc            | V                                     |

|                                       | Internal oscillation capacitance 1                       | Cg       | OSCIN                           |                 | 10    |                 | pF                                    |

|                                       | Internal oscillation capacitance 2                       | Cd       | OSCOUT                          |                 | 10    | _               | pF                                    |

|                                       | Input voltage                                            | Vil14    | SCI_SDA (for input)             | 0.0             |       | 0.3 ×<br>Vvcc3  | V                                     |

| I <sup>2</sup> C interface            | Input voltage                                            | Vih14    | SCL, SDA (for input)            | 0.7 ×<br>Vvcc3  | _     | Vvcc3           | V                                     |

|                                       | Output voltage                                           | Vol18    | SDA (for output)<br>lout = 3 mA | 0.0             | _     | 0.4             | V                                     |

| VFIL1,                                | Output voltage                                           | Vovfil1  | VFIL1                           | 1.175           | 1.225 | 1.275           | V                                     |

| VFIL2                                 | Output voltage                                           | Vovfil2  | VFIL2                           | 0.575           | 0.60  | 0.625           | V                                     |

| LDO5                                  | Output voltage                                           | Voutld5  | lout = 0 to lomax               | 2.325           | 2.40  | 2.475           | V                                     |

| UVLO                                  | UVLO release voltage                                     | Vuvlod   | _                               | 2.1             | 2.2   | 2.3             | V                                     |

|                                       | UVLO detection voltage                                   | Vuvlor   | _                               | 2.0             | 2.1   | 2.2             | V                                     |

| Over tem-<br>perature                 | Detection temperature                                    | Totpd    | _                               | + 135           | + 150 | + 165           | °C                                    |

| protection<br>(OTP)                   | Release temperature                                      | Totpr    |                                 | + 105           | + 120 | + 135           | °C                                    |

| Output short circuit protection (SCP) | Detection protection time                                | Tshort   | Output = 0.6 V ± 0.2 V or less  | 75              | 100   | 125             | ms                                    |

### 2. AC characteristics

(Ta = -30 °C to +85 °C, Vvcc1 = 2.7 V to 5.5 V ,Vvcc3 = 3.2 V to 5.5 V, Vvcc2 = 1.75 V to 1.90 V, Vrtc = 2.35 V to 2.475 V)

|                  | Parameter                                            | Symbol   | Condition                                                                                        |              | Value  |     | Unit |

|------------------|------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------|--------------|--------|-----|------|

|                  | Parameter                                            | Symbol   | Condition                                                                                        | Min          | Тур    | Max | Unit |

| RTC block        | Clock frequency                                      | Fck      | When using RTC_CLK, and FC_12M (manufactured by Epson Toyocom Corporation) for external crystal. | _            | 32.768 | _   | kHz  |

|                  | Clock duty                                           | Rck      | When using RTC_CLK, and FC_12M (manufactured by Epson Toyocom Corporation) for external crystal. | 25           | 50     | 75  | %    |

|                  | Margin for oscillation                               | Rfm      | Rmax = 90 kΩ                                                                                     | 10 ×<br>Rmax | _      |     | kΩ   |

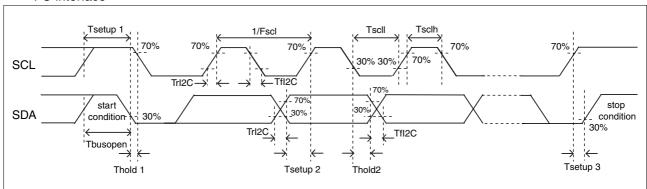

|                  | Clock frequency                                      | Fscl     | SCL                                                                                              | _            |        | 400 | kHz  |

|                  | Start condition hold time                            | Thold1   | SCL, SDA                                                                                         | 0.6          |        | _   | μs   |

|                  | SCL clock L cycle                                    | Tscll    | SCL                                                                                              | 1.3          | _      | _   | μs   |

|                  | SCL clock H cycle                                    | Tsclh    | SCL                                                                                              | 0.6          |        | _   | μs   |

|                  | Start condition set up time                          | Tsetup1  | SCL, SDA                                                                                         | 0.6          |        | _   | μs   |

| l <sup>2</sup> C | Data hold time                                       | Thold2   | SCL, SDA                                                                                         | 0            | _      | 0.9 | μs   |

| interface        | Data set up time                                     | Tsetup2  | SCL, SDA                                                                                         | 0.1          |        | _   | μs   |

|                  | Stop condition set up time                           | Tsetup3  | SCL, SDA                                                                                         | 0.6          |        | _   | μs   |

|                  | Bus open time between stop condition-start condition | Tbusopen | SDA                                                                                              | 1.3          | _      | _   | μs   |

|                  | Rise time                                            | Trl2C    | SCL, SDA                                                                                         | _            | _      | 300 | ns   |

|                  | Fall time                                            | Tfl2C    | SCL, SDA                                                                                         |              |        | 300 | ns   |

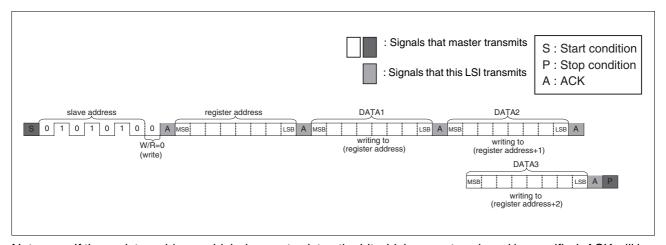

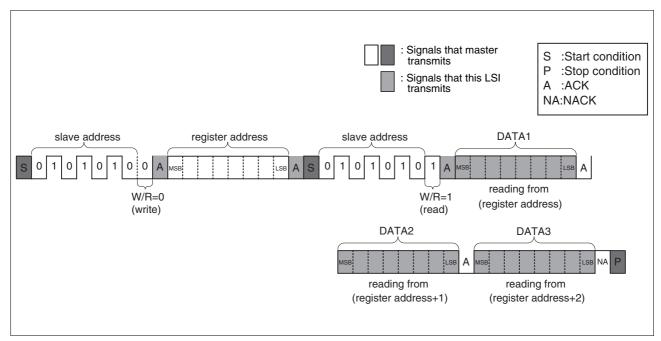

### • I2C interface

### 3. Current dissipation

| Parameter       | Condition                                                                               | Va  | Unit |      |

|-----------------|-----------------------------------------------------------------------------------------|-----|------|------|

|                 | Condition                                                                               | Тур | Max  | Oill |

| Standby current | ONOFF : L                                                                               | 150 | 250  | μΑ   |

| ON current      | DC/DC1 converter, DC/DC2 converter : ON (no load) LDO1, LDO2, LDO3, LDO4 : ON (no load) | 650 | 850  | μΑ   |

### **■ TYPICAL CHARACTERISTICS**

For the reference of design, typical characteristics are shown below.

• Characteristics of Voltage step-down DCDC (DCDC1, Vout = 1.200 V)

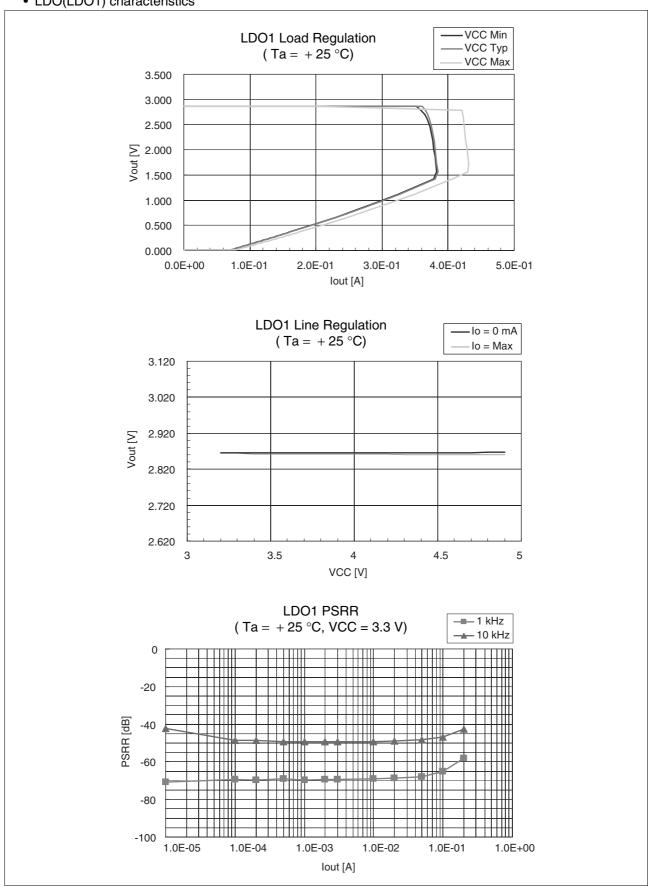

### • LDO(LDO1) characteristics

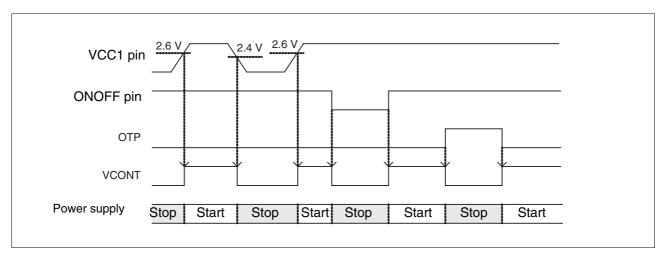

### ■ START/STOP CONTROL FUNCTION

Conditions of the VCC1 power supply pin and ONOFF, LDOCNT1 and LDOCNT2 pins and the setting of the REON register control the output of the LDO, the DC/DC converter and reset signals (XRST1 and XRST2). Also, the setting of the HRST register controls the output of the reset signal.

### 1. Conditions for start and stop

### • Conditions for start

When all conditions mentioned below are completed, the LDO and the DC/DC converter will start.

- VCC1 pin input voltage 2.6 V or more

- ONOFF pin input "H"

### • Conditions for stop

When one of conditions mentioned below occurs, the LDO and the DC/DC converter will stop.

- VCC1 pin input voltage 2.4 V or less

- ONOFF pin input "L"

- When the REON bit in the REON register changes "0" to "1"

- OTP (Over temperature protection) detection

The start and stop status in the constant voltage power supply block by the VCC1 pin input voltage and the ONOFF pin input is reflected to the VCONT bit (address 05H [0]) in the STATE register.

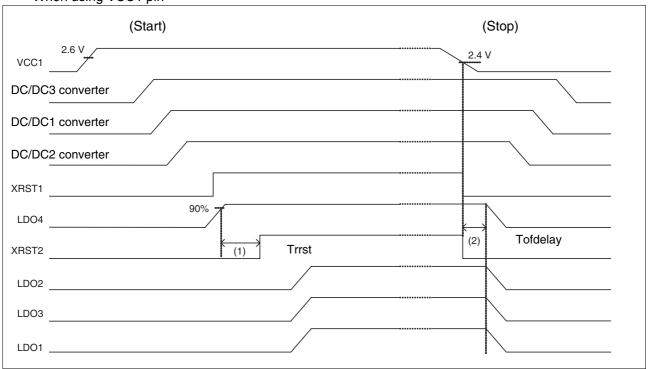

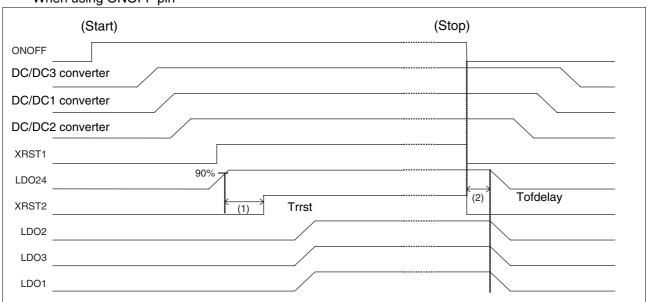

### 2. Start/stop sequence by VCC1 power supply pin and ONOFF pin

• When using VCC1 pin

• When using ONOFF pin

| Parameter | Symbol   |     |     | Unit |       |

|-----------|----------|-----|-----|------|-------|

|           | Symbol   | Min | Тур | Max  | Oille |

| (1)       | Trrst    | 4   | 5   | 6    | ms    |

| (2)       | Tofdelay | 150 | 200 | 250  | μs    |

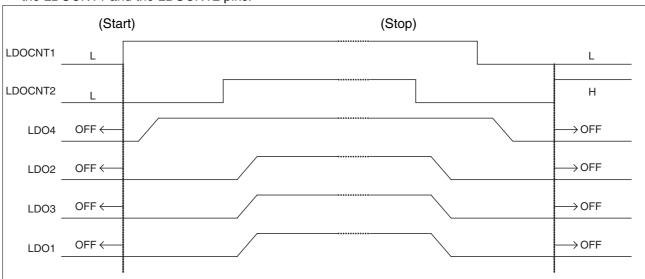

### 3. Start/stop by LDOCNT1 and LDOCNT2 pins (intermittent control)

When the XRST1 and the XRST2 pins are in "H", the LDO starts and stops depending on the conditions of the LDOCNT1 and the LDOCNT2 pins.

| Input co | ondition | L DO1 | LDO1 LDO2 |      | LDO4 |  |

|----------|----------|-------|-----------|------|------|--|

| LDOCNT1  | LDOCNT2  | LDOT  | LDO2      | LDO3 | LDO4 |  |

| Н        | Н        | ON    | ON        | ON   | ON   |  |

| Н        | L        | OFF   | OFF       | OFF  | ON   |  |

| L        | L        | OFF   | OFF       | OFF  | OFF  |  |

| L        | Н        | OFF   | OFF       | OFF  | OFF  |  |

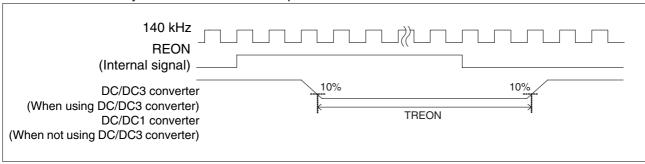

### 4. Start/stop by REON register (Restart power supply)

When "1" is written to the REON bit in the REON register (address 04<sub>H</sub> [0]), the power supply stops following the sequence and starts again after a fixed period has passed.

The STOPTIMEB bit (address 04H [5:4]) can set the time between the stop of the power supply and the restart of the power supply (calculated by the 140 kHz internal clock). The REON bit is automatically cleared after the time set by the STOPTIMEB bit has passed.

| Parameter | STOPTIMEB bit [1:0] |      | Unit |      |    |  |

|-----------|---------------------|------|------|------|----|--|

| Parameter | STOPTIMES DIL [1:0] | Min  | Тур  | Max  | J  |  |

| TREON     | 00в                 | 0.8  | 1.0  | 1.2  | ms |  |

|           | 01в                 | 3.4  | 4.0  | 5.2  | ms |  |

|           | 10в                 | 6.8  | 8.0  | 9.8  | ms |  |

|           | 11в                 | 13.6 | 16.0 | 19.0 | ms |  |

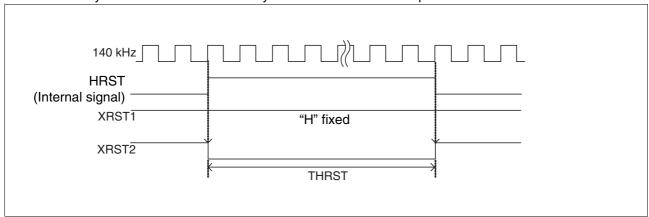

### 5. Reset control by HRST register

When "1" is written to the HRST bit in the HRST register (address 03<sub>H</sub> [0]), the output of XRST2 remains at "L" level for a fixed period.

The STOPTIMEA bit (address 03H [5:4]) can set the time for remaining on XRST2 = "L". The HRST bit is automatically cleared after the time set by the STOPTIMEA bit has passed.

| Parameter | STOPTIMEA bit |      | Unit |      |        |

|-----------|---------------|------|------|------|--------|

| Parameter | [1:0]         | Min  | Тур  | Max  | O IIII |

|           | 00в           | 0.8  | 1.0  | 1.2  | ms     |

| THRST     | 01в           | 3.4  | 4.0  | 5.2  | ms     |

| ITINOT    | 10в           | 6.8  | 8.0  | 9.8  | ms     |

|           | 11в           | 13.6 | 16.0 | 19.0 | ms     |

### ■ 32.768 kHz OUTPUT (CMOS output)

If the crystal oscillator is connected to the OSCIN and the OSCOUT pins, the  $32.768\,\mathrm{kHz}$  clock can be output from the RTC\_CLK pin.

### ■ I<sup>2</sup>C INTERFACE

This is the interface which is compliant with the I<sup>2</sup>C bus standard. The internal register data are read and write to the internal register data via two bidirectional bus lines which are the serial data line (SDA) and the serial clock line (SCL).

The MB39C316 has the following features.

- This LSI is set as slave, so the LSI cannot be set to master.

- The slave address is "2AH".

- Supports high speed mode (Max 400 kbps)

### 1. Writing flow

- (1) Detect start condition

- (2) Receive slave address ("2AH") and W/R bit ("0")

- (3) Transmit ACK

- (4) Receive register address

- (5) Transmit ACK

- (6) Receive write data

- (7) Transmit ACK

- (8) Increase the register address and then go back to (6), when a stop condition is not detected.\*

- (9) Communication stops after detecting a stop condition.

- \*: Increment stops at address FFH and keeps at FFH. The flow does not go back to 00H.

Notes: • If the register address which does not exist or the bit which are not assigned is specified, ACK will be returned, but data will not be written.

• If writing is set to the Read Only address, ACK will not be returned, but data will not be written.

### 2. Reading flow

- (1) Detect start condition

- (2) Receive slave address ("2AH") and W/R bit ("0")

- (3) Transmit ACK

- (4) Receive register address

- (5) Transmit ACK

- (6) Detect start condition

- (7) Receive slave address ("2AH") and W/R bit ("1")

- (8) Transmit ACK

- (9) Transmission of read data

- (10) Increase the register address and then go back to (9).\*

If [1] ACK is received. Release the bus if [2] NACK is received.

- (11) Communication stops after detecting a stop condition.

- \*: Increment stops at address FFH and keeps FFH. Increment does not go back to 00H.

Note: If the register address which does not exist and the bit which does not execute the bit assign are specified, read data becomes "0".

### **■ REGISTERS**

### 1. Address allocation

| Ad-            | <b>.</b>                               | Type Register name (function) W/R                   |    | Register Contents |          |                |                |          |          |          |          | Default   |

|----------------|----------------------------------------|-----------------------------------------------------|----|-------------------|----------|----------------|----------------|----------|----------|----------|----------|-----------|

| dress<br>(hex) | туре                                   |                                                     |    | D7                | D6       | D5             | D4             | D3       | D2       | D1       | D0       | value     |

| 00             | Reset                                  | SRST<br>(Soft reset control)                        | *  | RSTDET            | _        | _              | _              | _        | _        | _        | SRST     | 0000 0000 |

| 01             | Version                                | VERSION<br>(Information about<br>versions)          | R  | _                 | _        | _              | _              | VER3     | VER2     | VER1     | VER0     | 0000 0011 |

| 02             | Constant<br>voltage<br>power<br>supply | VSEL_SYN<br>(LDO<br>voltage setting)                | WR | _                 | _        | _              | _              | _        | _        | _        | VSEL_SYN | 0000 0000 |

| 03             | Reset                                  | HRST<br>(Hard reset control)                        | WR | HRDET             | _        | STOPTI<br>MEA1 | STOPTI<br>MEA0 | _        | _        | _        | HRST     | 0000 0000 |

| 04             | Power supply control                   | REON<br>(Control of<br>re-starting power<br>supply) | WR | REDET             | _        | STOPTI<br>MEB1 | STOPTI<br>MEB0 | _        | _        | _        | REON     | 0000 0000 |

| 05             | Notice of state                        | STATE<br>(Notice of state)                          | R  | _                 | _        | _              | _              | CUR_lim  | OTP      | RTC_OSC  | VCONT    | 0000 0000 |

| 06             | General                                | GP<br>(General-purpose<br>register)                 | WR | GP7               | GP6      | GP5            | GP4            | GP3      | GP2      | GP1      | GP0      | 0000 0000 |

| 07-7F          | _                                      | _                                                   | _  | _                 | _        | _              | _              | _        | _        | _        | _        | _         |

| 80-8B          | TEST                                   | reserved<br>(reserved bytes)                        |    | reserved          | reserved | reserved       | reserved       | reserved | reserved | reserved | reserved | _         |

| 8C             | _                                      |                                                     | _  |                   |          |                |                | _        |          | _        | _        |           |

<sup>\*: 00</sup>H[D0] is Write only, [D7] is Write/Read.

- Although data which "\_" is shown is accessible to read and write, writing is invalid and reading data becomes "0".

- All registers are initialized to the default value by power-on reset.

- Executing the soft reset control initializes all Write registers to the default value. There is a possibility that written data during execution of the soft reset control is not reflected correctly.

Note: Address 80H to 8BH is mapped on the registers for this LSI test. It is prohibited to write to 80H to 8BH when using this LSI.

### 2. Functional description

• Soft reset control (Address 00H)

**D7** D0 D6 D5 D4 D3 D2 D1 At Write **RSTDET SRST** At Read **RSTDET** 0 0 0 0 0 0 0 0 0 0 0 0 Default 0 0

bit [7] RSTDET: Register reset history bit

| RSTDET | Operation                                                           |

|--------|---------------------------------------------------------------------|

| 0      | No execution of soft reset control (Read)/RSTDET clear bits (Write) |

| 1      | Execution of register reset by soft reset control (Read)            |

This bit saves the execution history of the reset operation by the soft reset control. If the reset operation by the soft reset control is executed, this bit is set to "1".

When clearing this bit, write "00H" to this register.

Writing RSTDET = "1" is ignored.

bit [0] SRST: Register reset bit

| SRST | Operation                                                         |

|------|-------------------------------------------------------------------|

| 0    | Normal operation                                                  |

| 1    | Reset the Write register for other than address 00 <sub>H</sub> . |

If writing "1" to this bit, all Write registers are reset, and the read value for address 00H is "80H".

The reset state will be remained for about 15  $\mu$ s after writing SRST = "1".

This bit is for the write only and the read value is always "0".

Notes: • If RSTDET = "0" and SRST = "1" are written simultaneously, RSTDET = "0" is ignored. The reset operation by SRST = "1" is executed and the RSTDET bit is set to "1".

• There is a possibility that written data during the soft reset control execution is not written correctly.

• Information about versions (Address 01H)

|          | D7 | D6 | D5 | D4 | D3                           | D2   | D1   | D0   |

|----------|----|----|----|----|------------------------------|------|------|------|

| At Write | _  |    | _  | _  | _                            |      | _    | _    |

| At Read  | 0  | 0  | 0  | 0  | VER3                         | VER2 | VER1 | VER0 |

| Default  | 0  | 0  | 0  | 0  | Fixed value for each version |      |      | on   |

bit [3:0] VER: Version display bit

| VER  | Operation |

|------|-----------|

| 0000 | _         |

| 0001 | 1         |

| 0010 | 2         |

| 0011 | 3         |

| :    | :         |

This register reads information about device's versions.

• LDO voltage setting (Address 02н)

|          | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0       |

|----------|----|----|----|----|----|----|----|----------|

| At Write | _  | _  | _  | _  | _  |    | _  | VSEL_SYN |

| At Read  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | VSEL_SYN |

| Default  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0        |

bit [0] VSEL\_SYN: Selection bit of LDO3 voltage

| VSEL_SYN | Operation   |

|----------|-------------|

| 0        | 1.2 V (Typ) |

| 1        | 1.3 V (Typ) |

This bit switches output voltage of LDO3.

• Hard reset control (Address 03<sub>H</sub>)

|          | D7    | D6 | D5         | D4         | D3 | D2 | D1 | D0   |

|----------|-------|----|------------|------------|----|----|----|------|

| At Write | HRDET | _  | STOPTIMEA1 | STOPTIMEA0 | _  |    |    | HRST |

| At Read  | HRDET | 0  | STOPTIMEA1 | STOPTIMEA0 | 0  | 0  | 0  | HRST |

| Default  | 0     | 0  | 0          | 0          | 0  | 0  | 0  | 0    |

bit [7] HRDET: HRST history bit

| HRDET | Operation                                                          |  |  |  |  |  |

|-------|--------------------------------------------------------------------|--|--|--|--|--|

| 0     | No execution of hard reset control (Read)/HRDET clear bits (Write) |  |  |  |  |  |

| 1     | Execution of XRST2 reset by hard reset control (Read)              |  |  |  |  |  |

This bit saves the execution history of the reset operation by the hard reset control. The reset operation by the hard reset control sets this bit to "1" (same time as re-writing of the HRST bit). Write "00H" to this register when clearing this bit.

Writing HRDET = "1" is ignored.

bit [5:4] STOPTIMEA: XRST2 = "L" time setting bit

| STOPTIMEA | Operation   |

|-----------|-------------|

| 00        | 1 ms (Typ)  |

| 01        | 4 ms (Typ)  |

| 10        | 8 ms (Typ)  |

| 11        | 16 ms (Typ) |

This bit selects the time of XRST2 = "L" by the hard reset control.

bit [0] HRST : HRST Control bit

| HRST | Operation                                        |  |  |  |

|------|--------------------------------------------------|--|--|--|

| 0    | Normal operation (Read)                          |  |  |  |

| 1    | Instructions of hard reset control start (Write) |  |  |  |

When writing "1" to this bit, the output of the XRST2 pin will remain in "L" for the time set by the STOPTIMEA bit.

This bit is automatically cleared after the time set has passed.

Note: If HRDET = "0" and HRST = "1" are written at the same time, HRDET = "0" is ignored. The reset operation is executed by HRST = "1" and the HRDET bit is set to "1".

• Control of re-starting power supply (Address 04H)

| ·        | D7    | D6 | D5         | D4         | D3 | D2 | D1 | D0   |

|----------|-------|----|------------|------------|----|----|----|------|

| At Write | REDET | _  | STOPTIMEB1 | STOPTIMEB0 | _  | _  | _  | REON |

| At Read  | REDET | 0  | STOPTIMEB1 | STOPTIMEB0 | 0  | 0  | 0  | REON |

| Default  | 0     | 0  | 0          | 0          | 0  | 0  | 0  | 0    |

bit [7] REDET: REON history bit

| REDET | Operation                                                                        |

|-------|----------------------------------------------------------------------------------|

| 0     | No execution of re-starting power supply control (Read)/REDET Clear bits (Write) |

| 1     | Re-starting power supply by re-starting power supply control (Read)              |

This bit keeps the execution history of re-starting power supply by the re-starting power supply control. When re-starting power supply is executed by the re-starting power supply control, this bit is set to "1" (same time as re-writing of the REON bit).

Write "00H" to this register to clear this bit.

Writing REDET = "1" is ignored.

bit [5:4] STOPTIMEB: Time setting bit to maintain power supply stop status

| STOPTIMEB | Operation   |

|-----------|-------------|

| 00        | 1 ms (Typ)  |

| 01        | 4 ms (Typ)  |

| 10        | 8 ms (Typ)  |

| 11        | 16 ms (Typ) |

This bit selects the time between completion of the stop sequence and the beginning of the re-start.

bit [0] REON: REON Control bit

| REON | Operation                                     |  |  |

|------|-----------------------------------------------|--|--|

| 0    | Normal operation (Read)                       |  |  |

| 1    | Instructions to re-start power supply (Write) |  |  |

Writing "1" to this bit turns power supply on again (Stop  $\rightarrow$  Start the constant voltage power supply). The power supply start sequence starts when the time set by the STOPTIMEB bit passes after the power supply stop sequence has completed.

This bit is automatically cleared after the time set has passed.

Note: If REDET = "0" and REON = "1" are written at the same time, REDET = "0" is ignored. Re-starting power supply by REON = "1" is executed, and the REDET bit is set to "1".

• Notice of power supply state (Address 05H)

|          | D7 | D6 | D5 | D4 | D3      | D2  | D1      | D0    |

|----------|----|----|----|----|---------|-----|---------|-------|

| At Write | _  | _  |    | _  | _       | _   |         | _     |

| At Read  | 0  | 0  | 0  | 0  | CUR_lim | OTP | RTC_OSC | VCONT |

| Default  | 0  | 0  | 0  | 0  | 0       | 0   | 0       | 0     |

bit [3] CUR\_lim : Display bit to detect short circuit

| CUR_lim | Operation                     |

|---------|-------------------------------|

| 0       | Detection of no short circuit |

| 1       | Detection of short circuit    |

This bit reads detection signals of short circuit.

bit [2] OTP : OTP status display bit

| OTP | Operation                        |  |  |  |

|-----|----------------------------------|--|--|--|

| 0   | No problem with over temperature |  |  |  |

| 1   | Problem with over temperature    |  |  |  |

This bit reads the abnormal over temperature signal.

bit [1] RTC\_OSC: RTC oscillation status display bit

| RTC_OSC | Operation          |

|---------|--------------------|

| 0       | Oscillation stop   |

| 1       | Normal oscillation |

This bit reads the oscillation status of the RTC clock.

bit [0] VCONT : VCONT Status display bit

| VCONT | Operation                       |  |  |  |  |

|-------|---------------------------------|--|--|--|--|

| 0     | VCONT = L (power supply stops)  |  |  |  |  |

| 1     | VCONT = H (power supply starts) |  |  |  |  |

This bit reads the VCONT status.

• General-purpose register (Address 06н)

|          | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

|----------|-----|-----|-----|-----|-----|-----|-----|-----|

| At Write | GP7 | GP6 | GP5 | GP4 | GP3 | GP2 | GP1 | GP0 |

| At Read  | GP7 | GP6 | GP5 | GP4 | GP3 | GP2 | GP1 | GP0 |

| Default  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

bit [7:0] GP: general-purpose register

This register is the general-purpose register which can be used by users freely. It is possible to read and write to "0/1".

This register is reset to the default value by the soft reset control and power-on reset.

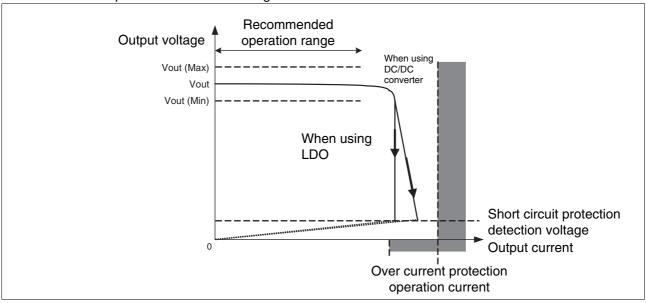

### **■ PROTECTION FUNCTIONS**

### 1. Over current protection (OCP)

This function controls the current value of the LDO and the DC/DC converter in the over load condition. When the output current excessively increases, the output voltage drops dramatically so as not to exceed the current of the over current protection operation.

The output of the LDO and the DC/DC converter stops when the output voltage drops dramatically below the short circuit protection detection voltage.

### 2. Output Short Circuit Protection (SCP)

If either of the LDO and the DC/DC converter output short circuit (GND short circuit) continues for 100 ms (Typ), all output of the LDO and the DC/DC converter except LDO5 stop. The output short circuit protection is released by power-on reset, and each output of the LDO and the DC/DC converter is restarted following the start sequence when the VCC1 pin exceeds 2.6 V (Typ).

### 3. Under Voltage Lock Out (UVLO)

When the VCC1 pin becomes less than 2.1 V (Typ), the inside of LSI is reset by the UVLO protection (power-on reset). The UVLO is released when the VCC1 pin becomes more than 2.2 V (Typ).

### 4. Over temperature protection (OTP)

If the chip temperature exceeds +150 °C (Typ), all output of the LDO and the DC/DC converter except for the LDO5 stop. If the chip temperature drops below +120 °C (Typ), OTP is released and each output of the LDO and the DC/DC converter is automatically restarted.

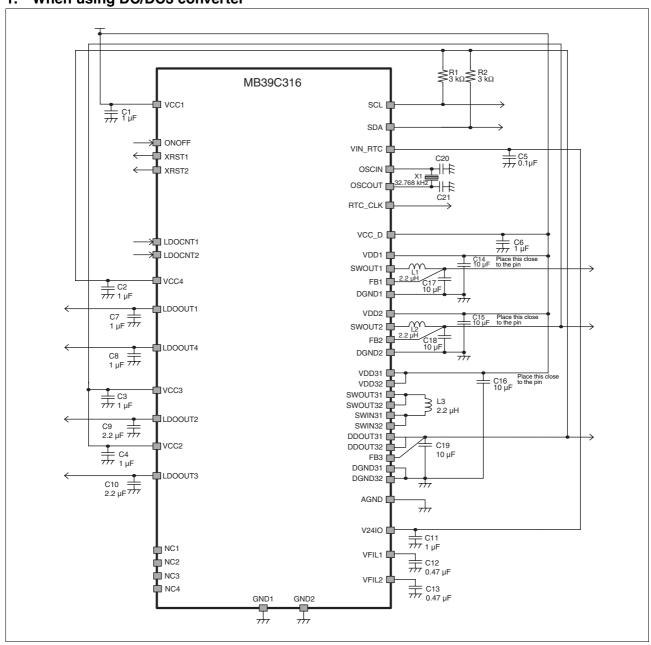

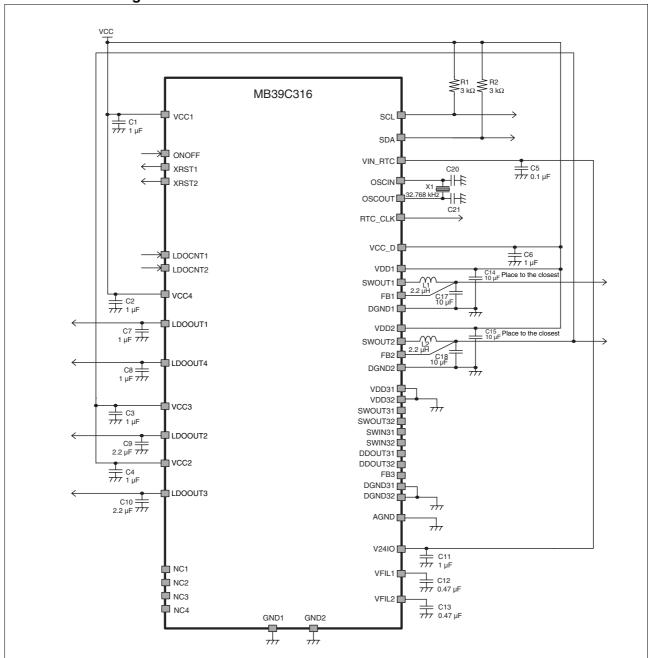

### **■ TYPICAL APPLICATION CIRCUIT**

### 1. When using DC/DC3 converter

### 2. When not using DC/DC3 converter

### **■ PART LIST**

| Circuit symbol | Part characteristic           | Package       | Application                       | Recommended part       |

|----------------|-------------------------------|---------------|-----------------------------------|------------------------|

| C1             | 1 μF                          | Ceramic       | Power supply input                | _                      |

| C2             | 1 μF                          | Ceramic       | Power supply input                | _                      |

| C3             | 1 μF                          | Ceramic       | Power supply input                | _                      |

| C4             | 1 μF                          | Ceramic       | Power supply input                | _                      |

| C5             | 0.1 μF                        | Ceramic       | Power supply input                | _                      |

| C6             | 1 μF                          | Ceramic       | Power supply input                | _                      |

| C7             | 1.0 μF (6.3 V, ± 10%)         | Ceramic       | LDO1 output capacitor             | GRM155B30J105K(murata) |

| C8             | 1.0 μF (6.3 V, ± 10%)         | Ceramic       | LDO4 output capacitor             | GRM155B30J105K(murata) |

| C9             | 2.2 μF (4.0 V, ± 20%)         | Ceramic       | LDO2 output capacitor             | GRM155B30G225M(murata) |

| C10            | 2.2 μF (4.0 V, ± 20%)         | Ceramic       | LDO3 output capacitor             | GRM155B30G225M(murata) |

| C11            | 1.0 μF (6.3 V, ± 10%)         | Ceramic       | LDO5 output capacitor             | GRM155B30J105K(murata) |

| C12            | $0.47~\mu F~(6.3~V,\pm 10\%)$ | Ceramic       | VFIL1 output capacitor            | GRM155B30J474K(murata) |

| C13            | $0.47~\mu F~(6.3~V,\pm~10\%)$ | Ceramic       | VFIL2 output capacitor            | GRM155B30J474K(murata) |

| C14            | 10 μF (6.3 V, ± 20%)          | Ceramic       | DC/DC1 converter input capacitor  | GRM188B30J106M(murata) |

| C15            | 10 μF (6.3 V, ± 20%)          | Ceramic       | DC/DC2 converter input capacitor  | GRM188B30J106M(murata) |

| C16            | 10 $\mu$ F (6.3 V, $\pm$ 20%) | Ceramic       | DC/DC3 converter input capacitor  | GRM188B30J106M(murata) |

| C17            | 10 $\mu$ F (6.3 V, $\pm$ 20%) | Ceramic       | DC/DC1 converter output capacitor | GRM188B30J106M(murata) |

| C18            | 10 μF (6.3 V, ± 20%)          | Ceramic       | DC/DC2 converter output capacitor | GRM188B30J106M(murata) |

| C19            | 10 μF (6.3 V, ± 20%)          | Ceramic       | DC/DC3 converter output capacitor | GRM188B30J106M(murata) |

| C20            | _                             | _             | RTC block frequency adjustment    | _                      |

| C21            | _                             | _             | RTC block frequency adjustment    |                        |

| L1             | 2.2 μΗ                        | Multi layered | DC/DC1 converter<br>Coil          | MIPSTZ2012D2R2(FDK)    |

| L2             | 2.2 μΗ                        | Multi layered | DC/DC2 converter<br>Coil          | MIPSTZ2012D2R2(FDK)    |

| L3             | 2.2 μΗ                        | Multi layered | DC/DC3 converter<br>Coil          | MIPSAZ3225D2R2(FDK)    |

| R1             | 3 kΩ                          |               | SCL pull-up resistor              | _                      |

| R2             | 3 kΩ                          |               | SDA pull-up resistor              | _                      |

| X1             | 32.768 kHz                    |               | <u> </u>                          | FC-12M(Epson Toyocom)  |

FDK : FDK Corporation

Epson Toyocom : Epson Toyocom Corporation murata : Murata Manufacturing Co., Ltd.

### 1. External parts for DC/DC converter

- 1. A capacitor (10  $\mu$ F) between the DC/DC converter power supply and GND pins needs to be connected at the closest place to both pins.

- 2. A coil needs to be selected with consideration for the frequency characteristics of inductance and DC bias characteristics.

### 1. External parts for DC/DC converter

- 1. A capacitor (10  $\mu$ F) between the DC/DC converter power supply and GND pins needs to be connected at the closest place to both pins.

- 2. A coil needs to be selected with consideration for the frequency characteristics of inductance and DC bias characteristics.

- 3. A capacitor needs to be selected with consideration for the DC bias characteristic of its capacitance.

### 2. External parts for LDO

- 1. A capacitor between the LOD output and GND pins needs to be connected at the closest place to both pins.

- 2. A capacitor needs to be selected with consideration for the DC bias and AC characteristics of its capacitance.

### **■ USAGE PRECAUTION**

### 1. Do not configure the IC over the maximum ratings.

If the IC is used over the maximum ratings, the LSI may be permanently damaged. It is preferable for the device to normally operate within the recommended usage conditions. Usage outside of these conditions can have an adverse effect on the reliability of the LSI.

### 2. Use the device within the recommended operating conditions.

The recommended values guarantee the normal LSI operation under the recommended operating conditions. The electrical ratings are guaranteed when the device is used within the recommended operating conditions and under the conditions stated for each item.

# 3. Printed circuit board ground lines should be set up with consideration for common impedance.

### 4. Take appropriate measures against static electricity.

- Containers for semiconductor materials should have anti-static protection or be made of conductive material.

- After mounting, printed circuit boards should be stored and shipped in conductive bags or containers.

- Work platforms, tools, and instruments should be properly grounded.

- Working personnel should be grounded with resistance of 250 k $\Omega$  to 1 M $\Omega$  in serial body and ground.

### 5. Do not apply negative voltages.

The use of negative voltages below – 0.3 V may make the parasitic transistor activated to the LSI, and can cause malfunctions.

### **■ ORDERING INFORMATION**

| Part number       | Package                     | Remarks           |

|-------------------|-----------------------------|-------------------|

| MB39C316PW-G-ERE1 | WL-CSP pin<br>(WLP-49P-M01) | Lead free version |

### **■ EV BOARD ORDERING INFORMATION**

| EV board number | EV board version No. | Remarks |

|-----------------|----------------------|---------|

| MB39C316EVB     | 1.0                  |         |

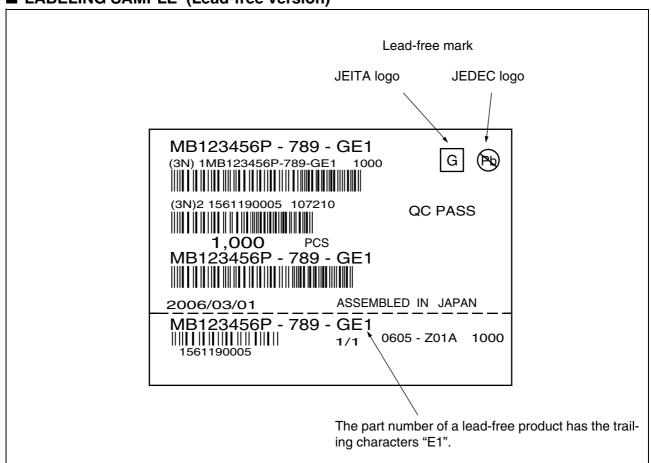

### ■ Rohs Compliance information of Lead (Pb) free version

The LSI products of Fujitsu Microelectronics with "E1" are compliant with RoHS Directive, and has observed the standard of lead, cadmium, mercury, Hexavalent chromium, polybrominated biphenyls (PBB), and polybrominated diphenyl ethers (PBDE). A product whose part number has trailing characters "E1" is RoHS compliant.

### ■ LABELING SAMPLE (Lead-free version)

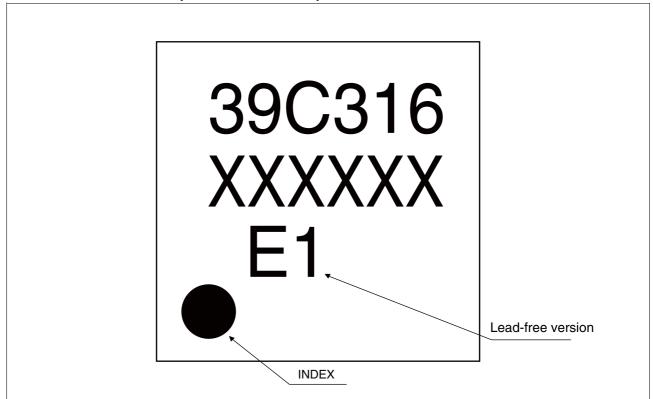

**■ MARKING FORMAT (Lead-free version)**

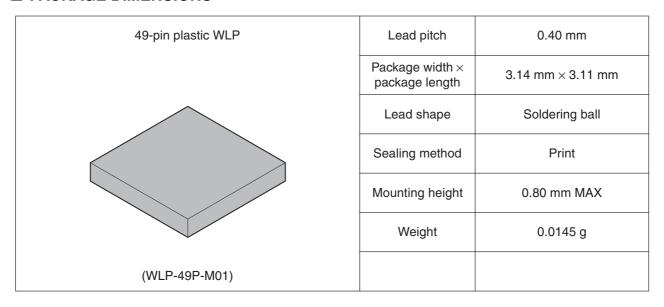

### **■ PACKAGE DIMENSIONS**

Please confirm the latest Package dimension by following URL. http://edevice.fujitsu.com/package/en-search/

### **■** CONTENTS

|                                                         | page |

|---------------------------------------------------------|------|

| - DESCRIPTION                                           | 1    |

| - FEATURES                                              | 1    |

| - APPLICATIONS                                          | 1    |

| - PIN ASSIGNMENT                                        | 2    |

| - PIN DISCRIPTIONS                                      | 3    |

| - BLOCK DIAGRAM                                         | 5    |

| - ABSOLUTE MAXIMUM RATINGS                              | 6    |

| - RECOMMENDED OPERATION CONDITIONS                      | 6    |

| - ELECTRICAL CHARACTERISTICS                            |      |

| - TYPICAL CHARACTERISTICS                               | 12   |

| - START/STOP CONTROL FUNCTION                           | 16   |

| - 32.768 kHz OUTPUT (CMOS output)                       | 19   |

| - I2C INTERFACE                                         | 20   |

| - REGISTERS                                             |      |

| - PROTECTION FUNCTIONS                                  | 27   |

| - TYPICAL APPLICATION CIRCUIT                           | 28   |

| - PART LIST                                             | 30   |

| - USAGE PRECAUTION                                      |      |

| - ORDERING INFORMATION                                  | 32   |

| - EV BOARD ORDERING INFORMATION                         | 32   |

| - RoHS COMPLIANCE INFORMATION OF LEAD (Pb) FREE VERSION | 32   |

| - LABELING SAMPLE (Lead-free version)                   | 33   |

| - MARKING FORMAT (Lead-free version)                    | 34   |

| - PACKAGE DIMENSIONS                                    | 35   |

### FUJITSU MICROELECTRONICS LIMITED

Shinjuku Dai-Ichi Seimei Bldg., 7-1, Nishishinjuku 2-chome, Shinjuku-ku, Tokyo 163-0722, Japan

Tel: +81-3-5322-3347 Fax: +81-3-5322-3387

http://jp.fujitsu.com/fml/en/

For further information please contact:

#### North and South America

FUJITSU MICROELECTRONICS AMERICA, INC. 1250 E. Arques Avenue, M/S 333

Sunnyvale, CA 94085-5401, U.S.A.

Tel: +1-408-737-5600 Fax: +1-408-737-5999

http://www.fma.fujitsu.com/

#### **Europe**

FUJITSU MICROELECTRONICS EUROPE GmbH Pittlerstrasse 47, 63225 Langen, Germany Tel: +49-6103-690-0 Fax: +49-6103-690-122 http://emea.fujitsu.com/microelectronics/

#### Korea

FUJITSU MICROELECTRONICS KOREA LTD. 206 Kosmo Tower Building, 1002 Daechi-Dong, Gangnam-Gu, Seoul 135-280, Republic of Korea Tel: +82-2-3484-7100 Fax: +82-2-3484-7111 http://kr.fujitsu.com/fmk/

#### **Asia Pacific**

FUJITSU MICROELECTRONICS ASIA PTE. LTD. 151 Lorong Chuan, #05-08 New Tech Park 556741 Singapore Tel: +65-6281-0770 Fax: +65-6281-0220 http://www.fmal.fujitsu.com/

FUJITSU MICROELECTRONICS SHANGHAI CO., LTD. Rm. 3102, Bund Center, No.222 Yan An Road (E), Shanghai 200002, China

Tel: +86-21-6146-3688 Fax: +86-21-6335-1605

http://cn.fujitsu.com/fmc/

FUJITSU MICROELECTRONICS PACIFIC ASIA LTD. 10/F., World Commerce Centre, 11 Canton Road, Tsimshatsui, Kowloon, Hong Kong

Tel: +852-2377-0226 Fax: +852-2376-3269

http://cn.fujitsu.com/fmc/en/

Specifications are subject to change without notice. For further information please contact each office.

### All Rights Reserved.

The contents of this document are subject to change without notice.

Customers are advised to consult with sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of FUJITSU MICROELECTRONICS device; FUJITSU MICROELECTRONICS does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information. FUJITSU MICROELECTRONICS assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU MICROELECTRONICS or any third party or does FUJITSU MICROELECTRONICS warrant non-infringement of any third-party's intellectual property right or other right by using such information. FUJITSU MICROELECTRONICS assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that FUJITSU MICROELECTRONICS will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of overcurrent levels and other abnormal operating conditions.

Exportation/release of any products described in this document may require necessary procedures in accordance with the regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.

The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

Edited: Sales Promotion Department