## AKM

# $\begin{array}{c} \textbf{AK5366} \\ \textbf{24-Bit 48kHz} \ \Delta \Sigma \ \textbf{ADC} \ \textbf{with Selector/PGA/ALC} \end{array}$

## GENERAL DESCRIPTION

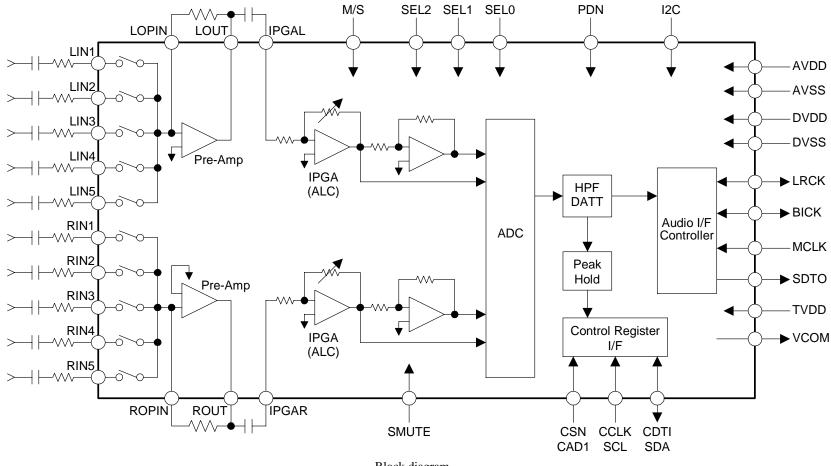

AK5366 is a high-performance 24-bit, 48kHz sampling ADC for consumer audio and digital recording applications. Thanks to AKM's Enhanced Dual-Bit modulator architecture, this analog-to-digital converter has an impressive dynamic range of 103dB with a high level of integration. The AK5366 has a 5-channel stereo input selector, an input Programmable Gain Amplifier with an ALC function. All this integration with high-performance makes the AK5366 well suited for CD and DVD recording systems.

## FEATURES

- 1. 24bit Stereo ADC

- 5ch Stereo Inputs Selector

- Input PGA from +18dB to 0dB, 0.5dB Step

- Peak Hold Function

- Auto Level Control (ALC) Circuit

- Digital HPF for offset cancellation (fc=1.0Hz@fs=48kHz)

- Digital Attenuator from +8dB to -63dB, Mute

- Soft Mute

- Single-end Inputs

- S/(N+D) : 94dB

- DR, S/N : 103dB

- Audio I/F Format : 24bit MSB justified, I<sup>2</sup>S

- 2. 3-wire Serial µP Interface / I<sup>2</sup>C-Bus

- 3. Master / Slave Mode

- 4. Master Clock : 256fs/384fs/512fs

- 5. Sampling Rate : 32kHz to 48kHz

- 6. Power Supply

- AVDD: 4.75 ~ 5.25V (typ. 5.0V)

- DVDD: 3.0 ~ 5.25V (typ. 3.3V)

- TVDD: 3.0 ~ 5.25V for input tolerant (typ. 5.0V)

- 7. Ta = −40 ~ 85°C

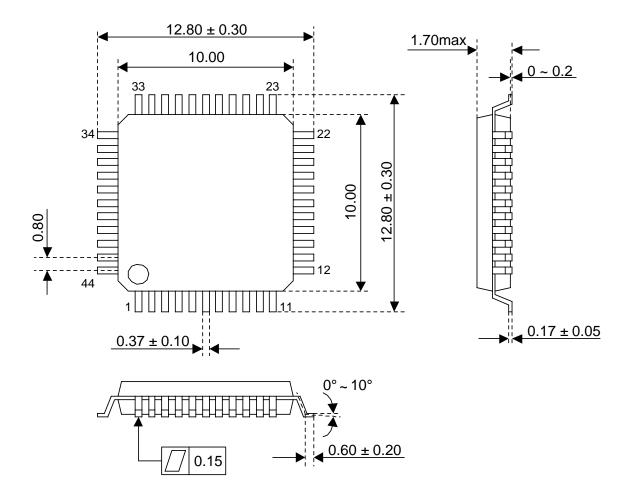

- 8. Package : 44pin LQFP

- 9. AK5365 Semi-Pin Compatible

#### ASAHI KASEI

#### Block Diagram

Block diagram

[AK5366]

#### Ordering Guide

| AK5366VQ | $-40 \sim +85^{\circ}C$     | 44pin LQFP (0.8mm pitch) |

|----------|-----------------------------|--------------------------|

| AKD5366  | Evaluation Board for AK5366 |                          |

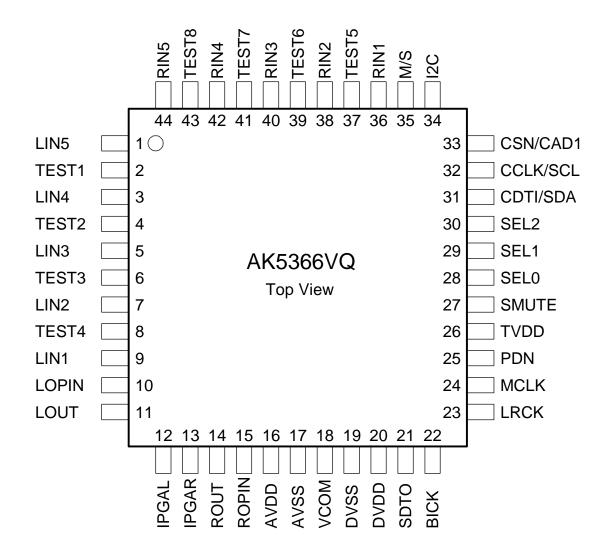

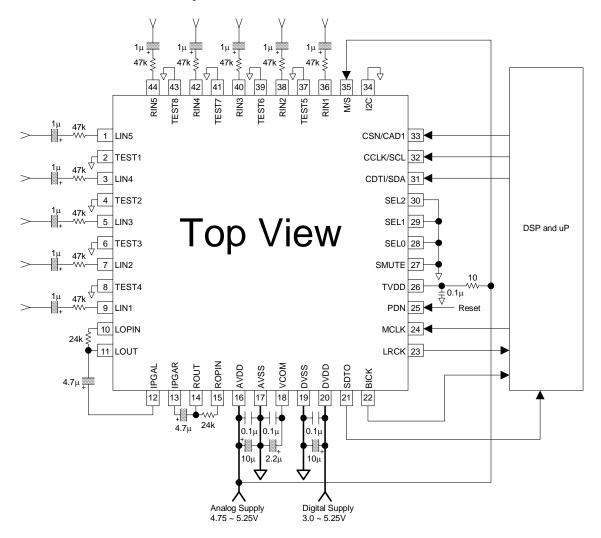

#### Pin Layout

## ■ Compatibility with AK5365

|                          | AK5365              | AK5366                |

|--------------------------|---------------------|-----------------------|

| Pin 26                   | ALC                 | TVDD                  |

| Pin 34                   | CTRL                | I2C                   |

| fs                       | max. 96kHz          | max. 48kHz            |

| ALC bit default value    | "0": ALC=OFF        | "1": ALC=ON           |

| REF7-0 bit default value | "89H": +4.5dB       | "8EH": +7.0dB         |

| IPGA Gain                | $0dB \sim +12dB$    | $0dB \sim +18dB$      |

| DATT Volume              | $-72$ dB $\sim$ 0dB | $-63$ dB $\sim +8$ dB |

| MCLK AC Coupling Input   | No                  | Yes                   |

| Peak Hold Circuit        | No                  | Yes                   |

| I2C Speed                | 100kHz              | 400kHz                |

| 5V tolerant              | No                  | Yes                   |

## (1) Pin Compatibility

|        | AK5365 | AK5366 |

|--------|--------|--------|

| Pin 26 | ALC    | TVDD   |

| Pin 34 | CTRL   | I2C    |

#### (2) Software Compatibility

| Addr | Register Name              | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

|------|----------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 00H  | Power Down & Reset Control | 0     | 0     | 0     | 0     | 0     | MCKPD | MCKAC | PWN   |

| 01H  | Input Selector Control     | 0     | 0     | 0     | 0     | 0     | SEL2  | SEL1  | SEL0  |

| 02H  | Clock & Format Control     | 0     | 0     | 0     | 0     | DIF   | CKS1  | CKS0  | SMUTE |

| 03H  | Timer Select               | 0     | 0     | LTM1  | LTM0  | ZTM1  | ZTM0  | WTM1  | WTM0  |

| 04H  | Lch IPGA Control           | IPGL7 | IPGL6 | IPGL5 | IPGL4 | IPGL3 | IPGL2 | IPGL1 | IPGL0 |

| 05H  | Rch IPGA Control           | IPGR7 | IPGR6 | IPGR5 | IPGR4 | IPGR3 | IPGR2 | IPGR1 | IPGR0 |

| 06H  | ALC Mode Control 1         | 0     | 0     | ZELMN | ALC   | FR    | LMTH  | RATT  | LMAT  |

| 07H  | ALC Mode Control 2         | REF7  | REF6  | REF5  | REF4  | REF3  | REF2  | REF1  | REF0  |

| 08H  | Lch DATT Control           | ATTL7 | ATTL6 | ATTL5 | ATTL7 | ATTL7 | ATTL7 | ATTL7 | ATTL0 |

| 09H  | Rch DATT Control           | ATTR7 | ATTR6 | ATTR5 | ATTR4 | ATTR3 | ATTR2 | ATTR1 | ATTR0 |

| 0AH  | Lch Peak Hold Low Byte     | PHL7  | PHL6  | PHL5  | PHL4  | PHL3  | PHL2  | PHL1  | PHL0  |

| 0BH  | Lch Peak Hold High Byte    | PHL15 | PHL14 | PHL13 | PHL12 | PHL11 | PHL10 | PHL9  | PHL8  |

| 0CH  | Rch Peak Hold Low Byte     | PHR7  | PHR6  | PHR5  | PHR4  | PHR3  | PHR2  | PHR1  | PHR0  |

| 0DH  | Rch Peak Hold High Byte    | PHR15 | PHR14 | PHR13 | PHR12 | PHR11 | PHR10 | PHR9  | PHR8  |

: Changing points from AK5365's register.

| No. | Pin Name | I/O | Function                                                        |

|-----|----------|-----|-----------------------------------------------------------------|

| 1   | LIN5     | Ι   | Lch Analog Input 5 Pin                                          |

| 2   | TEST1    | Ι   | Test 1 Pin<br>This pin should be connected to AVSS.             |

| 3   | LIN4     | Ι   | Lch Analog Input 4 Pin                                          |

| 4   | TEST2    | Ι   | Test 2 Pin<br>This pin should be connected to AVSS.             |

| 5   | LIN3     | Ι   | Lch Analog Input 3 Pin                                          |

| 6   | TEST3    | Ι   | Test 3 Pin<br>This pin should be connected to AVSS.             |

| 7   | LIN2     | Ι   | Lch Analog Input 2 Pin                                          |

| 8   | TEST4    | Ι   | Test 4 Pin<br>This pin should be connected to AVSS.             |

| 9   | LIN1     | Ι   | Lch Analog Input 1 Pin                                          |

| 10  | LOPIN    | Ι   | Lch Feedback Resistor Input Pin                                 |

| 11  | LOUT     | 0   | Lch Feedback Resistor Output Pin                                |

| 12  | IPGAL    | Ι   | Lch IPGA Input Pin                                              |

| 13  | IPGAR    | Ι   | Rch IPGA Input Pin                                              |

| 14  | ROUT     | 0   | Rch Feedback Resistor Output Pin                                |

| 15  | ROPIN    | Ι   | Rch Feedback Resistor Input Pin                                 |

| 16  | AVDD     | -   | Analog Power Supply Pin, 4.75 ~ 5.25V                           |

| 17  | AVSS     | -   | Analog Ground Pin                                               |

| 18  | VCOM     | 0   | Common Voltage Output Pin, AVDD/2<br>Bias voltage of ADC input. |

| 19  | DVSS     | -   | Digital Ground Pin                                              |

| 20  | DVDD     | -   | Digital Power Supply Pin, 3.0 ~ 5.25V                           |

| 21  | SDTO     | 0   | Audio Serial Data Output Pin                                    |

| 22  | BICK     | I/O | Audio Serial Data Clock Pin                                     |

## **PIN/FUNCTION**

Note: All digital input pins except pull-down pins should not be left floating. Note: TEST1, TEST2, TEST3 and TEST4 pins should be connected to AVSS.

| No. | Pin Name | I/O | Function                                                                                         |  |  |  |  |  |

|-----|----------|-----|--------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 23  | LRCK     | I/O | Output Channel Clock Pin                                                                         |  |  |  |  |  |

| 24  | MCLK     | Ι   | Master Clock Input Pin                                                                           |  |  |  |  |  |

| 25  | PDN      | Ι   | ower-Down Mode Pin<br>"H": Power up, "L": Power down reset and initializes the control register. |  |  |  |  |  |

| 26  | TVDD     | -   | Input Buffer Power Supply Pin, 3.0 ~ 5.25V                                                       |  |  |  |  |  |

| 27  | SMUTE    | Ι   | Soft Mute Pin(Internal Pull-down Pin, typ. 100kΩ)"H" : Soft Mute, "L" : Normal Operation         |  |  |  |  |  |

| 28  | SEL0     | Ι   | Input Selector 0 Pin                                                                             |  |  |  |  |  |

| 29  | SEL1     | Ι   | Input Selector 1 Pin                                                                             |  |  |  |  |  |

| 30  | SEL2     | Ι   | Input Selector 2 Pin                                                                             |  |  |  |  |  |

| 31  | CDTI     | Ι   | Control Data Input Pin in 3-wire Control (I2C pin = "L")                                         |  |  |  |  |  |

| 51  | SDA      | I/O | Control Data Input / Output Pin in $I^2C$ Control (I2C pin = "H")                                |  |  |  |  |  |

| 32  | CCLK     | Ι   | Control Data Clock Pin in 3-wire Control (I2C pin = "L")                                         |  |  |  |  |  |

| 52  | SCL      | Ι   | Control Data Clock Pin in $I^2C$ Control (I2C pin = "H")                                         |  |  |  |  |  |

| 33  | CSN      | Ι   | Chip Select Pin in 3-wire Control (I2C pin = "L")                                                |  |  |  |  |  |

| 55  | CAD1     | Ι   | Chip Address 1 Select Pin in $I^2C$ Control (I2C pin = "H")                                      |  |  |  |  |  |

| 34  | I2C      | Ι   | Control Mode Pin<br>"H" : I <sup>2</sup> C Control, "L" : 3-wire Control                         |  |  |  |  |  |

| 35  | M/S      | Ι   | Master / Slave Mode Pin<br>"H" : Master Mode, "L" : Slave Mode                                   |  |  |  |  |  |

| 36  | RIN1     | Ι   | Rch Analog Input 1 Pin                                                                           |  |  |  |  |  |

| 37  | TEST5    | Ι   | Test 5 Pin<br>This pin should be connected to AVSS.                                              |  |  |  |  |  |

| 38  | RIN2     | Ι   | Rch Analog Input 2 Pin                                                                           |  |  |  |  |  |

| 39  | TEST6    | Ι   | Test 6 Pin<br>This pin should be connected to AVSS.                                              |  |  |  |  |  |

| 40  | RIN3     | Ι   | Rch Analog Input 3 Pin                                                                           |  |  |  |  |  |

| 41  | TEST7    | Ι   | Test 7 Pin<br>This pin should be connected to AVSS.                                              |  |  |  |  |  |

| 42  | RIN4     | Ι   | Rch Analog Input 4 Pin                                                                           |  |  |  |  |  |

| 43  | TEST8    | Ι   | Test 8 Pin<br>This pin should be connected to AVSS.                                              |  |  |  |  |  |

| 44  | RIN5     | Ι   | Rch Analog Input 5 Pin                                                                           |  |  |  |  |  |

Note: All digital input pins except pull-down pins should not be left floating. Note: TEST5, TEST6, TEST7 and TEST8 pins should be connected to AVSS.

## Handling of Unused Pin

The unused input pins should be processed appropriately as below.

| Classification | Pin Name   | Setting                                                        |  |

|----------------|------------|----------------------------------------------------------------|--|

|                | LIN1-5     |                                                                |  |

|                | RIN1-5     | These pine should be open                                      |  |

| Analog         | IPGAL      | These pins should be open.                                     |  |

| Analog         | IPGAR      |                                                                |  |

|                | LOPIN/LOUT | Connected $10k\Omega$ resistor between LOPIN pin and LOUT pin. |  |

|                | ROPIN/ROUT | Connected $10k\Omega$ resistor between ROPIN pin and ROUT pin. |  |

|                | SMUTE      |                                                                |  |

|                | SEL2-0     |                                                                |  |

| Digital        | CSN        | These pine should be connected to DVSS                         |  |

| Digital        | CCLK/SCL   | These pins should be connected to DVSS.                        |  |

|                | CDTI/SDA   |                                                                |  |

|                | I2C        |                                                                |  |

|                                                                                         | ABSOLU                         | JTE MAXIMUM | RATINGS      |          |          |       |

|-----------------------------------------------------------------------------------------|--------------------------------|-------------|--------------|----------|----------|-------|

| (AVSS, DVSS=0V;                                                                         | Note 1                         |             |              |          |          |       |

| Parameter                                                                               |                                |             | Symbol       | min      | max      | Units |

| Power Supplies:                                                                         | Analog                         |             | AVDD         | -0.3     | 6.0      | V     |

|                                                                                         | Digital                        |             | DVDD         | -0.3     | 6.0      | V     |

|                                                                                         | Input Buffer                   | (Note 2)    | TVDD         | -0.3     | 6.0      | V     |

|                                                                                         | AVSS – DVSS                    | (Note 3)    | $\Delta GND$ | -        | 0.3      | V     |

| Input Current, Any I                                                                    | Pin Except Supplies            |             | IIN          | -        | ±10      | mA    |

| Analog Input Voltage (Note 4)<br>(LIN1-5, RIN1-5, LOPIN, ROPIN, IPGAL, IPGAR, M/S pins) |                                | VINA        | -0.3         | AVDD+0.3 | v        |       |

| Digital Input Voltag<br>(MCLK, BICK, LRC                                                |                                |             | VIND1        | -0.3     | DVDD+0.3 | V     |

| Digital Input Voltag<br>(SMUTE, SEL2-0, C<br>I2C pins)                                  | e 2<br>CSN/CAD1, CCLK/SCL, CD' | TI/SDA,     | VIND2        | -0.3     | TVDD+0.3 | V     |

| Ambient Temperature (Powered applied)                                                   |                                |             | Та           | -40      | 85       | °C    |

| Storage Temperature                                                                     | 2                              |             | Tstg         | -65      | 150      | °C    |

Note 1. All voltages with respect to ground.

Note 2. SMUTE, SEL2-0, CSN/CAD1, CCLK/SCL, CDTI/SDA and I2C pins correspond to 5V tolerant.

Note 3. AVSS and DVSS must be connected to the same analog ground plane.

Note 4. M/S pin is the digital input pin. However, M/S pin should be connected to AVDD or AVSS to prevent the noise to the analog input pins

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

|                            | RECOMMENDED OPERATING CONDITIONS |        |      |     |      |       |  |  |  |  |

|----------------------------|----------------------------------|--------|------|-----|------|-------|--|--|--|--|

| (AVSS, DVSS=0V; Note 1)    |                                  |        |      |     |      |       |  |  |  |  |

| Parameter                  |                                  | Symbol | min  | typ | max  | Units |  |  |  |  |

| Downer Sweeting            | Analog                           | AVDD   | 4.75 | 5.0 | 5.25 | V     |  |  |  |  |

| Power Supplies<br>(Note 5) | Digital                          | DVDD   | 3.0  | 3.3 | AVDD | V     |  |  |  |  |

| (Note 5)                   | Input Buffer                     | TVDD   | DVDD | 5.0 | AVDD | V     |  |  |  |  |

Note 1. All voltages with respect to ground.

Note 5. The power up sequence between AVDD, DVDD and TVDD is not critical.

WARNING: AKM assumes no responsibility for the usage beyond the conditions in this datasheet.

|                              | ANALOG CHARAC                 |                   |                 |               |              |

|------------------------------|-------------------------------|-------------------|-----------------|---------------|--------------|

|                              | V, DVDD=3.3V; AVSS=DVSS=      | ,                 | , , ,           |               |              |

| Signal Frequency=1kHz; 24bit | Data; Measurement frequency=2 | 0Hz ~ 20kHz       | at fs=48kHz; un | less otherwis | e specified) |

| Parameter                    |                               | min               | typ             | max           | Units        |

| Pre-Amp Characteristics:     |                               |                   |                 |               |              |

| Feedback Resistance          |                               | 10                |                 | 50            | kΩ           |

| S/(N+D)                      | (Note 6)                      | -                 | 100             |               | dB           |

| S/N (A-weighted)             | (Note 6)                      | -                 | 108             |               | dB           |

| Load Resistance              | (Note 7)                      | 6.3               |                 |               | kΩ           |

| Load Capacitance             |                               |                   |                 | 20            | pF           |

| Input PGA Characteristics:   |                               |                   |                 |               |              |

| Input Voltage                | (Note 8)                      | 0.9               | 1               | 1.1           | Vrms         |

| Input Resistance             | (Note 9)                      | 6.3               | 10              | 15            | kΩ           |

| Step Size                    |                               | 0.2               | 0.5             | 0.8           | dB           |

| Gain Control Range           | ALC = OFF                     | 0                 |                 | +18           | dB           |

|                              | ALC = ON                      | -9.5              |                 | +18           | dB           |

| ADC Analog Input Character   | istics: IPGA=0dB, ALC = OF    | <b>F</b> (Note 10 | ))              |               |              |

| Resolution                   |                               |                   |                 | 24            | Bits         |

| S/(N+D) (-0.5dBFS)           |                               | 84                | 94              |               | dB           |

| DR (-60dBFS, A-              | weighted)                     | 96                | 103             |               | dB           |

| S/N (A-weighted)             |                               | 96                | 103             |               | dB           |

| Interchannel Isolation       | (Note 11)                     | 90                | 110             |               | dB           |

| Interchannel Gain Mismatch   |                               |                   | 0.2             | 0.5           | dB           |

| Gain Drift                   |                               |                   | 100             | -             | ppm/°C       |

| Power Supply Rejection       | (Note 12)                     |                   | 50              | -             | dB           |

| Power Supplies               |                               |                   |                 |               |              |

| Power Supply Current         |                               |                   |                 |               |              |

| Normal Operation (PDN        | pin = "H")                    |                   |                 |               |              |

| AVDD                         |                               | 23                | 35              | mA            |              |

| DVDD+TVDD                    |                               | 4                 | 8               | mA            |              |

| Power-down mode (PDN         |                               | · ·               | Ŭ               |               |              |

| AVDD                         | pin = "L") (Note 13)          |                   | 10              | 100           |              |

|                              |                               |                   | 10              |               | μΑ           |

| DVDD+TVDD                    |                               |                   | 10              | 100           | μΑ           |

#### ANALOG CHARACTERISTICS

Note 6. This value is measured at LOUT and ROUT pins using the circuit as shown in Figure 25. The input signal voltage is 2Vrms.

Note 7. This value is the input impedance of an external device that the LOUT and ROUT pins can drive, when a device is

connected with LOUT and ROUT pin externally. The feedback resistor (min.  $10k\Omega$ ) that it is usually connected with the LOUT/ROUT pins, and the value of input impedance (min.  $6.3k\Omega$ ) of the IPGAL/R pins are not

included.

Note 8. Full scale (0dB) of the input voltage at ALC=OFF and IPGA=0dB.

Input voltage to IPGAL and IPGAR pins is proportional to AVDD voltage. typ. Vin = 0.2 x AVDD (Vrms).

Note 9. This value is input impedance of the IPGAL and IPGAR pins.

Note 10. This value is measured via the following path. Pre-Amp  $\rightarrow$  IPGA (Gain : 0dB)  $\rightarrow$  ADC. The measurement circuit is Figure 25.

Note 11. This value is the interchannel isolation between all the channels of the LIN1-5 and RIN1-5 when the applied input

signal causes the Pre-Amp output to equal IPGA input.

Note 12. PSR is applied to AVDD, DVDD and TVDD with 1kHz, 50mVpp.

Note 13. All digital input pins are held DVSS.

|                                                                      |               | FIL       | TER CHARA   | ACTERISTIC | S      |             |       |  |  |  |  |

|----------------------------------------------------------------------|---------------|-----------|-------------|------------|--------|-------------|-------|--|--|--|--|

| (Ta=-40 ~ 85°C; AVDD=4.75 ~ 5.25V; DVDD, TVDD=3.0 ~ 5.25V; fs=48kHz) |               |           |             |            |        |             |       |  |  |  |  |

| Parameter                                                            |               |           | Symbol      | min        | typ    | max         | Units |  |  |  |  |

| ADC Digital Filter                                                   | · (Decimation | n LPF):   |             |            |        |             |       |  |  |  |  |

| Passband                                                             | (Note 14)     | -0.005dB  | PB          | 0          |        | 21.5        | kHz   |  |  |  |  |

|                                                                      |               | -0.02dB   |             | -          | 21.768 | -           | kHz   |  |  |  |  |

|                                                                      |               | -0.06dB   |             | -          | 22.0   | -           | kHz   |  |  |  |  |

|                                                                      |               | -6.0dB    |             | -          | 24.0   | -           | kHz   |  |  |  |  |

| Stopband                                                             |               |           | SB          | 26.5       |        |             | kHz   |  |  |  |  |

| Passband Ripple                                                      |               |           | PR          |            |        | $\pm 0.005$ | dB    |  |  |  |  |

| Stopband Attenuation                                                 | on            |           | SA          | 80         |        |             | dB    |  |  |  |  |

| Group Delay                                                          |               | (Note 15) | GD          |            | 31     |             | 1/fs  |  |  |  |  |

| Group Delay Distor                                                   | tion          |           | $\Delta GD$ |            | 0      |             | μs    |  |  |  |  |

| <b>ADC Digital Filter</b>                                            | · (HPF):      |           |             |            |        |             |       |  |  |  |  |

| Frequency Respons                                                    | e (Note 14)   | -3dB      | FR          |            | 1.0    |             | Hz    |  |  |  |  |

|                                                                      |               | -0.5dB    |             |            | 2.9    |             | Hz    |  |  |  |  |

|                                                                      |               | -0.1dB    |             |            | 6.5    |             | Hz    |  |  |  |  |

Note 14. The passband and stopband frequencies scale with fs. For example, 21.768kHz at -0.02dB is 0.454 x fs. Note 15. The calculated delay time induced by digital filtering. This time is from the input of an analog signal to the setting of 24bit data both channels to the ADC output register for ADC.

|                                                            | DC CHARACTERISTICS |        |          |     |         |       |  |  |  |  |  |

|------------------------------------------------------------|--------------------|--------|----------|-----|---------|-------|--|--|--|--|--|

| (Ta=-40 ~ 85°C; AVDD=4.75 ~ 5.25V; DVDD, TVDD=3.0 ~ 5.25V) |                    |        |          |     |         |       |  |  |  |  |  |

| Parameter                                                  |                    | Symbol | min      | typ | max     | Units |  |  |  |  |  |

| High-Level Input Voltage                                   | (Note 16)          | VIH    | 70%DVDD  | -   |         | V     |  |  |  |  |  |

| Low-Level Input Voltage                                    | (Note 16)          | VIL    | -        | -   | 30%DVDD | V     |  |  |  |  |  |

| Input Voltage at AC Coupling                               | (Note 17)          | VAC    | 50%DVDD  | -   | -       | V     |  |  |  |  |  |

| High-Level Output Voltage                                  | (Iout=-400µA)      | VOH    | DVDD-0.5 | -   | -       | V     |  |  |  |  |  |

| Low-Level Output Voltage                                   |                    |        |          |     |         |       |  |  |  |  |  |

| (Except SDA p                                              | oin : Iout=400µA)  | VOL    | -        | -   | 0.5     | V     |  |  |  |  |  |

| (SDA pin : Iout=3mA)                                       |                    | VOL    | -        | -   | 0.4     | V     |  |  |  |  |  |

| Input Leakage Current                                      | (Note 18)          | Iin    | -        | -   | ±10     | μΑ    |  |  |  |  |  |

Note 16. SMUTE, SEL2-0, CSN/CAD1, CCLK/SCL, CDTI/SDA and I2C pins correspond to 5V tolerant.

Note 17. When AC coupled capacitor is connected to MCLK pin.

Note 18. SMUTE pin is internally connected to a pull-down resistor. (typ.  $100k\Omega$ )

| SWITCHING CHARACTERISTICS     |                                   |             |                            |      |        |       |

|-------------------------------|-----------------------------------|-------------|----------------------------|------|--------|-------|

| (Ta=-40 ~ 85°C; AVDD=-        | 4.75 ~ 5.25V; DVDD, TV            | 'DD=3.0 ~ 5 | .25V; C <sub>L</sub> =20pF | 7)   |        |       |

| Parameter                     | Parameter                         |             | min                        | typ  | max    | Units |

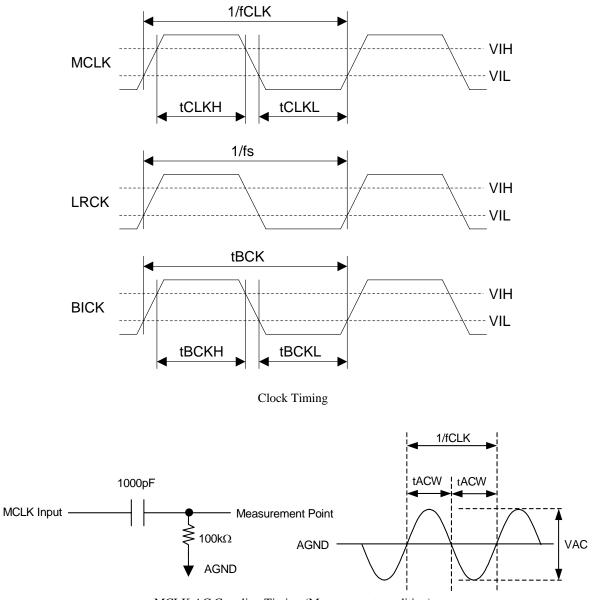

| Master Clock Timing           |                                   |             |                            |      |        |       |

| Frequency                     |                                   | fCLK        | 8.192                      |      | 24.576 | MHz   |

| Pulse Width Low               |                                   | tCLKL       | 0.3/fCLK                   |      |        | ns    |

| Pulse Width High              |                                   | tCLKH       | 0.3/fCLK                   |      |        | ns    |

| AC Pulse Width                | (Note 19)                         | tACW        | 0.4/fCLK                   |      |        | ns    |

| LRCK Frequency                |                                   |             |                            |      |        |       |

| Frequency                     |                                   | fsn         | 32                         |      | 48     | kHz   |

| Duty Cycle                    | Slave mode                        |             | 45                         |      | 55     | %     |

|                               | Master mode                       |             |                            | 50   |        | %     |

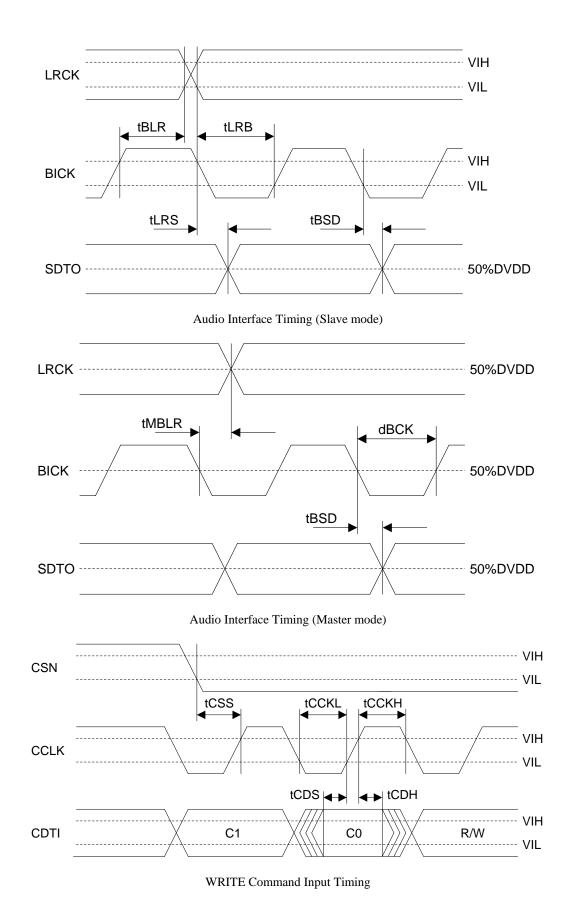

| Audio Interface Timing        |                                   |             |                            |      |        |       |

| Slave mode                    |                                   |             |                            |      |        |       |

| BICK Period                   |                                   | tBCK        | 160                        |      |        | ns    |

| BICK Pulse Width L            | ow                                | tBCKL       | 65                         |      |        | ns    |

| Pulse Width H                 | ligh                              | tBCKH       | 65                         |      |        | ns    |

| LRCK Edge to BICK             | (Note 20)                         | tLRB        | 30                         |      |        | ns    |

| BICK "↑" to LRCK              | Edge (Note 20)                    | tBLR        | 30                         |      |        | ns    |

| LRCK to SDTO (MS              | B) (Except I <sup>2</sup> S mode) | tLRS        |                            |      | 35     | ns    |

| BICK "↓" to SDTO              |                                   | tBSD        |                            |      | 35     | ns    |

| Master mode                   |                                   |             |                            |      |        |       |

| BICK Frequency                |                                   | fBCK        |                            | 64fs |        | Hz    |

| BICK Duty                     |                                   | dBCK        |                            | 50   |        | %     |

| BICK "↓" to LRCK              |                                   | tMBLR       | -20                        |      | 20     | ns    |

| BICK " $\downarrow$ " to SDTO |                                   | tBSD        | -20                        |      | 35     | ns    |

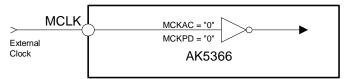

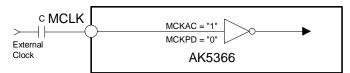

Note 19. Pulse width to ground level when MCLK is connected to a capacitor in series and a resistor is connected to ground.

Note 20. BICK rising edge must not occur at the same time as LRCK edge.

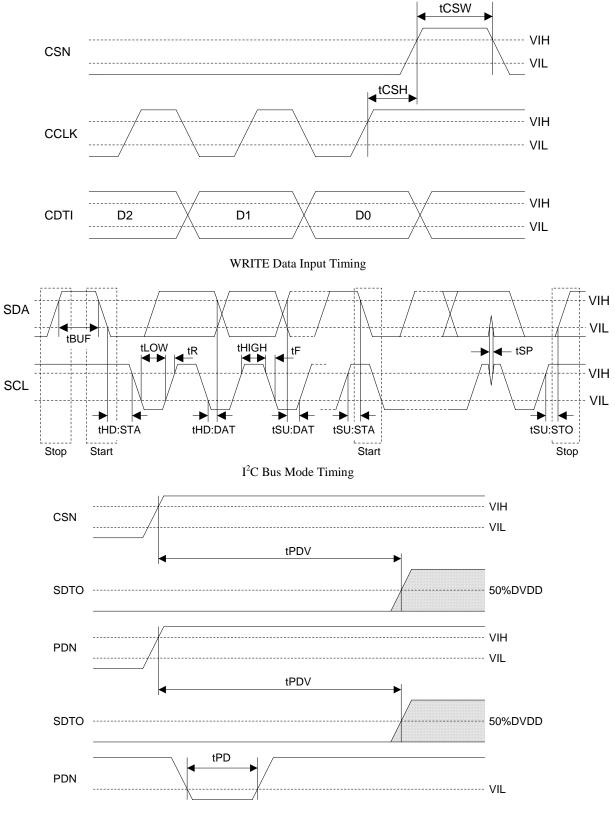

| Parameter                                                  |           | Symbol  | min | typ | max | Units |

|------------------------------------------------------------|-----------|---------|-----|-----|-----|-------|

| Control Interface Timing (3-wire Serial mod                | de):      |         |     |     |     |       |

| CCLK Period                                                |           | tCCK    | 200 |     |     | ns    |

| CCLK Pulse Width Low                                       |           | tCCKL   | 80  |     |     | ns    |

| Pulse Width High                                           |           | tCCKH   | 80  |     |     | ns    |

| CDTI Setup Time                                            |           | tCDS    | 40  |     |     | ns    |

| CDTI Hold Time                                             |           | tCDH    | 40  |     |     | ns    |

| CSN "H" Time                                               |           | tCSW    | 150 |     |     | ns    |

| CSN " $\downarrow$ " to CCLK " $\uparrow$ "                |           | tCSS    | 50  |     |     | ns    |

| CCLK "↑" to CSN "↑"                                        |           | tCSH    | 50  |     |     | ns    |

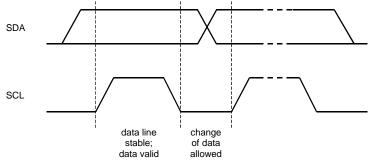

| <b>Control Interface Timing (I<sup>2</sup>C Bus mode):</b> |           |         |     |     |     |       |

| SCL Clock Frequency                                        |           | fSCL    | -   |     | 400 | kHz   |

| Bus Free Time Between Transmissions                        |           | tBUF    | 1.3 |     | -   | μs    |

| Start Condition Hold Time (prior to first clo              | ck pulse) | tHD:STA | 0.6 |     | -   | μs    |

| Clock Low Time                                             |           | tLOW    | 1.3 |     | -   | μs    |

| Clock High Time                                            |           | tHIGH   | 0.6 |     | -   | μs    |

| Setup Time for Repeated Start Condition                    |           | tSU:STA | 0.6 |     | -   | μs    |

| SDA Hold Time from SCL Falling                             | (Note 21) | tHD:DAT | 0   |     | -   | μs    |

| SDA Setup Time from SCL Rising                             |           | tSU:DAT | 0.1 |     | -   | μs    |

| Rise Time of Both SDA and SCL Lines                        |           | tR      | -   |     | 0.3 | μs    |

| Fall Time of Both SDA and SCL Lines                        |           | tF      | -   |     | 0.3 | μs    |

| Setup Time for Stop Condition                              |           | tSU:STO | 0.6 |     | -   | μs    |

| Pulse Width of Spike Noise Suppressed by Input Filter      |           | tSP     | 0   |     | 50  | ns    |

| Reset Timing                                               |           |         |     |     |     |       |

| PDN Pulse Width                                            | (Note 22) | tPD     | 150 |     |     | ns    |

| PDN "↑" to SDTO valid                                      | (Note 23) | tPDV    |     | 516 |     | 1/fs  |

| CSN "↑" to SDTO valid                                      | (Note 24) | tPDV    |     | 516 |     | 1/fs  |

Note 21. Data must be held long enough to bridge the 300ns-transition time of SCL.

Note 22. The AK5366 can be reset by bringing the PDN pin = "L".

Note 23. This cycle is the number of LRCK rising edges from the PDN pin = "H".

Note 24. This cycle is the number of LRCK rising edges from the CSN = "H".

Purchase of Asahi Kasei Microsystems Co., Ltd I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system, provided the system conform to the I<sup>2</sup>C specifications defined by Philips.

#### Timing Diagram

Power Down & Reset Timing

#### **OPERATION OVERVIEW**

#### System Clock

MCLK (256fs/384fs/512fs), BICK (48fs~) and LRCK (fs) clocks are required in slave mode. The LRCK clock input must be synchronized with MCLK, however the phase is not critical. MCLK frequency is automatically detected in slave mode. Table 1 shows the relationship of typical sampling frequency and the system clock frequency. Setting of CKS 1-0 bit is ignored.

MCLK (256fs/384fs/512fs) is required in master mode. MCLK frequency is selected by CKS1-0 bits as shown in Table 2. In master mode, after setting CKS1-0 bits, there is a possibility the frequency and duty of LRCK and BICK outputs become an abnormal state.

All external clocks (MCLK, BICK and LRCK) must be present unless PDN pin = "L" and PWN bit = "1". If these clocks are not provided, the AK5366 may draw excess current due to its use of internal dynamically refreshed logic. If the external clocks are not present, place the AK5366 in power-down mode (PDN pin = "L" or PWN bit = "0"). In master mode, the master clock (MCLK) must be provided unless PDN pin = "L".

| fs      | MCLK       |            |            |  |  |

|---------|------------|------------|------------|--|--|

| 13      | 256fs      | 384fs      | 512fs      |  |  |

| 32kHz   | 8.192MHz   | 12.288MHz  | 16.384MHz  |  |  |

| 44.1kHz | 11.2896MHz | 16.9344MHz | 22.5792MHz |  |  |

| 48kHz   | 12.288MHz  | 18.432MHz  | 24.576MHz  |  |  |

| CKS1 | CKS0 | MCLK  |         |

|------|------|-------|---------|

| 0    | 0    | 256fs | Default |

| 0    | 1    | 512fs |         |

| 1    | 0    | 384fs |         |

| 1    | 1    | N/A   |         |

Table 1. System clock example (Slave mode)

Table 2. Master clock frequency select (Master mode)

#### [MCLK AC Coupling input]

MCLK AC coupling input becomes possible by controlling MCKPD bit and MCKAC bit.

| Master Clock                |            | Status                         | MCKAC bit | MCKPD bit  |

|-----------------------------|------------|--------------------------------|-----------|------------|

| External Clock Direct Input | (Figure 1) | Clock is input to MCLK pin.    | 0         | 0          |

|                             |            | Clock isn't input to MCLK pin. | 0         | Don't care |

| AC Coupling Input           | (Figure 2) | Clock is input to MCLK pin.    | 1         | 0          |

|                             | -          | Clock isn't input to MCLK pin. | 1         | 1          |

Table 3. MCKPD bit and MCKAC bit setting for Master Clock Status

(1) External clock direct input

Figure 1. External Master Clock Input Block

(2) AC coupling input

$\label{eq:Figure 2. External Clock mode (Input : $\geq 50\% DVDD, Input circuit example)$$ - Note: This clock level must not exceed DVDD level. (C : 0.1 \mu F)$

#### ■ Audio Interface Format

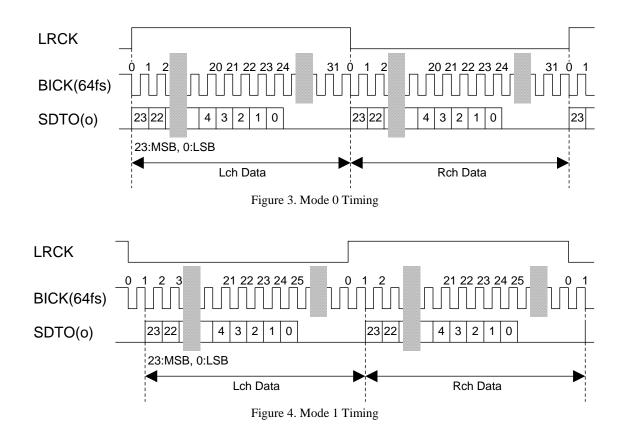

Two kinds of data formats can be chosen with the DIF bit (Table 4). In both modes, the serial data is in MSB first, 2's compliment format. The SDTO is clocked out on the falling edge of BICK. The audio interface supports both master and slave modes. In master mode, BICK and LRCK are output with the BICK frequency fixed to 64fs and the LRCK frequency fixed to 1fs.

| Mode | DIF bit | SDTO                               | LRCK | BICK                            | Figure   |         |

|------|---------|------------------------------------|------|---------------------------------|----------|---------|

| 0    | 0       | 24bit, MSB justified               | H/L  | ≥ 48fs (Slave)<br>64fs (Master) | Figure 3 | Default |

| 1    | 1       | 24bit, I <sup>2</sup> S Compatible | L/H  | ≥ 48fs (Slave)<br>64fs (Master) | Figure 4 |         |

Table 4. Audio Interface Format

#### Master Mode and Slave Mode

The M/S pin selects either master or slave mode. M/S pin = "H" selects master mode and "L" selects slave mode. The AK5366 outputs BICK and LRCK in master mode. In slave mode, MCLK, BICK and LRCK are input externally.

|              | BICK, LRCK    |

|--------------|---------------|

| Slave Mode   | BICK = Input  |

| Slave Mode   | LRCK = Input  |

| Master Mode  | BICK = Output |

| Waster Would | LRCK = Output |

Table 5. Master mode/Slave mode

#### ■ Digital High Pass Filter

The ADC has a digital high pass filter for DC offset cancellation. The cut-off frequency of the HPF is 1.0Hz (@fs=48kHz) and scales with sampling rate (fs).

#### ■ Power-up/down

The AK5366 is placed in the power-down mode by bringing PDN pin = "L" and the digital filter is also reset at the same time. This reset should always be done after power-up. An analog initialization cycle starts after exiting the power-down mode. Therefore, the output data SDTO becomes available after 516 cycles of LRCK.

| Power Supply                      |              |                 |     |                    |

|-----------------------------------|--------------|-----------------|-----|--------------------|

| PDN pin                           | 150ns        |                 |     |                    |

| ADC Internal State                | PDN          | INITA           |     | Normal             |

| ALC bit                           |              | "1"             |     | "O"                |

| ALC Function                      |              | ON              |     | OFF                |

| IPGA                              |              | Unknow          | n   | (1)                |

| SDTO                              | "0"          | ,               |     | Output             |

| External clocks<br>in slave mode  | The clock    | ks can be stopp |     | , BICK, LRCK Input |

| External clocks<br>in master mode | ×            | MCLK Input      |     |                    |

| BICK, LRCK<br>in master mode      | Fixed to "L" |                 | BIC | K, LRCK Output     |

• PDN : Power down state.

• INITA : Initializing period of ADC analog section (516/fs).

• (1): After ALC operation is disabled, the IPGA changes to the last written data during or before ALC operation.

Figure 5. Power-up Sequence

#### Peak Hold Circuit

The AK5366 includes the peak hold circuit. The peak is held L/R audio data independently. These registers are reset by reading 8bit of MSB, reading 8bit of both MSB and LSB should be continuity controlled by reading in order of 8bit of MSB from LSB. After reading 8bit of LSB the last, 8bit of MSB is lost by reading 8bit of LSB the last. The output value is the absolute value. Full scale is "FFFFH".

#### ■ Input Selector

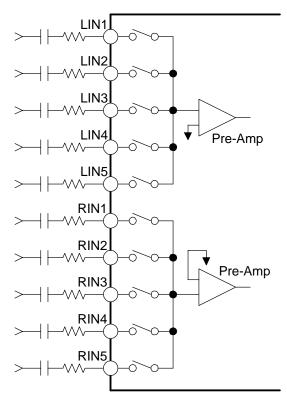

The AK5366 includes 5ch stereo input selectors (Figure 6). The input selector is 5 to 1 selector. The input channel is set by the SEL2-0 bits (Table 6) and the SEL2-0 pins (Table 7). The SEL2-0 pins should be fixed to "LLL" if the AK5366 is controlled by the SEL 2-0 bits, because the setting of the SEL2-0 pins are prior to the SEL2-0 bits setting.

| SEL2 bit | SEL1 bit | SEL0 bit | Input Channel |         |

|----------|----------|----------|---------------|---------|

| 0        | 0        | 0        | LIN1 / RIN1   | Default |

| 0        | 0        | 1        | LIN2 / RIN2   |         |

| 0        | 1        | 0        | LIN3 / RIN3   |         |

| 0        | 1        | 1        | LIN4 / RIN4   |         |

| 1        | 0        | 0        | LIN5 / RIN5   | ]       |

| SEL2 pin | SEL1 pin | SEL0 pin | Input Channel |

|----------|----------|----------|---------------|

| L        | L        | L        | LIN1 / RIN1   |

| L        | L        | Н        | LIN2 / RIN2   |

| L        | Н        | L        | LIN3 / RIN3   |

| L        | Н        | Н        | LIN4 / RIN4   |

| Н        | L        | L        | LIN5 / RIN5   |

Table 6. Input Selector (SEL2-0 pin = "LLL")

Table 7. Input Selector (SEL2-0 bit = "000")

#### Figure 6. Input Selector

#### [Input selector switching sequence]

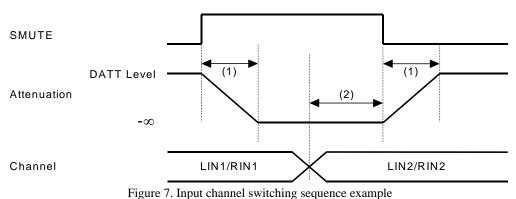

The input selector should be changed after soft mute to avoid the switching noise of the input selector (Figure 7).

- 1. Enable the soft mute before changing channel.

- 2. Change channel.

- 3. Disable the soft mute.

rigure // input channer switching sequence example

The period of (1) varies in the setting value of DATT. It takes 1028/fs to mute when DATT value is +8dB.

When changing channels, the input channel should be changed during (2). The period of (2) should be around 200ms because there is some DC difference between the channels.

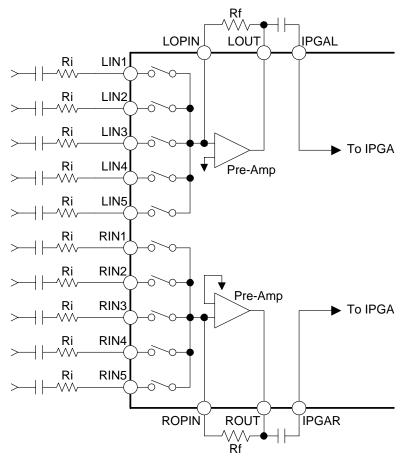

#### Input Attenuator

The input ATTs are constructed by adding the input resistor (Ri) for LIN1-5/RIN1-5 pins and the feedback resistor (Rf) between LOPIN (ROPIN) pin and LOUT (ROUT) pin (Figure 8). The input voltage range of the IPGAL/IPGAR pin is typically typ. 0.2 x AVDD (Vrms). If the input voltage of the input selector exceeds typ. 0.2 x AVDD, the input voltage of the IPGAL/IPGAR pins must be attenuated to 0.2 x AVDD by the input ATTs. Table 8 shows the example of Ri and Rf.

Figure 8. Input ATT

• Example for input range

| Input Range | Ri [kΩ] | Rf [kΩ] | ATT Gain [dB] | IPGAL/R pin |

|-------------|---------|---------|---------------|-------------|

| 4Vrms       | 47      | 12      | -11.86        | 1.02Vrms    |

| 2Vrms       | 47      | 24      | -5.84         | 1.02Vrms    |

| 1Vrms       | 47      | 47      | 0             | 1Vrms       |

Table 8. Input ATT example

#### Input Volume

The AK5366 includes two independent channel analog volumes (IPGA) with 37 levels at 0.5dB steps located in front of the ADC.

The IPGA is a true analog volume control that improves the S/N ratio as seen in Table 9. Independent zero-crossing detection is used to ensure level changes only occur during zero-crossings. If there are no zero-crossings, the level will then change after a time-out period (Table 10); the time-out period scales with fs. If a new value is written to the IPGA register before the IPGA changes at the zero crossing or time-out, the previous value becomes invalid. The timer (channel independent) for time-out is reset and the timer restarts for new IPGA value.

|                      | Input Gain Setting      |  |  |  |  |  |

|----------------------|-------------------------|--|--|--|--|--|

|                      | 0dB +6dB +18dB          |  |  |  |  |  |

| fs=48kHz, A-weight   | veight 103dB 100dB 89dB |  |  |  |  |  |

| Table 9. PGA+ADC S/N |                         |  |  |  |  |  |

| ZTM1 | ZTM0 | Zero crossing timeout period | @fs=48kHz |         |

|------|------|------------------------------|-----------|---------|

| 0    | 0    | 288/fs                       | 6ms       |         |

| 0    | 1    | 1152/fs                      | 24ms      |         |

| 1    | 0    | 2304/fs                      | 48ms      | Default |

| 1    | 1    | 4608/fs                      | 96ms      |         |

Table 10. Zero crossing timeout period

[Writing operation at ALC Enable]

Writing to the area over 7FH (Table 17) of IPGL/R registers (04H, 05H) is ignored during ALC operation. After ALC is disabled, the IPGA changes to the last written data by zero-crossing or time-out. In case of writing to the DATT area (08H, 09H), the DATT changes even if ALC is enabled.

#### Output Volume

The AK5366 includes two independent channel digital volumes (DATT) with 144 levels at 0.5dB steps located behind the ADC. When changing levels, transitions are executed via soft changes; thus no switching noise occurs during these transitions. The data must not be written over 90H.

| ATTL/R7-0 | Attenuation  |         |

|-----------|--------------|---------|

| 8FH       | +8.0dB       |         |

| 8EH       | +7.5dB       |         |

| :         | :            |         |

| 81H       | +1.0dB       |         |

| 80H       | +0.5dB       |         |

| 7FH       | 0dB          | Default |

| 7EH       | -0.5dB       |         |

| 7DH       | -1.0dB       |         |

| :         | :            |         |

| 02H       | -62.5dB      |         |

| 01H       | -63dB        |         |

| 00H       | Mute (−∞)    |         |

| T-1-1-11  | DATT C. I. T |         |

Table 11. DATT Code Table

#### ALC Operation

#### [1] ALC Limiter Operation

When the ALC limiter is enabled, and either Lch or Rch exceed the ALC limiter detection level (LMTH bit), the IPGA value is attenuated by the amount defined in the ALC limiter ATT step (LMAT bit) automatically. Then the IPGA value is changed commonly for L/R channels.

When the ZELMN bit = "1", the timeout period is set by the LTM1-0 bits. The operation for attenuation is done continuously until the input signal level becomes the ALC limiter detection level (LMTH bit) or less. If the ALC bit does not change into "0" or the ALC pin does not change into "L" after completing the attenuation, the attenuation operation repeats until the input signal level equals or exceeds the ALC limiter detection level (LMTH bit).

When the ZELMN bit = "0", the timeout period is set by the ZTM1-0 bits. This enables the zero-crossing attenuation function so that the IPGA value is attenuated at the zero-detect points of the waveform.

When FR bit = "1", the ALC operation corresponds to the impulse noise in additional to the normal ALC operation. Then if the impulse noise is supplied at ZELMN bit = "0", the ALC operation becomes the faster period than a set of ZTM1-0 bits. In case of ZELMN bit = "1", it becomes the same period as LTM1-0 bits. When FR bit = "0", the ALC operation is the normal ALC operation.

#### [2] ALC Recovery Operation

The ALC recovery refers to the amount of time that the AK5366 will allow a signal to exceed a predetermined limiting value prior to enabling the limiting function. The ALC recovery operation uses the WTM1-0 bits to define the wait period used after completing an ALC limiter operation. If the input signal does not exceed the "ALC Recovery Waiting Counter Reset Level", the ALC recovery operation starts. The IPGA value increases automatically during this operation up to the reference level (REF7-0 bits). The ALC recovery operation is done at a period set by the WTM1-0 bits. Zero crossing is detected during WTM1-0, the ALC recovery operation waits WTM1-0 period and the next recovery operation starts.

During the ALC recovery operation, when input signal level exceeds the ALC limiter detection level (LMTH bit), the ALC recovery operation changes immediately into an ALC limiter operation.

In the case of "(Recovery waiting counter reset level)  $\leq$  Input Signal < Limiter detection level" during the ALC recovery operation, the wait timer for the ALC recovery operation is reset. Therefore, in the case of "(Recovery waiting counter reset level) > Input Signal", the wait timer for the ALC recovery operation starts.

When the impulse noise is input at FR bit = "1", the ALC recovery operation becomes faster than a normal recovery operation. When the FR bit = "0", the ALC recovery operation is done by normal period.

#### [3] ALC Level Diagram

#### (1) ALC=OFF

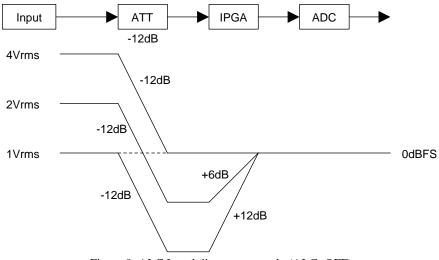

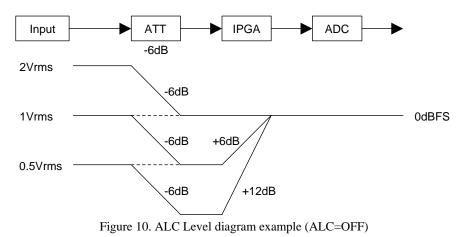

Figure 9 and 10 show the level diagram example at ALC=OFF. In Figure 9, Input ATT is -12dB.

Figure 9. ALC Level diagram example (ALC=OFF)

In Figure 10, Input ATT is -6dB.

#### (2) ALC=ON

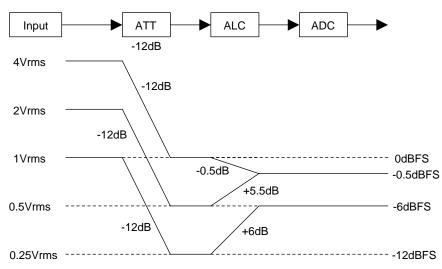

Figure 11 and 12 show the level diagram example at ALC=ON. In Figure 11, Input ATT is -12dB and REF7-0 bits are "8CH".

Figure 11. ALC Level diagram example (ALC=ON, LMTH bit="0")

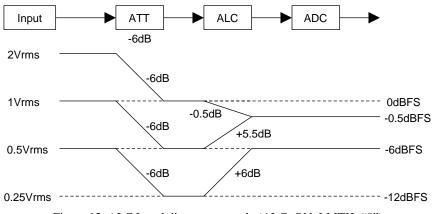

In Figure 12, Input ATT is -6dB and REF7-0 bits are "8CH".

Figure 12. ALC Level diagram example (ALC=ON, LMTH="0")

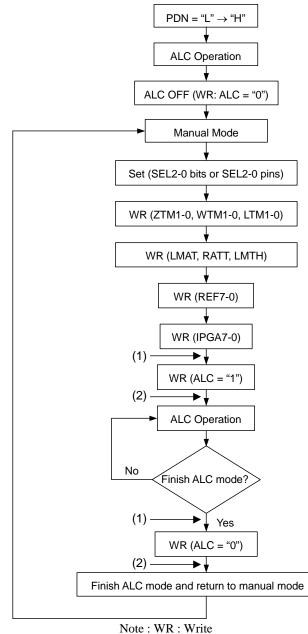

#### [4] Example of ALC Operation

The following registers should not be changed during the ALC operation.

- LTM1-0, LMTH, LMAT, WTM1-0, ZTM1-0, RATT, REF7-0, ZELMN bits

- The IPGA value of Lch becomes the start value if the IPGA value is different with Lch and Rch when the ALC starts.

- Writing to the area over 80H (Table 17) of IPGL/R registers (04H, 05H) is ignored during ALC operation. After ALC is disabled, the IPGA changes to the last written data by zero-crossing or time-out. In case of writing to

- the

DATT area (Table 11) of DATT registers (08H, 09H), the DATT changes even if ALC is enabled.

Figure 13. Registers set-up sequence at ALC operation

(1): Enable soft mute (2): Disable soft mute

Note : After ALC operation is disabled, the IPGA changes to the last written data during or before ALC operation.

[5] IPGA value before and after ALC operation

After ALC operation is disabled, the IPGA changes to the last written data during or before ALC operation.

[Operation Example 1]

- 1. Set IPGA = +12dB at ALC=OFF. DATT portion is set to 0dB internally.

- 2. ALC=ON after soft mute is enabled.

- 3. Disable the soft mute.

- 4. During ALC operation. The IPGA changes from -9.5dB to the value set by REF7-0 bits.

- 5. ALC=OFF after soft mute is enabled.

- 6. Disable the soft mute. The IPGA return to +12dB automatically.

[Operation Example 2]

- 1. Set IPGA = +12dB at ALC=OFF. DATT portion is set to 0dB internally.

- 2. ALC=ON after soft mute is enabled.

- 3. Disable the soft mute.

- 4. During ALC operation. When the DATT portion is set to -10dB, the IPGA changes from -19.5dB to the value set by REF7-0 bits.

- 5. ALC=OFF after soft mute is enabled.

- 6. Disable the soft mute. The IPGA setting is -10dB.

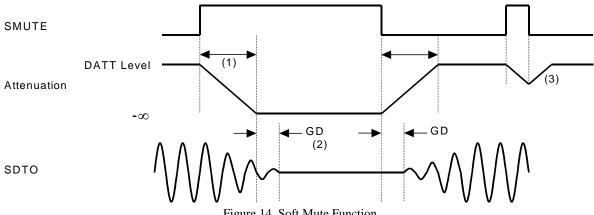

#### ■ Soft Mute Operation

Soft mute operation is performed in the digital domain of the ADC output.

Soft mute can be controlled by SMUTE bit or SMUTE pin. The SMUTE bit and SMUTE pin are ORed between pin and register. When SMUTE bit goes "1" or SMUTE pin goes "H", the ADC output data is attenuated by  $-\infty$  within 1028 LRCK cycles. When the SMUTE bit returned "0" and SMUTE pin goes "L" the mute is cancelled and the output attenuation gradually changes to DATT value within 1028 LRCK cycles. If the soft mute is cancelled before mute state after starting of the operation, the attenuation is discontinued and returned to DATT value.

Soft mute function and digital volume are common.

Figure 14. Soft Mute Function

(1) The output signal is attenuated by  $-\infty$  within 1028 LRCK cycles (1028/fs).

(2) Digital output delay from the analog input is called the group delay (GD).

(3) If the soft mute is cancelled before the mute, the attenuation is discontinued and returned to DATT value.

#### Chip Address

In case of 3-wire control mode, the chip address is fixed to C1 bit = "1" and C0 bit = "0". Table 12 shows the relationship between chip address (C1-0 bits) and CAD1 pin in  $I^2$ C-bus control mode.

| CAD1 pin                                               | C1 bit | C0 bit       |  |  |  |

|--------------------------------------------------------|--------|--------------|--|--|--|

| L                                                      | 0      | Fixed to "1" |  |  |  |

| Н                                                      | 1      | Fixed to "1" |  |  |  |

| Table 12. Chip address in I <sup>2</sup> C-bus control |        |              |  |  |  |

Note : C1 bit should match with the input level of CAD1 pin.

#### Serial Control Interface

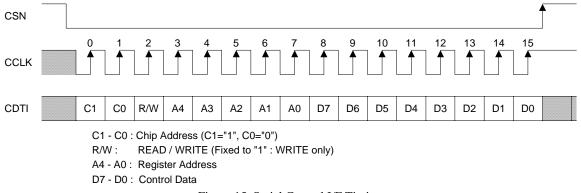

(1) 3-wire Serial Control Mode (I2C pin = "L")

Internal registers may be written by using the 3-wire  $\mu$ P interface pins (CSN, CCLK and CDTI). The data on this interface consists of a Chip address (2bits, Fixed to "10"), Read/Write (1bit, Fixed to "1", Write only), Register address (MSB first, 5bits) and Control data (MSB first, 8bits). Address and data is clocked in on the rising edge of CCLK and data is clocked out on the falling edge. After a low-to-high transition of CSN, data is latched for write operations. The clock speed of CCLK is 5MHz (max). The value of internal registers is initialized at PDN pin = "L".

Figure 15. Serial Control I/F Timing

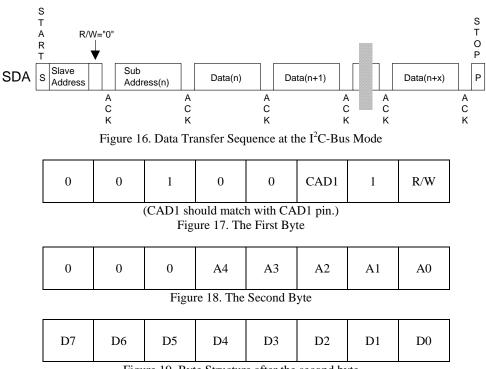

#### (2) $I^2$ C-bus Control Mode (CTRL pin = "H")

The AK5366 supports the standard-mode and the first-mode I<sup>2</sup>C-bus system (max: 400kHz).

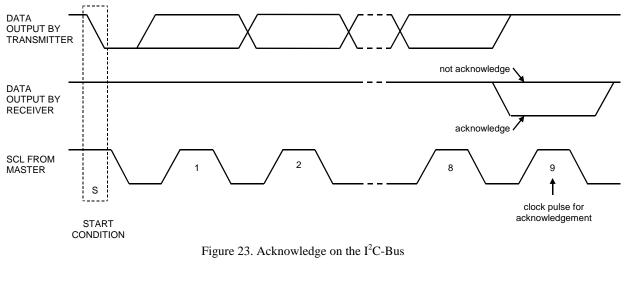

#### (2)-1. WRITE Operations

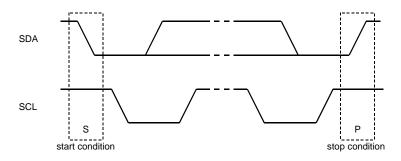

Figure 16 shows the data transfer sequence for the  $I^2C$ -bus mode. All commands are preceded by a START condition. A HIGH to LOW transition on the SDA line while SCL is HIGH indicates a START condition (Figure 22). After the START condition, a slave address is sent. This address is 7 bits long followed by an eighth bit that is a data direction bit (R/W). The most significant five bits of the slave address are fixed as "00100". The next one bit are CAD1 (device address bits). This one bit identify the specific device on the bus. The hard-wired input pin (CAD1 pin) set these device address bits (Figure 17). If the slave address matches that of the AK5366, the AK5366 generates an acknowledge and the operation is executed. The master must generate the acknowledge-related clock pulse and release the SDA line (HIGH) during the acknowledge clock pulse (Figure 23). A R/W bit value of "1" indicates that the read operation is to be executed. A "0" indicates that the write operation is to be executed.

The second byte consists of the control register address of the AK5366. The format is MSB first, and those most significant 3-bits are fixed to zeros (Figure 18). The data after the second byte contains control data. The format is MSB first, 8bits (Figure 19). The AK5366 generates an acknowledge after each byte has been received. A data transfer is always terminated by a STOP condition generated by the master. A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition (Figure 22).

The AK5366 can perform more than one byte write operation per sequence. After receipt of the third byte the AK5366 generates an acknowledge and awaits the next data. The master can transmit more than one byte instead of terminating the write cycle after the first data byte is transferred. After receiving each data packet the internal 5-bit address counter is incremented by one, and the next data is automatically taken into the next address. If the address exceeds 0DH prior to generating the stop condition, the address counter will "roll over" to 00H and the previous data will be overwritten.

The data on the SDA line must remain stable during the HIGH period of the clock. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW (Figure 24) except for the START and STOP conditions.

Figure 19. Byte Structure after the second byte

#### (2)-2. READ Operations

Set the R/W bit = "1" for the READ operation of the AK5366. After transmission of data, the master can read the next address's data by generating an acknowledge instead of terminating the write cycle after the receipt of the first data word. After receiving each data packet the internal 5-bit address counter is incremented by one, and the next data is automatically taken into the next address. If the address exceeds 0DH prior to generating a stop condition, the address counter will "roll over" to 00H and the previous data will be overwritten.

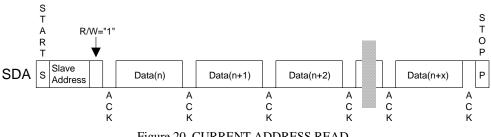

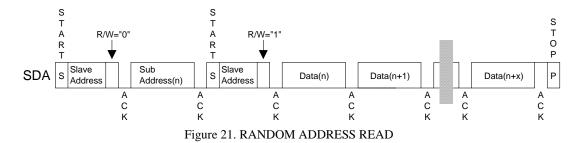

The AK5366 supports two basic read operations: CURRENT ADDRESS READ and RANDOM ADDRESS READ.

#### (2)-2-1. CURRENT ADDRESS READ

The AK5366 contains an internal address counter that maintains the address of the last word accessed, incremented by one. Therefore, if the last access (either a read or write) were to address n, the next CURRENT READ operation would access data from the address n+1. After receipt of the slave address with R/W bit set to "1", the AK5366 generates an acknowledge, transmits 1-byte of data to the address set by the internal address counter and increments the internal address counter by 1. If the master does not generate an acknowledge to the data but instead generates a stop condition, the AK5366 ceases transmission.

#### Figure 20. CURRENT ADDRESS READ

#### (2)-2-2. RANDOM ADDRESS READ

The random read operation allows the master to access any memory location at random. Prior to issuing the slave address with the R/W bit set to "1", the master must first perform a "dummy" write operation. The master issues a start request, a slave address (R/W bit = "0") and then the register address to read. After the register address is acknowledged, the master immediately reissues the start request and the slave address with the R/W bit set to "1". The AK5366 then generates an acknowledge, 1 byte of data and increments the internal address counter by 1. If the master does not generate an acknowledge to the data but instead generates a stop condition, the AK5366 ceases transmission.

MS0309-E-00

Figure 22. START and STOP Conditions

Figure 24. Bit Transfer on the I<sup>2</sup>C-Bus

### Control by Pin and Bit

| Function            | Pin                            | bit                    |

|---------------------|--------------------------------|------------------------|

|                     | SEL2-0 Pin                     | SEL2-0 bit             |

| In word Cale of a m | "LLL" : LIN1/RIN1              | "000" : LIN1/RIN1      |

|                     | "LLH" : LIN2/RIN2              | "001" : LIN2/RIN2      |

| Input Selector      | "LHL" : LIN3/RIN3              | "010": LIN3/RIN3       |

|                     | "LHH" : LIN4/RIN4              | "011" : LIN4/RIN4      |

|                     | "HLL" : LIN5/RIN5              | "100" : LIN5/RIN5      |

|                     | SMUTE Pin (Internal Pull-down) | SMUTE bit              |

| Soft Mute           | "L" : Normal operation         | "0" : Normal operation |

|                     | "H" : Soft muted               | "1" : Soft muted       |

Table 13. Pin and Bit control

Note : The SEL2-0 pins should be fixed to "LLL" if the AK5366 is controlled by the SEL2-0 bits, because the setting of the

SEL2-0 pins are prior to the SEL2-0 bits setting. Soft Mute is ORed between pin and register.

#### Register Map

| Addr | Register Name              | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

|------|----------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 00H  | Power Down & Reset Control | 0     | 0     | 0     | 0     | 0     | MCKPD | MCKAC | PWN   |

| 01H  | Input Selector Control     | 0     | 0     | 0     | 0     | 0     | SEL2  | SEL1  | SEL0  |

| 02H  | Clock & Format Control     | 0     | 0     | 0     | 0     | DIF   | CKS1  | CKS0  | SMUTE |

| 03H  | Timer Select               | 0     | 0     | LTM1  | LTM0  | ZTM1  | ZTM0  | WTM1  | WTM0  |

| 04H  | Lch IPGA Control           | IPGL7 | IPGL6 | IPGL5 | IPGL4 | IPGL3 | IPGL2 | IPGL1 | IPGL0 |

| 05H  | Rch IPGA Control           | IPGR7 | IPGR6 | IPGR5 | IPGR4 | IPGR3 | IPGR2 | IPGR1 | IPGR0 |

| 06H  | ALC Mode Control 1         | 0     | 0     | ZELMN | ALC   | FR    | LMTH  | RATT  | LMAT  |

| 07H  | ALC Mode Control 2         | REF7  | REF6  | REF5  | REF4  | REF3  | REF2  | REF1  | REF0  |

| 08H  | Lch DATT Control           | ATTL7 | ATTL6 | ATTL5 | ATTL7 | ATTL7 | ATTL7 | ATTL7 | ATTL0 |

| 09H  | Rch DATT Control           | ATTR7 | ATTR6 | ATTR5 | ATTR4 | ATTR3 | ATTR2 | ATTR1 | ATTR0 |

| 0AH  | Lch Peak Hold Low Byte     | PHL7  | PHL6  | PHL5  | PHL4  | PHL3  | PHL2  | PHL1  | PHL0  |

| 0BH  | Lch Peak Hold High Byte    | PHL15 | PHL14 | PHL13 | PHL12 | PHL11 | PHL10 | PHL9  | PHL8  |

| 0CH  | Rch Peak Hold Low Byte     | PHR7  | PHR6  | PHR5  | PHR4  | PHR3  | PHR2  | PHR1  | PHR0  |

| 0DH  | Rch Peak Hold High Byte    | PHR15 | PHR14 | PHR13 | PHR12 | PHR11 | PHR10 | PHR9  | PHR8  |

PDN pin = "L" resets the registers to their default values.

Note: Unused bits must contain a "0" value.

Note: Only write to address 00H to 09H.

Note: 3-wire serial control does not support Read function. I2C control supports Read function.

#### Register Definitions

| Addr | Register Name              | D7 | D6 | D5 | D4 | D3 | D2    | D1    | D0  |

|------|----------------------------|----|----|----|----|----|-------|-------|-----|

| 00H  | Power Down & Reset Control | 0  | 0  | 0  | 0  | 0  | MCKPD | MCKAC | PWN |

|      | R/W                        | RD | RD | RD | RD | RD | R/W   | R/W   | R/W |

|      | Default                    |    | 0  | 0  | 0  | 0  | 0     | 0     | 1   |

PWN: Power down control

0 : Power down. All registers are not initialized.

1 : Normal Operation (Default)

"0" powers down all sections and then both IPGA and ADC do not operate. The contents of all register are not initialized and enabled to write to the registers.

When MCLK and LRCK are changed, it is not necessary to reset by the PDN pin or PWN bit because the AK5366 builds in reset-free circuit. However, it can be reduced the noise by reset.

MCKAC: Master Clock input Mode Select

0 : CMOS input (Default)

1 : AC coupling input

MCKPD: MCLK Input Buffer Control

0 : Enable (Default)

1 : Disable

When MCLK input with AC coupling is stopped, MCKPD bit should be set to "1".

| Addr    | Register Name          | D7 | D6 | D5 | D4 | D3 | D2   | D1   | D0   |

|---------|------------------------|----|----|----|----|----|------|------|------|

| 01H     | Input Selector Control | 0  | 0  | 0  | 0  | 0  | SEL2 | SEL1 | SEL0 |

|         | R/W                    | RD | RD | RD | RD | RD | R/W  | R/W  | R/W  |

| Default |                        | 0  | 0  | 0  | 0  | 0  | 0    | 0    | 0    |

SEL2-0: Input selector (see Table 6) Initial values are "000".

| Addr    | Register Name          | D7 | D6 | D5 | D4 | D3  | D2   | D1   | D0    |

|---------|------------------------|----|----|----|----|-----|------|------|-------|

| 02H     | Clock & Format Control | 0  | 0  | 0  | 0  | DIF | CKS1 | CKS0 | SMUTE |

|         | R/W                    |    | RD | RD | RD | R/W | R/W  | R/W  | R/W   |

| Default |                        | 0  | 0  | 0  | 0  | 0   | 0    | 0    | 0     |

SMUTE: Soft Mute control

- 0 : Normal Operation (Default)

- 1 : SDTO outputs soft-muted.

- CKS1-0: Master clock frequency select (see Table 2) Initial values are "00".

- DIF: Audio interface format (see Table 4) Initial values are "0" (24bit, MSB first).

| Addr | Register Name | D7 | D6 | D5   | D4   | D3   | D2   | D1   | D0   |

|------|---------------|----|----|------|------|------|------|------|------|

| 03H  | Timer Select  | 0  | 0  | LTM1 | LTM0 | ZTM1 | ZTM0 | WTM1 | WTM0 |

|      | R/W           | RD | RD | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

|      | Default       | 0  | 0  | 1    | 0    | 1    | 0    | 1    | 1    |

WTM1-0: ALC Recovery waiting time (see Table 14)

A period of recovery operation when any limiter operation does not occur during the ALC operation.

| WTM1 | WTM0 | ALC recovery operation waiting period | @fs=48kHz |         |

|------|------|---------------------------------------|-----------|---------|

| 0    | 0    | 288/fs                                | 6ms       |         |

| 0    | 1    | 1152/fs                               | 24ms      |         |

| 1    | 0    | 2304/fs                               | 48ms      |         |

| 1    | 1    | 4608/fs                               | 96ms      | Default |

Table 14. ALC recovery waiting time

#### ZTM1-0: Zero crossing timeout (see Table 15)

When the IPGA of each L/R channels perform zero crossing or timeout independently, the IPGA value is changed by the  $\mu$ P WRITE operation, ALC recovery operation or ALC limiter operation (ZELMN bit = "0").

| ZTM1 | ZTM0 | Zero crossing timeout period | @fs=48kHz |         |

|------|------|------------------------------|-----------|---------|

| 0    | 0    | 288/fs                       | бms       |         |

| 0    | 1    | 1152/fs                      | 24ms      |         |

| 1    | 0    | 2304/fs                      | 48ms      | Default |

| 1    | 1    | 4608/fs                      | 96ms      |         |

Table 15. Zero crossing timeout

LTM1-0: ALC Limiter period (see Table 16)

When ZELMN bit = "1", the IPGA value is changed immediately. When the IPGA value is changed continuously, the change is done by the period set by the LTM1-0 bits.

| LTM1 | LTM0 | ALC limiter operation period | @fs=48kHz |         |

|------|------|------------------------------|-----------|---------|

| 0    | 0    | 3/fs                         | 63µs      |         |

| 0    | 1    | 6/fs                         | 125µs     |         |

| 1    | 0    | 12/fs                        | 250µs     | Default |

| 1    | 1    | 24/fs                        | 500µs     |         |

Table 16. ALC limiter period

| Addr | Register Name    | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

|------|------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 04H  | Lch IPGA Control | IPGL7 | IPGL6 | IPGL5 | IPGL4 | IPGL3 | IPGL2 | IPGL1 | IPGL0 |

| 05H  | Rch IPGA Control | IPGR7 | IPGR6 | IPGR5 | IPGR4 | IPGR3 | IPGR2 | IPGR1 | IPGR0 |

|      | R/W              | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

|      | Default          | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

IPGL/R7-0: Input PGA & Digital volume control (see Table 17) Initial values are "80H".

The data must not be written under 80H.

Writing to the area over 7FH (Table 17) of IPGL/R registers (04H, 05H) is ignored during ALC operation. After ALC is disabled, the IPGA changes to the last written data by zero-crossing or time-out. In case of writing to the DATT area (Table 11) of DATT registers (08H, 09H), the DATT changes even if ALC is enabled.

| Data (hex) | Gain (dB) | Step width (dB) |                               |

|------------|-----------|-----------------|-------------------------------|

| A4H        | +18       | 0.5             |                               |

| :          | :         | 0.5             |                               |

| 9EH        | +15       | 0.5             |                               |

| :          | :         | 0.5             |                               |

| 98H        | +12       | 0.5             | IPGA                          |

| 97H        | +11.5     | 0.5             |                               |

| 96H        | +11       | 0.5             | Analog volume with 0.5dB step |

| :          | :         | 0.5             |                               |

| 82H        | +1.0      | 0.5             |                               |

| 81H        | +0.5      | 0.5             |                               |

| 80H        | 0         | -               |                               |

Table 17. IPGA Code Table

| Addr | Register Name      | D7 | D6 | D5    | D4  | D3  | D2   | D1   | D0   |

|------|--------------------|----|----|-------|-----|-----|------|------|------|

| 06H  | ALC Mode Control 1 | 0  | 0  | ZELMN | ALC | FR  | LMTH | RATT | LMAT |

|      | R/W                | RD | RD | R/W   | R/W | R/W | R/W  | R/W  | R/W  |

|      | Default            | 0  | 0  | 1     | 0   | 1   | 0    | 0    | 0    |

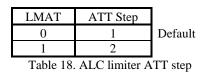

LMAT: ALC Limiter ATT step (see Table 18)

During the ALC limiter operation, when either Lch or Rch exceeds the ALC limiter detection level set by LMTH bit, the number of steps attenuated from the current IPGA value is set. For example, when the current IPGA value is 94H and the LMAT bit = "1", the IPGA transition to 92H when the ALC limiter operation starts, resulting in the input signal level being attenuated by 1dB (=0.5dB x 2).

RATT: ALC Recovery gain step (see Table 19)

During the ALC recovery operation, the number of steps changed from the current IPGA value is set. For example, when the current IPGA value is 82H and RATT bit = "1" is set, the IPGA changes to 84H by the ALC recovery operation and the output signal level is gained up by 1dB (=0.5dB x 2). When the IPGA value exceeds the reference level (REF7-0 bits), the IPGA value does not increase.

| RATT     | Gain Step                        |         |  |  |  |  |  |  |

|----------|----------------------------------|---------|--|--|--|--|--|--|

| 0        | 1                                | Default |  |  |  |  |  |  |

| 1        | 2                                |         |  |  |  |  |  |  |

| Table 10 | Table 10 ALC resources gain stan |         |  |  |  |  |  |  |

Table 19. ALC recovery gain step

LMTH: ALC Limiter detection level / Recovery waiting counter reset level (see Table 20) The ALC limiter detection level and the ALC recovery counter reset level may be offset by about ±2dB.

| LMTH | ALC Limiter Detection Level | ALC Recovery Waiting Counter Reset Level | ]       |

|------|-----------------------------|------------------------------------------|---------|

| 0    | ALC Output ≥ −0.5dBFS       | $-0.5$ dBFS > ALC Output $\ge -2.5$ dBFS | Default |

| 1    | ALC Output $\geq -2.0$ dBFS | $-2.0$ dBFS > ALC Output $\ge -4.0$ dBFS |         |

Table 20. ALC Limiter detection level / Recovery waiting counter reset level

FR: ALC fast recovery

0 : Disable

1 : Enable (Default)

When the impulse noise is input, the ALC recovery operation becomes faster than a normal recovery operation.

ALC: ALC enable flag

0 : ALC Disable (Default) 1 : ALC Enable

ZELMN: Zero crossing enable flag at ALC limiter operation

0 : Enable

1 : Disable (Default)

When the ZELMN bit = "0", the IPGA of each L/R channel perform a zero crossing or timeout independently. The zero crossing timeout is the same as the ALC recovery operation. When the ZELMN bit = "1", the IPGA value is changed immediately. The ALC Limiter period can be set up by a ZTM 1-0 bits when ZELMN bit = "0", it can be set up by a LTM1-0 bits when ZELMN bit = "1"

| Addr | Register Name      | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|------|--------------------|------|------|------|------|------|------|------|------|

| 07H  | ALC Mode Control 2 | REF7 | REF6 | REF5 | REF4 | REF3 | REF2 | REF1 | REF0 |

|      | R/W                | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

|      | Default            | 1    | 0    | 0    | 0    | 1    | 1    | 1    | 0    |

REF7-0: Reference value at ALC recovery operation (see Table 21)

During the ALC recovery operation, if the IPGA value exceeds the setting reference value by gain operation, then the IPGA does not become larger than the reference value.

The REF7-0 bits should not be set up except for Table 21.

| 1       |           |            |

|---------|-----------|------------|

|         | Gain (dB) | DATA (hex) |

|         | +18.0     | A4H        |

|         | :         | :          |

|         | +8.0      | 90H        |

|         | +7.5      | 8FH        |

| Default | +7.0      | 8EH        |

|         | +6.5      | 8DH        |

|         | :         | :          |

|         | +4.5      | 89H        |

|         | :         | :          |

| ]       | +0.5      | 81H        |

| ]       | 0         | 80H        |

| -       |           |            |

Table 21. Reference value at ALC recovery operation

| Addr | Register Name    | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

|------|------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 08H  | Lch DATT Control | ATTL7 | ATTL6 | ATTL5 | ATTL4 | ATTL3 | ATTL2 | ATTL1 | ATTL0 |

| 09H  | Rch DATT Control | ATTR7 | ATTR6 | ATTR5 | ATTR4 | ATTR3 | ATTR2 | ATTR1 | ATTR0 |

|      | R/W              | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

|      | Default          | 0     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

ATTL/R7-0: Digital output volume control (see Table 11) Initial value is "7FH".

The data must not be written over 90H.

When PDN pin = "L", ATTL/R7-0 bits are initialized "7FH". When PWN bit = "0", the DATT holds the last setting value.

| Addr | Register Name           | D7    | D6    | D5    | D4    | D3    | D2    | D1   | D0   |

|------|-------------------------|-------|-------|-------|-------|-------|-------|------|------|

| 0AH  | Lch Peak Hold Low Byte  | PHL7  | PHL6  | PHL5  | PHL4  | PHL3  | PHL2  | PHL1 | PHL0 |

| 0BH  | Lch Peak Hold High Byte | PHL15 | PHL14 | PHL13 | PHL12 | PHL11 | PHL10 | PHL9 | PHL8 |

| 0CH  | Rch Peak Hold Low Byte  | PHR7  | PHR6  | PHR5  | PHR4  | PHR3  | PHR2  | PHR1 | PHR0 |

| 0DH  | Rch Peak Hold High Byte | PHR15 | PHR14 | PHR13 | PHR12 | PHR11 | PHR10 | PHR9 | PHR8 |

|      | R/W                     | RD    |       |       |       |       |       |      |      |

|      | Default                 | 0 0   |       |       | 0     | 0     | 0     | 0    | 0    |

PHL15-0: Lch Peak Hold Low/High Byte

PHR15-0: Rch Peak Hold Low/High Byte

The AK5366 includes the peak hold circuit. The peak is held L/R audio data independently. These registers are reset by reading 8bit of MSB, reading 8bit of both MSB and LSB should be continuity controlled by reading in order of 8bit of MSB from LSB. After reading 8bit of LSB the last, 8bit of MSB is lost by reading 8bit of LSB the last. The output value is the absolute value. Full scale is "FFFFH".

These registers are reset by PDN pin = "L" or PWN bit = "0".