Data Sheet May 2003 FN2896.5

# 600MHz, Very High Slew Rate Operational Amplifier

The Intersil HA-2539 represents the ultimate in high slew rate, wideband, monolithic operational amplifiers. It has been designed and constructed with the Intersil High Frequency Bipolar Dielectric Isolation process and features dynamic parameters never before available from a truly differential device.

With a  $600V/\mu s$  slew rate and a 600MHz gain bandwidth product, the HA-2539 is ideally suited for use in video and RF amplifier designs, in closed loop gains of 10 or greater. Full  $\pm 10V$  swing coupled with outstanding AC parameters and complemented by high open loop gain makes the devices useful in high speed data acquisition systems.

For further design assistance please refer to Application Note AN541 (Using the HA-2539 Very High Slew Rate Wideband Operational Amplifiers) and Application Note AN556 (Thermal Safe-Operating-Areas For High Current Operational Amplifiers.

For military grade product information, the HA-2539/883 data sheet is available upon request.

### Part Number Information

| PART NUMBER | TEMP.<br>RANGE (°C) | PACKAGE    | PKG. NO. |

|-------------|---------------------|------------|----------|

| HA3-2539-5  | 0 to 75             | 14 Ld PDIP | E14.3    |

#### **Features**

| • Very High Slew Rate 600V/µs               |

|---------------------------------------------|

| Open Loop Gain                              |

| • Wide Gain-Bandwidth (AV $\geq$ 10) 600MHz |

| Power Bandwidth 9.5MHz                      |

| Low Offset Voltage                          |

| • Input Voltage Noise 6nV/\(\sqrt{Hz}\)     |

| Output Voltage Swing                        |

|                                             |

# **Applications**

- Pulse and Video Amplifiers

- · Wideband Amplifiers

- · High Speed Sample-Hold Circuits

· Monolithic Bipolar Dielectric Construction

RF Oscillators

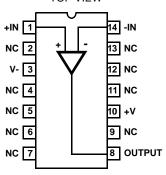

### **Pinout**

#### HA-2539 (PDIP) TOP VIEW

NOTE: No-Connection (NC) leads may be tied to a ground plane for better isolation and heat dissipation.

### **Absolute Maximum Ratings**

| Supply Voltage Between V+ and V- Terminals | 35V  |

|--------------------------------------------|------|

| Differential Input Voltage                 | . 6V |

| Peak Output Current                        | 0mA  |

| Continuous Output Current                  | DMC  |

### **Operating Conditions**

| Temperature Range |             |

|-------------------|-------------|

| HA-2539-5         | 0°C to 75°C |

### **Thermal Information**

| Thermal Resistance (Typical, Note 2)    | $\theta_{JA}$ (oC/W) | $\theta_{JC}$ (oC/W)                   |

|-----------------------------------------|----------------------|----------------------------------------|

| PDIP Package                            | 95                   | N/A                                    |

| Maximum Internal Quiescent Power Dissip | oation (Note         | 1)                                     |

| Maximum Junction Temperature (Plastic F | Package)             | 150 <sup>o</sup> C                     |

| Maximum Storage Temperature Range       | 6                    | 5 <sup>0</sup> C to 150 <sup>0</sup> C |

| Maximum Lead Temperature (Soldering 1   | 0s)                  | 300 <sup>o</sup> C                     |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- Maximum power dissipation with load conditions must be designed to maintain the maximum junction temperature below 150°C for the plastic package. By using Application Note AN556 on Safe Operating Area equations, along with the thermal resistances, proper load conditions can be determined. Heat sinking is recommended above 75°C.

- 2. θJA is measured with the component mounted on a low effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

### **Electrical Specifications** V<sub>SUPPLY</sub> = ±15V, R<sub>L</sub> = 1kW, C<sub>L</sub> < 10pF, Unless Otherwise Specified

| PARAMETER                                                           | TEMP.<br>(°C) | MIN   | ТҮР | MAX | UNITS              |

|---------------------------------------------------------------------|---------------|-------|-----|-----|--------------------|

| INPUT CHARACTERISTICS                                               | <b>'</b>      |       | ı   | 1   |                    |

| Offset Voltage                                                      | 25            | -     | 8   | 15  | mV                 |

|                                                                     | Full          | -     | 13  | 20  | mV                 |

| Average Offset Voltage Drift                                        | Full          | -     | 20  | -   | μV/ <sup>o</sup> C |

| Bias Current                                                        | 25            | -     | 5   | 20  | μА                 |

|                                                                     | Full          | -     | -   | 25  | μА                 |

| Offset Current                                                      | 25            | -     | 1   | 6   | μА                 |

|                                                                     | Full          | -     | -   | 8   | μА                 |

| Input Resistance                                                    | 25            | -     | 10  | -   | kΩ                 |

| Input Capacitance                                                   | 25            | -     | 1   | -   | pF                 |

| Common Mode Range                                                   | Full          | ±10.0 | -   | -   | V                  |

| Input Current Noise<br>(f = 1kHz, R <sub>SOURCE</sub> = $0\Omega$ ) | 25            | -     | 6   | -   | pA√Hz              |

| Input Voltage Noise (f = 1kHz, $R_{SOURCE} = 0\Omega$ )             | 25            | -     | 6   | -   | nV/√Hz             |

| TRANSFER CHARACTERISTICS                                            |               | 1     | 1   | 1   |                    |

| Large Signal Voltage Gain                                           | 25            | 10    | 15  | -   | kV/V               |

| (Note 3)                                                            | Full          | 5     | -   |     | kV/V               |

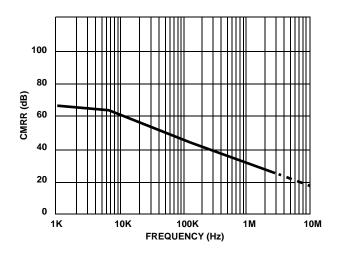

| Common Mode Rejection Ratio<br>(Note 4)                             | Full          | 60    | 72  | -   | dB                 |

| Minimum Stable Gain                                                 | 25            | 10    | -   | -   | V/V                |

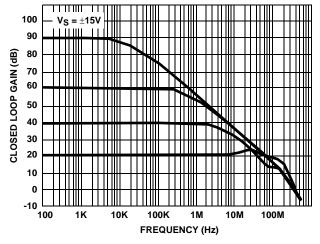

| Gain Bandwidth (Notes 5, 6)                                         | 25            | -     | 600 | -   | MHz                |

# $\textbf{Electrical Specifications} \hspace{0.5cm} V_{SUPPLY} = \pm 15 \text{V}, \hspace{0.1cm} R_L = 1 \text{kW}, \hspace{0.1cm} C_L < 10 \text{pF}, \hspace{0.1cm} \text{Unless Otherwise Specified} \hspace{0.1cm} \textbf{(Continued)}$

| PARAMETER                             | TEMP.<br>(°C) | MIN   | TYP | MAX | UNITS |  |  |

|---------------------------------------|---------------|-------|-----|-----|-------|--|--|

| OUTPUT CHARACTERISTICS                |               |       |     |     |       |  |  |

| Output Voltage Swing (Notes 3, 10)    | Full          | ±10.0 | -   | -   | V     |  |  |

| Output Current (Note 3)               | 25            | ±10   | ±20 | -   | mA    |  |  |

| Output Resistance                     | 25            | -     | 30  | -   | Ω     |  |  |

| Full Power Bandwidth (Notes 3, 7)     | 25            | 8.7   | 9.5 | -   | MHz   |  |  |

| TRANSIENT RESPONSE (Note 8)           |               |       |     |     |       |  |  |

| Rise Time                             | 25            | -     | 7   | -   | ns    |  |  |

| Overshoot                             | 25            | -     | 15  | -   | %     |  |  |

| Slew Rate                             | 25            | 550   | 600 | -   | V/µs  |  |  |

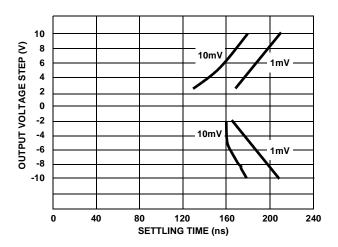

| Settling Time: 10V Step to 0.1%       | 25            | -     | 180 | -   | ns    |  |  |

| POWER REQUIREMENTS                    |               |       |     |     |       |  |  |

| Supply Current                        | Full          | -     | 20  | 25  | mA    |  |  |

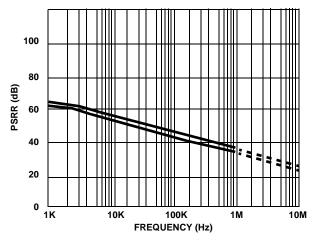

| Power Supply Rejection Ratio (Note 9) | Full          | 60    | 70  | -   | dB    |  |  |

### NOTES:

- 3.  $R_L = 1k\Omega$ ,  $V_O = \pm 10V$ .

- 4.  $V_{CM} = \pm 10.0V$ .

- 5.  $V_O = 90 \text{mV}$ .

- 6.  $A_V = 10$ .

- 6.  $A_V$  = 10. 7. Full Power Bandwidth guaranteed based on slew rate measurement using: FPBW =  $\frac{\text{Slew Rate}}{2\pi V_{\text{PEAK}}}$

- 8. Refer to Test Circuits section of data sheet.

- 9.  $V_{SUPPLY} = +5V$ , -15V and +15V, -5V.

- 10. Guaranteed range for output voltage is  $\pm 10V$ . Functional operation outside of this range is not guaranteed.

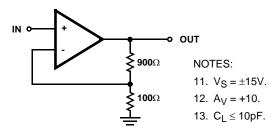

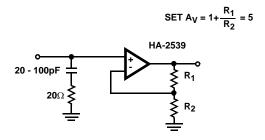

### Test Circuits and Waveforms

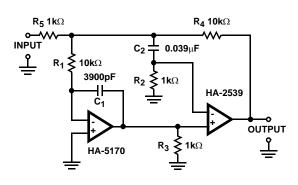

FIGURE 1. TEST CIRCUIT

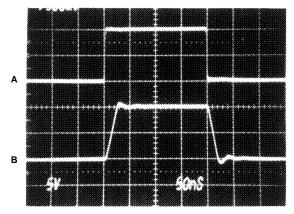

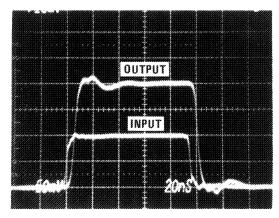

Vertical Scale: A = 0.5V/Div., B = 5.0V/Div.

Horizontal Scale: 50ns/Div.

FIGURE 2. LARGE SIGNAL RESPONSE

Vertical Scale: Input = 10mV/Div., Output = 50mV/Div. Horizontal Scale: 20ns/Div.

FIGURE 3. SMALL SIGNAL RESPONSE

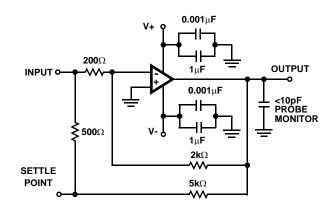

### NOTES:

- 14.  $A_V = -10$ .

- 15. Load Capacitance should be less than 10pF.

- 16. It is recommended that resistors be carbon composition and that feedback and summing network ratios be matched to 0.1%.

- 17. SETTLE POINT (Summing Node) capacitance should be less than 10pF. For optimum settling time results, it is recommended that the test circuit be constructed directly onto the device pins. A Tektronix 568 Sampling Oscilloscope with S-3A sampling heads is recommended as a settle point monitor.

FIGURE 4. SETTLING TIME CIRCUIT

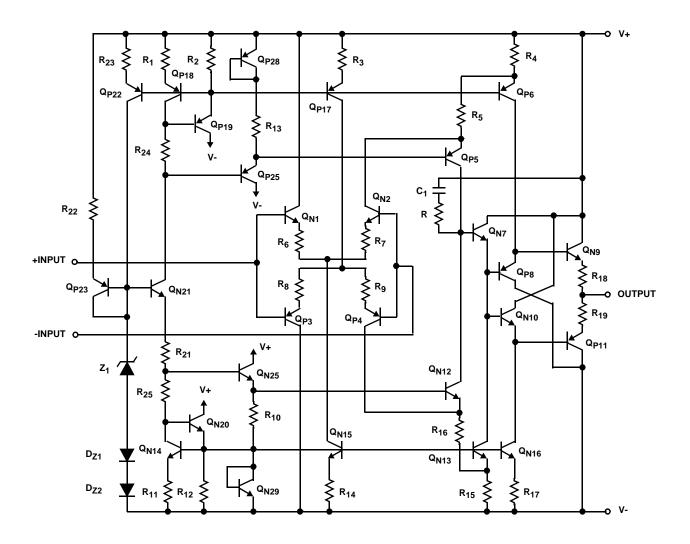

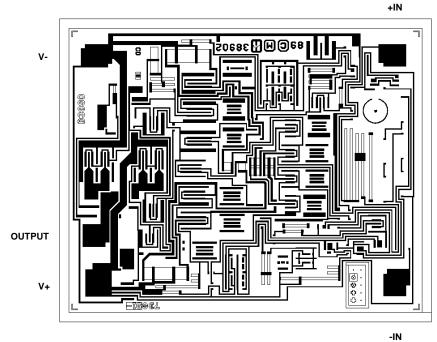

# Schematic Diagram

# **Typical Applications**

FIGURE 5. FREQUENCY COMPENSATION BY OVERDAMPING

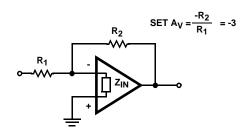

FIGURE 6. STABILIZATION USING  $Z_{\text{IN}}$

FIGURE 7. REDUCING DC ERRORS; COMPOSITE AMPLIFIER

FIGURE 8. DIFFERENTIAL GAIN ERROR (3%) HA-2539 20dB VIDEO GAIN BLOCK

# **Typical Performance Curves**

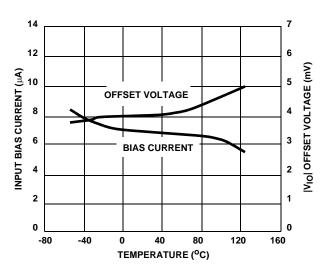

FIGURE 9. INPUT OFFSET VOLTAGE AND BIAS CURRENT vs TEMPERATURE

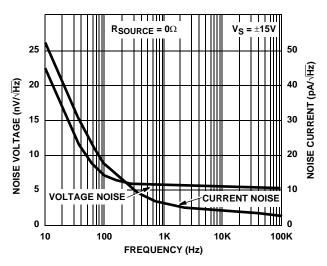

FIGURE 10. INPUT NOISE VOLTAGE AND NOISE CURRENT vs FREQUENCY

# Typical Performance Curves (Continued)

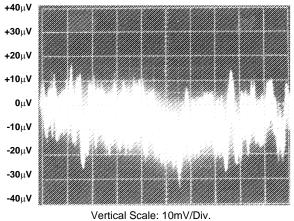

Horizontal Scale: 50ms/Div.

FIGURE 11. BROADBAND NOISE (0.1Hz TO 1MHz)

FIGURE 13. POWER SUPPLY REJECTION RATIO vs FREQUENCY

FIGURE 15. CLOSED LOOP FREQUENCY RESPONSE

FIGURE 12. COMMON MODE REJECTION RATIO vs FREQUENCY

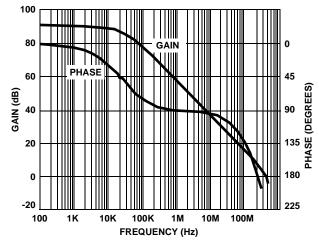

FIGURE 14. OPEN LOOP GAIN/PHASE vs FREQUENCY

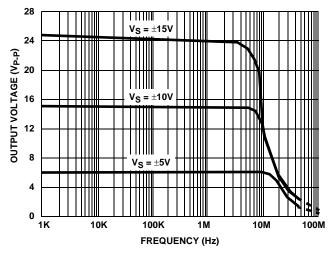

FIGURE 16. OUTPUT VOLTAGE SWING vs FREQUENCY

# Typical Performance Curves (Continued)

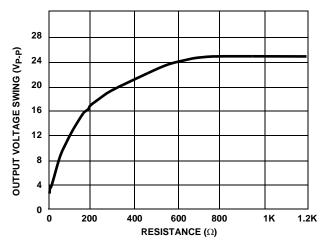

FIGURE 17. OUTPUT VOLTAGE SWING vs LOAD RESISTANCE

FIGURE 19. SETTLING TIME FOR VARIOUS OUTPUT STEP VOLTAGES

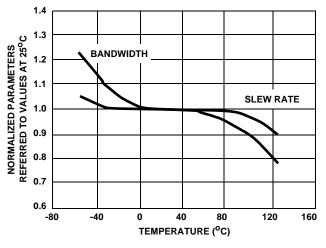

FIGURE 18. NORMALIZED AC PARAMETERS vs TEMPERATURE

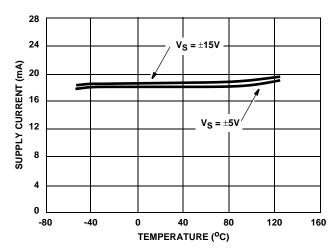

FIGURE 20. POWER SUPPLY CURRENT vs TEMPERATURE

# Die Characteristics

### **DIE DIMENSIONS:**

62 mils x 76 mils x 19 mils 1575μm x 1930μm x 483μm

### **METALLIZATION:**

Type: Al, 1% Cu Thickness: 16kÅ ±2kÅ

### **PASSIVATION:**

Type: Nitride (Si<sub>3</sub>N<sub>4</sub>) over Silox (SiO<sub>2</sub>, 5% Phos.)

Silox Thickness: 12kÅ ±2kÅ Nitride Thickness: 3.5kÅ ±1.5kÅ

# Metallization Mask Layout

### SUBSTRATE POTENTIAL (POWERED UP):

V-

### TRANSISTOR COUNT:

30

# PROCESS:

Bipolar Dielectric Isolation

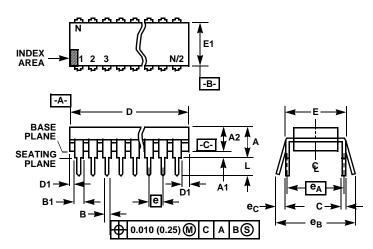

# Dual-In-Line Plastic Packages (PDIP)

#### NOTES:

- Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

- Dimensions A, A1 and L are measured with the package seated in JEDEC seating plane gauge GS-3.

- D, D1, and E1 dimensions do not include mold flash or protrusions.

Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

- E and e<sub>A</sub> are measured with the leads constrained to be perpendicular to datum -C-.

- e<sub>B</sub> and e<sub>C</sub> are measured at the lead tips with the leads unconstrained. e<sub>C</sub> must be zero or greater.

- 8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).

- 9. N is the maximum number of terminal positions.

- Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

E14.3 (JEDEC MS-001-AA ISSUE D)

14 LEAD DUAL-IN-LINE PLASTIC PACKAGE

|                | INCHES MILLIMETERS |           |          |          |       |

|----------------|--------------------|-----------|----------|----------|-------|

| SYMBOL         | MIN                | MAX       | MIN      | MAX      | NOTES |

| Α              | -                  | 0.210     | -        | 5.33     | 4     |

| A1             | 0.015              | =         | 0.39     | -        | 4     |

| A2             | 0.115              | 0.195     | 2.93     | 4.95     | -     |

| В              | 0.014              | 0.022     | 0.356    | 0.558    | -     |

| B1             | 0.045              | 0.070     | 1.15     | 1.77     | 8     |

| С              | 0.008              | 0.014     | 0.204    | 0.355    | -     |

| D              | 0.735              | 0.775     | 18.66    | 19.68    | 5     |

| D1             | 0.005              | -         | 0.13     | -        | 5     |

| Е              | 0.300              | 0.325     | 7.62     | 8.25     | 6     |

| E1             | 0.240              | 0.280     | 6.10     | 7.11     | 5     |

| е              | 0.100 BSC          |           | 2.54 BSC |          | -     |

| e <sub>A</sub> | 0.300              | 0.300 BSC |          | 7.62 BSC |       |

| e <sub>B</sub> | -                  | 0.430     | -        | 10.92    | 7     |

| L              | 0.115              | 0.150     | 2.93     | 3.81     | 4     |

| N              | 14                 |           | 14       |          | 9     |

Rev. 0 12/93

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.