#### Typical Applications

The is suitable for:

- SONET, Fibre Channel, GigE Clock Distribution

- ADC/DAC Clock Distribution

- · Low Skew and Jitter Clock or Data Fanout

- Wireless/Wired Communications

- Level Translation

- High Performance Instrumentation

- Medical Imaging

- Single-Ended to Differential Conversion

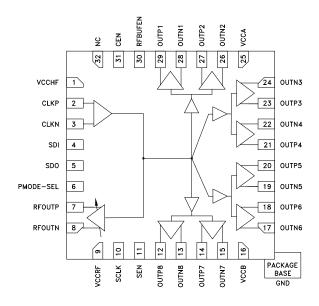

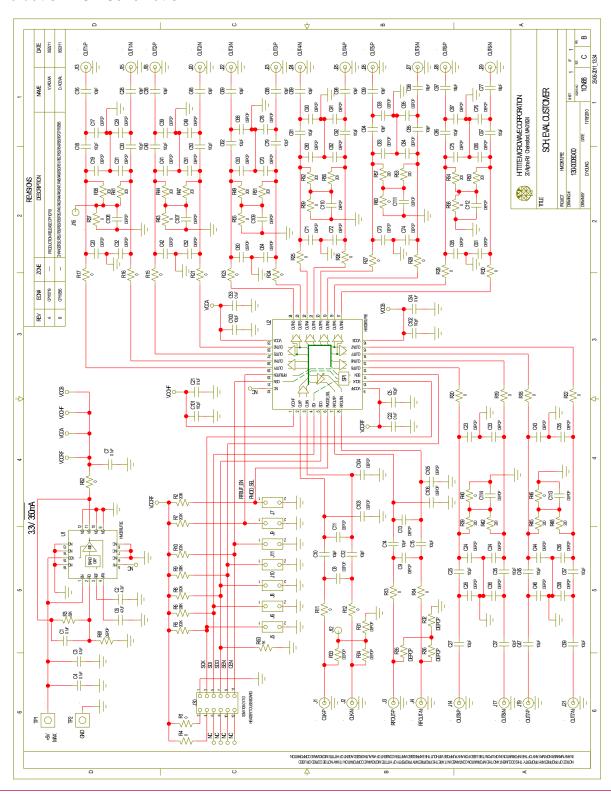

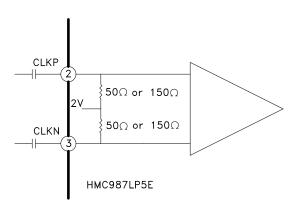

#### **Functional Diagram**

#### **Features**

Ultra Low Noise Floor: -166 dBc/Hz @ 2 GHz Wideband: DC - 8 GHz Operating Frequency Flexible Input Interface:

LVPECL, LVDS, CML, CMOS Compatible

AC or DC Coupling

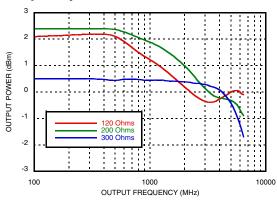

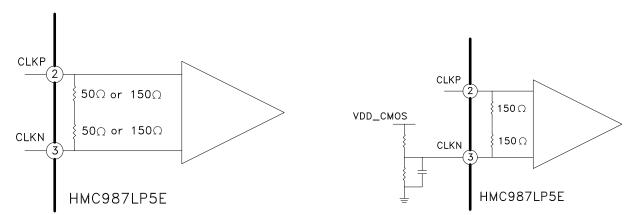

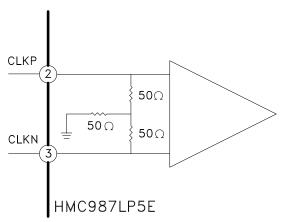

On-Chip Termination 50 or 150  $\Omega$  (100/300  $\Omega$  Diff.)

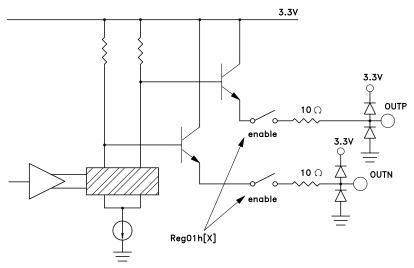

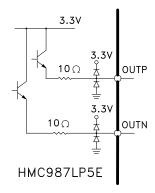

Multiple Output Drivers:

Up to 8 Differential or 16 Single-Ended LVPECL Outputs:

800 mVpp into 50 Ω Single-Ended (+3 dBm Fo)

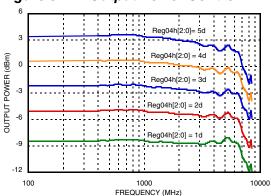

One Adjustable Power CML/RF Output:

-9 to 3 dBm Single-Ended

Serial or Parallel Control, Hardware Chip-Enable

Power-Down Current < 1 uA

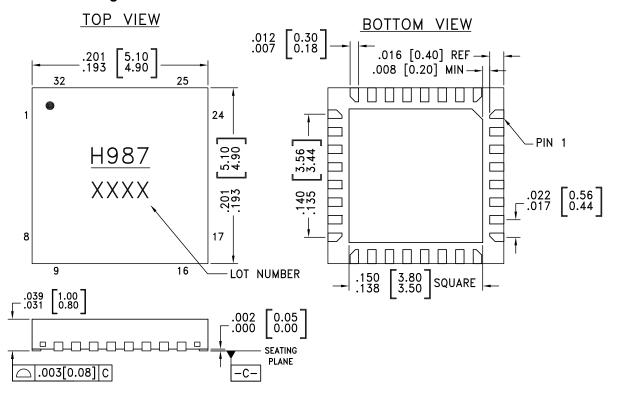

32 Lead 5x5 mm SMT Package 25 mm<sup>2</sup>

#### **General Description**

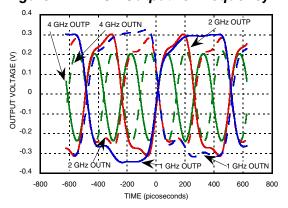

The 1-to-9 fanout buffer is designed for low noise clock distribution. It is intended to generate relatively square wave outputs with rise/fall times < 100 ps. The low skew and jitter outputs of the HMC987LP5E, combined with its fast rise/fall times, leads to controllable low-noise switching of downstream circuits such as mixers, ADCs/DACs or SERDES devices. The noise floor is particularly important in these applications, when the clock-network bandwidth is wide enough to allow square-wave switching. Driven at 2 GHz, outputs of the HMC987LP5E have a noise floor of -166 dBc/Hz, corresponding to a jitter density of 0.6 asec/rtHz - or 50 fs over an 8 GHz bandwidth.

The input stage can be driven single-ended or differentially, in a variety of signal formats (CML, LVDS, LVPECL or CMOS), AC or DC coupled. The input stage also features adjustable input impedance. It has 8 LVPECL outputs, and 1 CML output with adjustable swing/power-level in 3 dB steps.

Individual output stages may be enabled or disabled for power-savings when not required using either hardware control pins, or under control of a serial-port interface.

#### Table 1. Electrical Specifications

Unless otherwise specified: T = 27 °C, Regulated VDD of 3.3 V, 2 GHz, 6 dBm in, AC coupled single ended input and output, 120  $\Omega$ /leg DC termination, AC coupled into 50  $\Omega$  measuring load. Effects of customer eval board ("Evaluation PCB Schematic") are de-embedded. For convenience, all voltages are referenced to GND (0V), but negative supply references are acceptable.

| Parameter                                                             | Conditions                                                      | Min.      | Тур.      | Max.      | Units |

|-----------------------------------------------------------------------|-----------------------------------------------------------------|-----------|-----------|-----------|-------|

| DC Input Characteristics                                              |                                                                 |           |           |           | •     |

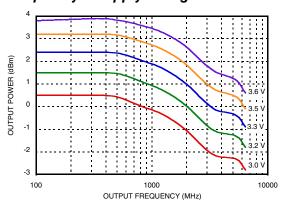

| VDD (VCCHF=VCCA=VCCB=VCCRF)                                           |                                                                 | 3.0       | 3.3       | 3.6       | V     |

| Input Common Mode Voltage                                             |                                                                 | 1.35      | 2         | VDD - 0.2 | V     |

| Input Swing (Single Ended)                                            |                                                                 | 0.2       |           | 2         | Vpp   |

| Input Capacitance                                                     |                                                                 |           | 0.5       |           | pF    |

| Input Impedance                                                       |                                                                 |           |           |           |       |

| Single-Ended                                                          | Selectable                                                      |           | 50 / 150  |           | Ω     |

| Differential                                                          | Selectable                                                      |           | 100 / 300 |           | Ω     |

| Input Bias Current                                                    | Base current under external DC bias, Internal termination open. |           | 165       |           | μА    |

| Logic Inputs                                                          |                                                                 |           |           |           |       |

| Switching Threshold (Vsw)                                             | VIH/VIL within 50 mV of Vsw                                     | 38        | 47        | 54        | %VDD  |

| LVPECL DC Output Characteristics                                      |                                                                 |           |           |           |       |

| Output Voltage High Level                                             | @ 3.3 V = 2.25                                                  | VDD - 1.2 | VDD - 1.0 | VDD - 0.8 | V     |

| Ouput Voltage Common Mode                                             | @ 3.3 V = 1.82                                                  | VDD - 1.7 | VDD - 1.5 | VDD - 1.3 | V     |

| Output Voltage Low Level                                              | @ 3.3 V = 1.42                                                  | VDD - 2.1 | VDD - 1.9 | VDD - 1.7 | V     |

| Output Voltage, Single-Ended                                          | Output Voltage, Single-Ended                                    |           | 800       |           | mVpp  |

| AC Performance                                                        |                                                                 |           |           |           |       |

| Input/Output Frequency [1]                                            | > 400 Vpp single-ended                                          | DC        |           | 8000      | MHz   |

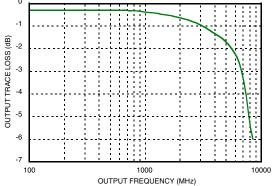

| 3 dB Bandwidth                                                        |                                                                 |           | 4000      |           | MHz   |

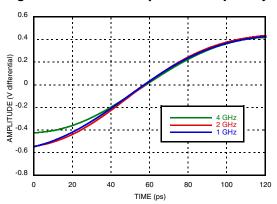

| Output Rise/Fall Time                                                 | 20% to 80%                                                      |           | 65        |           | ps    |

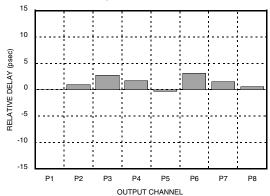

| Typical Channel Skew  Across all LVPECL outputs relative to channel 1 |                                                                 | 0         | 1.5       | 3.1       | ps    |

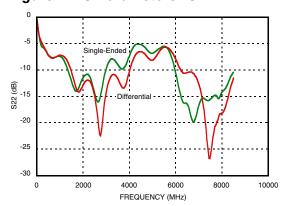

| Small Signal Gain S21                                                 |                                                                 |           |           |           |       |

| 1000 MHz                                                              |                                                                 |           | 26        |           | dB    |

| 4000 MHz                                                              |                                                                 |           | 15        |           | dB    |

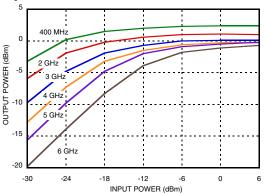

| Input P1dB                                                            |                                                                 |           |           |           |       |

| 1000 MHz                                                              |                                                                 |           | -20       |           | dBm   |

| 4000 MHz                                                              | 4000 MHz                                                        |           | -10       |           | dBm   |

| Saturated Power in fundamental tone (Sing                             | gle-Ended)                                                      |           |           |           |       |

| 1000 MHz                                                              |                                                                 |           | 2.5       |           | dBm   |

| 4000 MHz                                                              |                                                                 |           | -0.5      |           | dBm   |

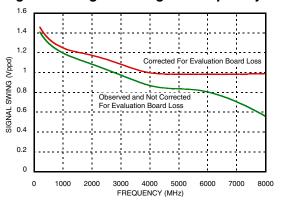

| Output Voltage Swing (Vppd into 100 $\Omega$ )                        |                                                                 |           |           |           |       |

| 700 MHz                                                               |                                                                 | 1.5       | 1.6       | 1.7       | V     |

| 2000 MHz                                                              |                                                                 | 1.2       | 1.3       | 1.4       | V     |

<sup>[1]</sup> For frequencies < 700 MHz, square wave signals should be used to maintain high quality phase noise performance.

Table 1. Electrical Specifications (Continued...)

| Parameter                        | Conditions        | Min. | Тур. | Max. | Units    |

|----------------------------------|-------------------|------|------|------|----------|

| 4000 MHz                         |                   | 1.1  | 1.2  | 1.3  | V        |

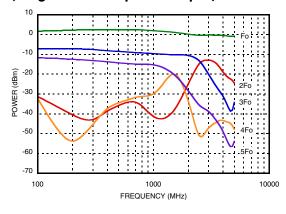

| Harmonics                        |                   |      |      |      |          |

| Fo                               |                   |      | 2    |      | dBm      |

| 2Fo                              |                   |      | -25  |      | dBc      |

| 3Fo                              |                   |      | -8   |      | dBc      |

| 4Fo                              |                   |      | -28  |      | dBc      |

| 5Fo                              |                   |      | -12  |      | dBc      |

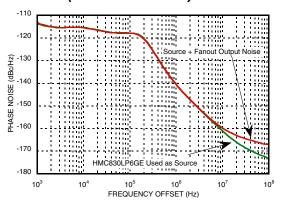

| SSB Phase Noise at 100 Hz Offset |                   |      |      |      |          |

| 622.08 MHz Carrier Frequency     |                   |      | -147 |      | dBc/Hz   |

| 1750 MHz Carrier Frequency       |                   |      | -147 |      | dBc/Hz   |

| 4000 MHz Carrier Frequency       |                   |      | -147 |      | dBc/Hz   |

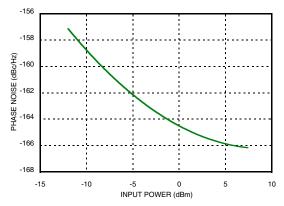

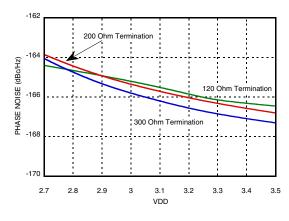

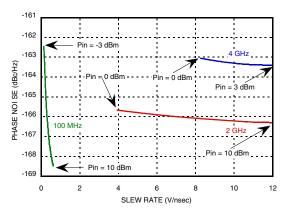

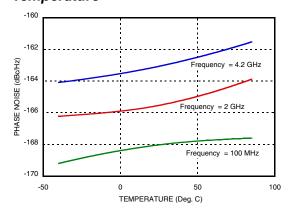

| SSB Phase Noise Floor [2]        |                   |      | 1    |      |          |

| 100 MHz Carrier Frequency        |                   |      | -167 |      | dBc/Hz   |

| 622.08 MHz Carrier Frequency     |                   |      | -167 |      | dBc/Hz   |

| 1750 MHz Carrier Frequency       |                   |      | -166 |      | dBc/Hz   |

| 2000 MHz Carrier Frequency       |                   |      | -166 |      | dBc/Hz   |

| 4000 MHz Carrier Frequency       |                   |      | -163 |      | dBc/Hz   |

| 4200 MHz Carrier Frequency       |                   |      | -162 |      | dBc/Hz   |

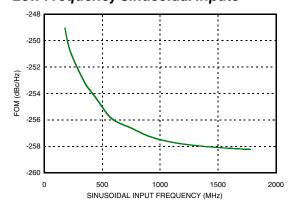

| Floor Jitter Density             |                   |      |      |      |          |

| 622.08 MHz Carrier Frequency     |                   |      | 1.8  |      | asec/√Hz |

| 1750 MHz Carrier Frequency       |                   |      | 0.7  |      | asec/√Hz |

| 4000 MHz Carrier Frequency       |                   |      | 0.5  |      | asec/√Hz |

| Integrated RMS Jitter            |                   |      |      |      |          |

|                                  | 100 Hz to 100 MHz |      | 17   |      | fs rms   |

|                                  | 12 kHz to 20 MHz  |      | 8    |      | fs rms   |

| 622.08 MHz Carrier Frequency     | 20 kHz to 80 MHz  |      | 17   |      | fs rms   |

|                                  | 50 kHz to 80 MHz  |      | 17   |      | fs rms   |

|                                  | 4 MHz to 80 MHz   |      | 16   |      | fs rms   |

|                                  | 100 Hz to 100 MHz |      | 7    |      | fs rms   |

|                                  | 12 kHz to 20 MHz  |      | 3    |      | fs rms   |

| 1750 MHz Carrier Frequency       | 20 kHz to 80 MHz  |      | 6    |      | fs rms   |

|                                  | 50 kHz to 80 MHz  |      | 6    |      | fs rms   |

|                                  | 4 MHz to 80 MHz   |      | 6    |      | fs rms   |

|                                  | 100 Hz to 100 MHz |      | 4    |      | fs rms   |

|                                  | 12 kHz to 20 MHz  |      | 2    |      | fs rms   |

| 4000 MHz Carrier Frequency       | 20 kHz to 80 MHz  |      | 4    |      | fs rms   |

|                                  | 50 kHz to 80 MHz  |      | 4    |      | fs rms   |

|                                  | 4 MHz to 80 MHz   |      | 4    |      | fs rms   |

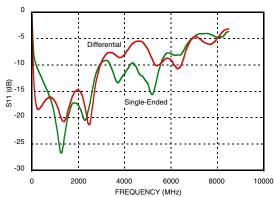

| Output Return Loss               | 500 MHz to 4 GHz  | -16  | -12  | -8   | dB       |

$\cite{CML} \ \ buffer \ has \ similar \ phase \ noise \ characteristics \ at \ maximum \ output \ power \ level.$

Table 1. Electrical Specifications (Continued...)

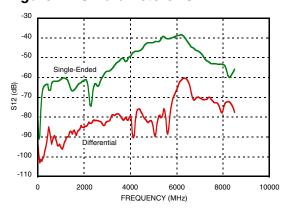

| Isolation   In to Out - Chip Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Off isolation - Relative to Power of neighboring driven port         60         48         0           700 MHz         60         48         0           4000 MHz         50         32         0           Output to Output Isolation with 500 MHz Aggressor Signal Injected into Output Port         To Locally paired output buffer         25         0           To other buffers         45         0           RF Output Buffer         3dB Bandwidth         5000         M           Max Output Power (vs Temperature at 2 GHz)         Single-Ended         3         3.2         dt           Power Control Range (3 dB steps)         Single-Ended         -9         3         dt           Delay Relative to LVPECL Output         -140         p           Power Supply Rejection         FM/Phase Pushing         0.8         p           AM Rejection         7         0         0           Current Consumption (3.3 V Unloaded Outputs)         1         p           Chip Disabled         1         60         m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| To 0 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A000 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Output to Output Isolation with 500 MHz Aggressor Signal Injected into Output Port  To Locally paired output buffer 25 comparison of the paired output buffer 45 comparison output Power (vs Temperature at 2 GHz) Single-Ended 3 comparison output Buffer 45 comparison out |

| To Locally paired output buffer 25 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| To other buffers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ### RF Output Buffer    3 dB Bandwidth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

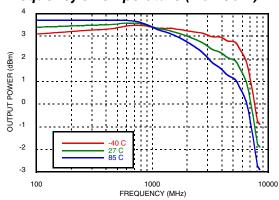

| 3 dB Bandwidth         5000         M           Max Output Power (vs Temperature at 2 GHz)         Single-Ended         3         3.2         df           Power Control Range (3 dB steps)         Single-Ended         -9         3         df           Delay Relative to LVPECL Output         -140         p           Power Supply Rejection         0.8         ps           FM/Phase Pushing         0.8         ps           AM Rejection         7         c           Current Consumption (3.3 V Unloaded Outputs)         1         p           Chip Disabled         1         p           1 Output         60         m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

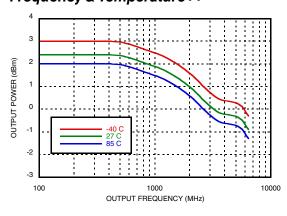

| Max Output Power (vs Temperature at 2 GHz)         Single-Ended         3         3.2         delay           Power Control Range (3 dB steps)         Single-Ended         -9         3         delay           Delay Relative to LVPECL Output         -140         p           Power Supply Rejection         0.8         ps           FM/Phase Pushing         0.8         ps           AM Rejection         7         c           Current Consumption (3.3 V Unloaded Outputs)         1         p           Chip Disabled         1         p           1 Output         60         m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2 GHz) Single-Ended 3 3.2 dt Power Control Range (3 dB steps) Single-Ended -9 3 dt Delay Relative to LVPECL Output -140 p Power Supply Rejection FM/Phase Pushing 0.8 ps AM Rejection 7 ccurrent Consumption (3.3 V Unloaded Outputs) Chip Disabled 1 p 1 Output 60 m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Delay Relative to LVPECL Output         -140         p.           Power Supply Rejection         0.8         ps           FM/Phase Pushing         0.8         ps           AM Rejection         7         c           Current Consumption (3.3 V Unloaded Outputs)         1         ps           Chip Disabled         1         ps           1 Output         60         m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Power Supply Rejection           FM/Phase Pushing         0.8         ps           AM Rejection         7         c           Current Consumption (3.3 V Unloaded Outputs)         1         ps           Chip Disabled         1         ps           1 Output         60         m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| FM/Phase Pushing         0.8         ps           AM Rejection         7         c           Current Consumption (3.3 V Unloaded Outputs)         1         μ           Chip Disabled         1         μ           1 Output         60         m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AM Rejection         7         0           Current Consumption (3.3 V Unloaded Outputs)         1         µ           Chip Disabled         1         0         m           1 Output         60         m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

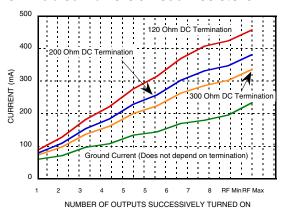

| Current Consumption (3.3 V Unloaded Outputs)           Chip Disabled         1         μ           1 Output         60         m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Chip Disabled         1         μ           1 Output         60         π                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1 Output 60 m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2 Outputs 71 m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3 Outputs 97 m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4 Outputs 108 m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5 Outputs 134 m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6 Outputs 144 m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7 Outputs 170 m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8 Outputs 180 m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8 + RF Buffer (Min to Max Power) 198 234 m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SPI Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Vil 1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Vih 2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

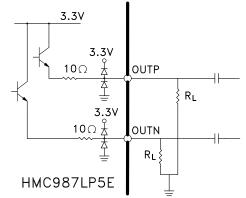

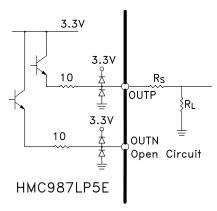

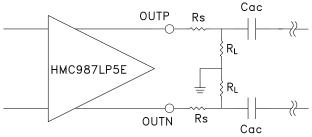

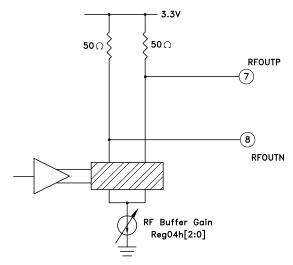

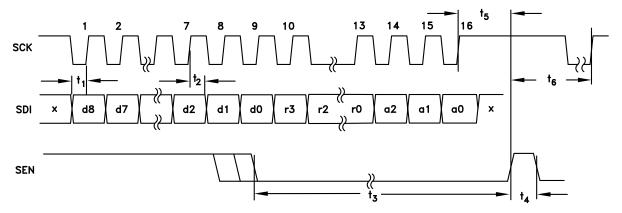

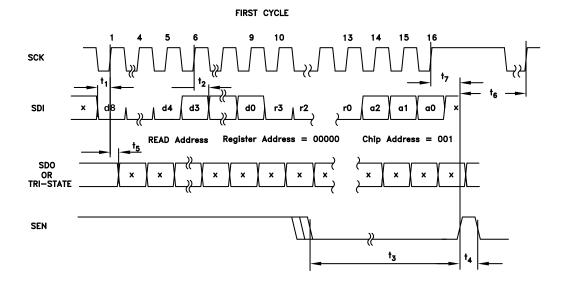

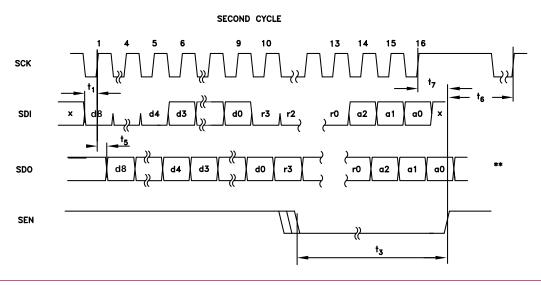

| Vol 0.4 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |