# SPECIFICATIONS FOR LIQUID CRYSTAL DISPLAY

PART NUMBER: AGM2416B

DATE: September 13, 2005

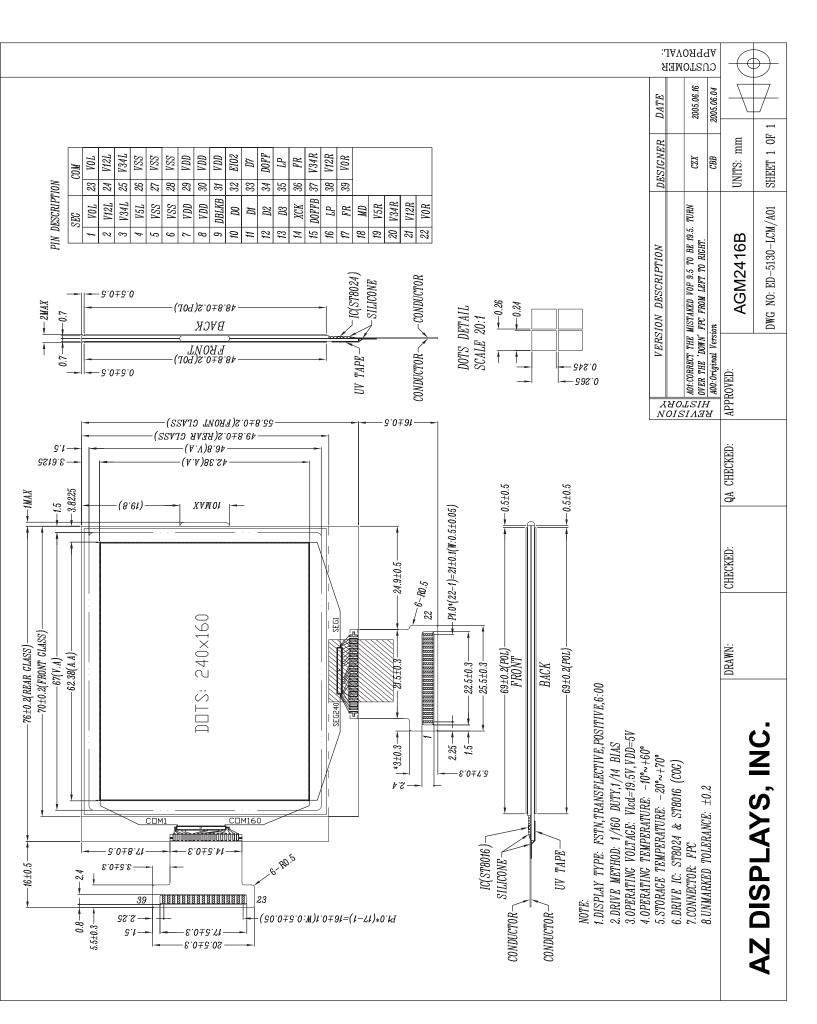

## 1 General Specifications

| Item                       | Standard Value                                                                                                                                        | Unit |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Display Pattern            | ☑Dot-Graphic ☐Character ☐Digits ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐                                                                                 | Dots |

| Color                      | □Mono. □Grayscale ☑ <u>FSTN</u>                                                                                                                       |      |

| Module Dimension           | 92.0 X 71.8 X 2.0                                                                                                                                     | mm   |

| Viewing Area               | 67.0 X 46.8                                                                                                                                           | mm   |

| Active Area                | 62.38 X 42.38                                                                                                                                         | mm   |

| Character Size             | 1                                                                                                                                                     | mm   |

| Character Pitch            | 1                                                                                                                                                     | mm   |

| DOT Size                   | 0.245 X 0.24                                                                                                                                          | mm   |

| DOT Pitch                  | 0.265 X 0.26                                                                                                                                          | mm   |

| LCD Type                   | □TN, Positive □TN, Negative □HTN, Positive □HTN, Negative □STN, Yellow-Green □STN, Gray □STN, Blue □FSTN, Positive □FSTN, Negative □Color STN □FM LCD |      |

| Polarizer Type             | ☑Transflective □Transmissive □Reflective □Anti-Glare                                                                                                  |      |

| View Direction             | ☑6H □12H □                                                                                                                                            |      |

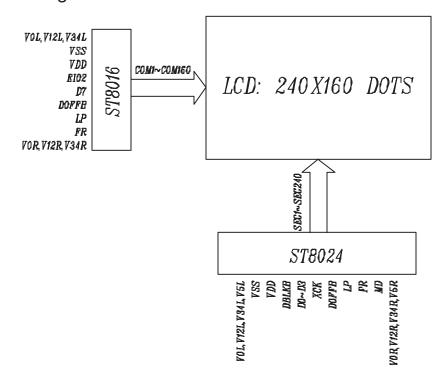

| LCD Controller & Driver    | ST8016 & ST8024                                                                                                                                       |      |

| LCD Driving Method         | 1/160duty, 1/14bias                                                                                                                                   |      |

| Interface Type             | □I <sup>2</sup> C □4-wire Serial □3-wire Serial □6800 □8080 ☑4-bit □                                                                                  |      |

| Backlight Type             | 1                                                                                                                                                     |      |

| Backlight Color            | /                                                                                                                                                     |      |

| EL/CCFL Driver type        | /                                                                                                                                                     |      |

| DC-DC Converter            | □Build-in ☑External                                                                                                                                   |      |

| Operation Temperature (°C) | -10 ~ 60 (T <sub>OPL</sub> – T <sub>OPH</sub> )                                                                                                       | °C   |

| Storage Temperature (°C)   | -20 ~ 70 (T <sub>STL</sub> T <sub>STH</sub> )                                                                                                         | ° C  |

## 3.1 Pin Description

#### Segment Pin

| Pin No. | Symbol | Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V0L    | Bias power supply pins for LCD drive voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2       | V12L   | Normally use the bias voltages set by a resistor divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3       | V34L   | Ensure that voltages are set such that $V_{SS} \cdot V_5 < V_{43} < V_{12} < V_0$ .<br>$V_{i\perp}$ and $V_{iR}$ (i = 0,12, 43, 5) must connect to an external power supply, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4       | V5L    | supply regular voltage which is assigned by specification for each power pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5       | VSS    | Crownd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6       | VSS    | - Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7       | VDD    | Logic power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 8       | VDD    | Logic power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 9       | DBLKB  | Use as contrast control, use PWM signal as input. Connect to V <sub>DD</sub> for no contrast control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10      | D0     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 11      | D1     | - Data bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 12      | D2     | - Data bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 13      | D3     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 14      | XCK    | Clock input pin for taking display data * Data is read at the falling edge of the clock pulse.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 15      | DOFFB  | Control input pin for output of non-select level The input signal is level-shifted from logic voltage level to LCD drive voltage level, and controls the LCD drive circuit. When set to Vss level "L", the LCD drive output pins (Y1-Y240) are set to level Vss. When set to "L", the contents of the line latch are reset, but the display data are read in the data latch regardless of the condition of DISPOFF. When the DISPOFF function is canceled, the driver outputs non-select level (V12 or V43), then outputs the contents of the data latch at the next falling edge of the LP. At that time, if DISPOFF removal time does not correspond to what is shown in AC characteristics, it can not output the reading data correctly. Table of truth values is shown in "TRUTH TABLE" in Functional Operations. |

| 16      | LP     | Latch pulse input pin for display data  Data is latched at the falling edge of the clock pulse.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 17      | FR     | AC signal input pin for LCD drive waveform The input signal is level-shifted from logic voltage level to LCD drive voltage level, and controls the LCD drive circuit. Normally it inputs a frame inversion signal. The LCD drive output pins' output voltage levels can be set using the line latch output signal and the FR signal. Table of truth values is shown in "TRUTH TABLE" in Functional Operations.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 18      | MD     | Mode selection pin When set to Vsslevel "L", 8-bit parallel input mode is set. When set to Vpd level "H", 4-bit parallel input mode is set. Refer to "RELATIONSHIP BETWEEN THE DISPLAY DATA AND LCD DRIVE OUTPUT PINS" in Functional Operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 19      | V5R    | Bias power supply pins for LCD drive voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 20 | V34R | Normally use the bias voltages set by a resistor divider                                                                                                                     |

|----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21 | V12R | Ensure that voltages are set such that $V_{SS} \cdot V_5 < V_{43} < V_{12} < V_0$ .<br>$V_{iL}$ and $V_{iR}$ (i = 0,12, 43, 5) must connect to an external power supply, and |

| 22 | V0R  | supply regular voltage which is assigned by specification for each power pin                                                                                                 |

#### Common Pin

| Pin No. | Symbol | Function Description                                                                                           |

|---------|--------|----------------------------------------------------------------------------------------------------------------|

| 23      | VOL    | Bias power supply pins for LCD drive voltage                                                                   |

| 24      | V12L   | Normally use the bias voltages set by a resistor divider.                                                      |

| 25      |        | Ensure that voltages are set such that Vss < V43 < V12 < V0.                                                   |

|         | V34L   | Vi∟ and ViR (i = 0,12, 43) must connect to an external power supply, and                                       |

|         |        | supply regular voltage that is assigned by specification for each power pin.                                   |

| 26      | VSS    |                                                                                                                |

| 27      | VSS    | Ground                                                                                                         |

| 28      | VSS    |                                                                                                                |

| 29      | VDD    |                                                                                                                |

| 30      | VDD    | Logic power supply                                                                                             |

| 31      | VDD    |                                                                                                                |

| 32      | EIO2   | Shift data input for shift register at common mode                                                             |

| 33      | D7     | Dual mode data input at common mode                                                                            |

| 34      |        | Control input pin for output of non-select level                                                               |

|         |        | The input signal is level-shifted from logic voltage level to LCD drive voltage                                |

|         |        | level, and controls the LCD drive circuit.                                                                     |

|         |        | When set to Vss level "L", the LCD drive output pins (Y1-Y160) are set to level                                |

|         |        | Vss.                                                                                                           |

|         | DOFFB  | When set to "Lit, the contents of the shift register are reset to not reading                                  |

|         |        | data. When the /DISPOFF function is canceled, the driver outputs non-select                                    |

|         |        | level (V <sub>12</sub> or V <sub>43</sub> ), and the shift data is read at the next falling edge of the LP. At |

|         |        | that time, if /DISPOFF removal time does not correspond to what is shown in                                    |

|         |        | AC characteristics, the shift data is not read correctly.                                                      |

|         |        | Table of truth-values is shown in "TRUTH TABLE" in Functional Operations.                                      |

| 35      | LP     | Shift clock pulse input pin for bi-directional shift register                                                  |

|         | LP     | * Data is shifted at the falling edge of the clock pulse.                                                      |

| 36      |        | AC signal input pin for LCD drive waveform                                                                     |

|         |        | The input signal is level-shifted from logic voltage level to LCD drive voltage                                |

|         |        | level, and controls the LCD drive circuit.                                                                     |

|         | FR     | Normally it inputs a frame inversion signal.                                                                   |

|         |        | The LCD drive output pins' output voltage levels can be set using the shift                                    |

|         |        | register output signal and the FR signal.                                                                      |

|         |        | Table of truth-values is shown in "TRUTH TABLE" in Functional Operations.                                      |

| 37      | V34R   | Bias power supply pins for LCD drive voltage                                                                   |

| 38      | V12R   | Normally use the bias voltages set by a resistor divider.                                                      |

| 39      |        | Ensure that voltages are set such that Vss < V43 < V12 < V0.                                                   |

|         | V0R    | V <sub>iL</sub> and V <sub>iR</sub> (i = 0,12, 43) must connect to an external power supply, and               |

|         |        | supply regular voltage that is assigned by specification for each power pin.                                   |

## 3.2 Block Diagram

## 4. Electrical-optical Specifications

#### 4.1 Absolute Maximum Ratings

| PARAMETER           | SYMBOL APPLICABLE PINS RATING |                                                                      | UNIT                          | NOTE |     |

|---------------------|-------------------------------|----------------------------------------------------------------------|-------------------------------|------|-----|

| Supply voltage (1)  | Voo                           | VDD                                                                  | -0.3 to +7.0                  | V    | 1   |

|                     | V <sub>o</sub>                | Vol, Vor                                                             | -0.3 to +45.0                 | V    |     |

| Supply voltage (2)  | V12                           | V12L, V12R                                                           | -0.3 to Vo + 0.3              | V    |     |

| Supply voltage (2)  | V43                           | V43L, V43R                                                           | -0.3 to Vo + 0.3              | V    | 1,2 |

|                     | V5                            | Vsl, Vsr                                                             | -0.3 toV₀+0.3                 | V    | 1,2 |

| Input voltage       | Vı                            | D17-D16, XCK, LP, L/R, FR,<br>MD, S/C, EIO1, EIO2,<br>DISPOFF, TEST1 | -0.3 to V <sub>DD</sub> + 0.3 | ٧    |     |

| Storage temperature | Тѕтс                          |                                                                      | -45 to +125                   | °C   |     |

#### NOTES:

#### 4.2 Electrical-Optical Characteristics

| No | Item         |           | Symbol           | Condition                           | Min. | Тур. | Max. | Unit |

|----|--------------|-----------|------------------|-------------------------------------|------|------|------|------|

| 1  | Current (all | SEG on)   | 1                | Ta=25°C                             | -    | 15.0 | 30.0 | • A  |

| 2  | Contrast Ra  | atio      | Cr               | Ta=25°C<br>V <sub>LCD</sub> = 19.5V | 4.5  | 5.0  | -    | -    |

| 3  | Threshold    | voltage   | Vth              | Ta=25°C                             | 1.85 | 1.90 | -    | V    |

| 4  | Saturation   | voltage   | Vsat             | Ta=25°C                             | -    | 2.05 | 2.10 | V    |

|    |              | Rise time | Tr               | Ta=25°C                             | -    | 250  | 350  | ms   |

| 5  | 1            |           | Tf               | Ta=25°C                             | -    | 200  | 300  | ms   |

|    | time         | On time   | T <sub>ON</sub>  | Ta=25°C                             | -    | 300  | 450  | ms   |

| 6  |              | Off time  | T <sub>OFF</sub> | Ta=25°C                             | -    | 250  | 350  | ms   |

| 7  |              | 6H        | • 4              |                                     | 45   | -    | -    | Deg. |

| 8  | Viewing      | 12H       | • 2              | Cr = 2<br>Ta=25°C                   | 25   | -    | -    | Deg. |

| 9  | Angle        | 3Н        | • 8              |                                     | 45   | -    | -    | Deg. |

| 10 | ]            | 9H        | • 4              |                                     | 45   | -    | -    | Deg. |

| 11 | Frame freq   | uency     | fм               | Ta=25°C                             | 32   | 64   | 128  | Hz   |

#### 4.3 Electrical Characteristics

| No | Item                          | Symbol                                                 | Condition                         | Min. | Тур. | Max. | Unit |

|----|-------------------------------|--------------------------------------------------------|-----------------------------------|------|------|------|------|

| 1  | Supply Voltage for Logic      | V <sub>DD</sub> -V <sub>SS</sub>                       | -                                 | 2.5  | ı    | 5.5  | V    |

| 2  | Supply Voltage for LCD Driver | V <sub>DD</sub> -V <sub>O</sub><br>(V <sub>LCD</sub> ) | Ta=25 °C                          | 19.3 | 19.5 | 19.7 | V    |

| 3  | Supply Current for Logic      | I <sub>DD</sub>                                        | Ta=25 °C<br>V <sub>DD</sub> =5.0V | -    | 23   | 26   | mA   |

| 4  | Frame Frequency               | f <sub>M</sub>                                         | Ta=25°C                           | -    | 80   | -    | Hz   |

<sup>1.</sup> TA = +25 °C

<sup>2.</sup> The maximum applicable voltage on any pin with respect to Vss (0 V).

| 5 | Input High Voltage  | V <sub>IH</sub> | - | $0.8XV_{DD}$ | - | $V_{DD}$     | V |

|---|---------------------|-----------------|---|--------------|---|--------------|---|

| 6 | Input Low Voltage   | V <sub>IL</sub> | - | GND          | - | $0.2XV_{DD}$ | V |

| 7 | Output High Voltage | V <sub>OH</sub> | - | VDD-0.4      | - | -            | V |

| 8 | Output Low Voltage  | V <sub>OL</sub> | - | -            | - | +0.4         | V |

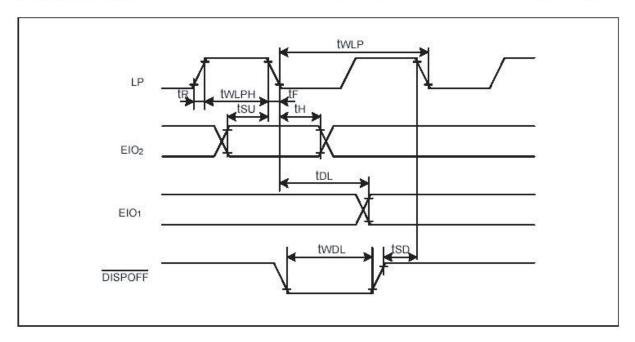

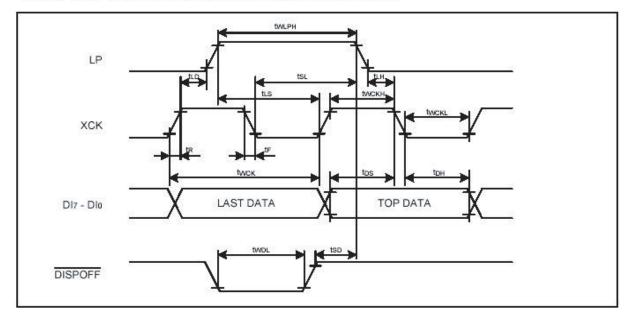

#### 4.3 Timming Characteristics

#### Segment

(Segment Mode 1) (Vss =  $V_5 = 0 \text{ V}, V_{DD} = +5.0\pm0.5 \text{ V}, V_0 = +15.0 \text{ to } +42.0 \text{ V}, T_{OPR} = -25 \text{ to } +85 ^{\circ}\text{C}$ )

| PARAMETER                                 | SYMBOL     | CONDITIONS   | MIN | TYP. | MAX. | UNIT | NOTE |

|-------------------------------------------|------------|--------------|-----|------|------|------|------|

| Shift clock period                        | twck       | tr,tr ≤ 10ns | 50  |      |      | ns   | 1    |

| Shift clock "H" pulse width               | twcкн      |              | 15  |      |      | ns   | 2    |

| Shift clock "L" pulse width               | twckL      |              | 15  |      |      | ns   |      |

| Data setup time                           | tos        |              | 10  |      |      | ns   |      |

| Data hold time                            | tон        |              | 12  |      |      | ns   |      |

| Latch pulse "H" pulse width               | twlph      | n n          | 15  |      |      | ns   |      |

| Shift clock rise to latch pulse rise time | tuo        |              | 0   |      |      | ns   |      |

| Shift clock fall to latch pulse fall time | tsı        |              | 30  |      |      | ns   |      |

| Latch pulse rise to shift clock rise time | tus        |              | 25  |      |      | ns   |      |

| Latch pulse fall to shift clock fall time | tьн        |              | 25  |      |      | ns   | 1    |

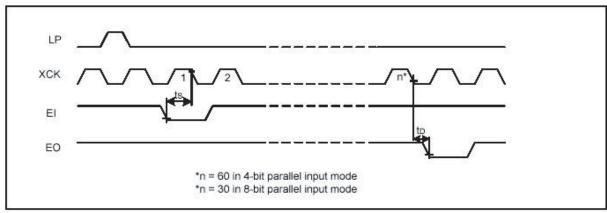

| Enable setup time                         | ts         |              | 10  |      |      | ns   |      |

| Input signal rise time                    | tr         |              |     |      | 50   | ns   | 2    |

| Input signal fall time                    | tr         |              |     |      | 50   | ns   | 2    |

| DISPOFF removal time                      | tsp        | i i          | 100 |      |      | ns   |      |

| DISPOFF "L" pulse width                   | twoL       |              | 1.2 |      |      | μs   |      |

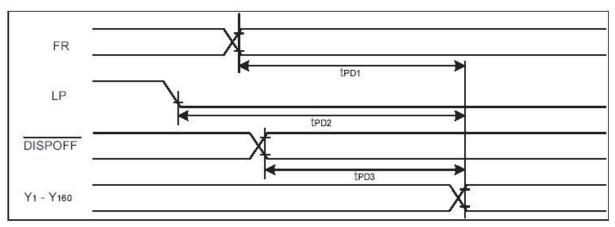

| Output delay time (1)                     | to         | CL = 15 pF   |     |      | 30   | ns   |      |

| Output delay time (2)                     | tedi, teda | CL = 15 pF   |     |      | 1.2  | μs   |      |

| Output delay time (3)                     | tроз       | CL = 15 pF   |     |      | 1.2  | μs   |      |

#### NOTES:

- 1. Takes the cascade connection into consideration.

- 2. (twcк twcкн twcкL)/2 is maximum in the case of high speed operation.

(Segment Mode 2) (Vss = Vs = 0 V, VDD = +3.0 to +4.5 V, V0 = +15.0 to +42.0 V, TopR = -25 10+85 °C)

| PARAMETER                                 | SYMBOL     | CONDITIONS | MIN. | TYP.     | MAX. | UNIT | NOTE |

|-------------------------------------------|------------|------------|------|----------|------|------|------|

| Shift clock period                        | twck       | tr,tr≤10ns | 66   | 9        |      | ns   | 1    |

| Shift clock "H" pulse width               | twckh      |            | 23   |          |      | ns   |      |

| Shift clock "L" pulse width               | twckL      |            | 23   |          |      | ns   |      |

| Data setup time                           | tos        |            | 15   | 31       |      | ns   |      |

| Data hold time                            | tон        |            | 23   | g.       |      | ns   |      |

| Latch pulse "H" pulse width               | twlph      |            | 30   |          |      | ns   |      |

| Shift clock rise to latch pulse rise time | tuo        |            | 0    |          |      | ns   |      |

| Shift clock fall to latch pulse fall time | tsL        |            | 50   | 31       |      | ns   |      |

| Latch pulse rise to shift clock rise time | tus        |            | 30   | g.       |      | ns   |      |

| Latch pulse fall to shift clock fall time | tьн        |            | 30   |          |      | ns   |      |

| Enable setup time                         | ts         |            | 15   |          |      | ns   | 100  |

| Input signal rise time                    | tr         |            |      | 31<br>31 | 50   | ns   | 2    |

| Input signal fall time                    | tr         |            |      | g.       | 50   | ns   | 2    |

| DISPOFF removal time                      | tsp        |            | 100  |          |      | ns   |      |

| DISPOFF "L" pulse width                   | twoL       | 1          | 1.2  |          |      | μs   |      |

| Output delay time (1)                     | to         | CL = 15 pF | 8    | 3        | 41   | ns   |      |

| Output delay time (2)                     | teds, teds | CL = 15 pF | 4    | g.       | 1.2  | μs   |      |

| Output delay time (3)                     | tррз       | CL = 15 pF |      |          | 1.2  | μs   |      |

#### NOTES:

- 1. Takes the cascade connection into consideration.

- 2. (twcк twcкн twcкL)/2 is maximum in the case of high speed operation.

#### AGM2412B

| 5 | Input High Voltage  | V <sub>IH</sub> | _ | $0.8XV_{DD}$ | - | $V_{DD}$     | V |

|---|---------------------|-----------------|---|--------------|---|--------------|---|

| 6 | Input Low Voltage   | V <sub>IL</sub> | - | GND          | - | $0.2XV_{DD}$ | V |

| 7 | Output High Voltage | V <sub>OH</sub> | - | VDD-0.4      | - | -            | V |

| 8 | Output Low Voltage  | V <sub>OL</sub> | - | -            | - | +0.4         | V |

#### 4.3 Timming Characteristics

#### Segment

(Segment Mode 1) (Vss =  $V_5 = 0 \text{ V}, V_{DD} = +5.0\pm0.5 \text{ V}, V_0 = +15.0 \text{ to } +42.0 \text{ V}, T_{OPR} = -25 \text{ to } +85 ^{\circ}\text{C}$ )

| PARAMETER                                 | SYMBOL     | CONDITIONS   | MIN | TYP. | MAX. | UNIT | NOTE |

|-------------------------------------------|------------|--------------|-----|------|------|------|------|

| Shift clock period                        | twck       | tr,tr ≤ 10ns | 50  |      |      | ns   | 1    |

| Shift clock "H" pulse width               | twcкн      |              | 15  |      |      | ns   | 2    |

| Shift clock "L" pulse width               | twckL      |              | 15  |      |      | ns   |      |

| Data setup time                           | tos        |              | 10  |      |      | ns   |      |

| Data hold time                            | tон        |              | 12  |      |      | ns   |      |

| Latch pulse "H" pulse width               | twlph      | n n          | 15  |      |      | ns   |      |

| Shift clock rise to latch pulse rise time | tuo        |              | 0   |      |      | ns   |      |

| Shift clock fall to latch pulse fall time | tsı        |              | 30  |      |      | ns   |      |

| Latch pulse rise to shift clock rise time | tus        |              | 25  |      |      | ns   |      |

| Latch pulse fall to shift clock fall time | tьн        |              | 25  |      |      | ns   | 1    |

| Enable setup time                         | ts         |              | 10  |      |      | ns   |      |

| Input signal rise time                    | tr         |              |     |      | 50   | ns   | 2    |

| Input signal fall time                    | tr         |              |     |      | 50   | ns   | 2    |

| DISPOFF removal time                      | tsp        | i i          | 100 |      |      | ns   |      |

| DISPOFF "L" pulse width                   | twoL       |              | 1.2 |      |      | μs   |      |

| Output delay time (1)                     | to         | CL = 15 pF   |     |      | 30   | ns   |      |

| Output delay time (2)                     | tedi, teda | CL = 15 pF   |     |      | 1.2  | μs   |      |

| Output delay time (3)                     | tроз       | CL = 15 pF   |     |      | 1.2  | μs   |      |

#### NOTES:

- 1. Takes the cascade connection into consideration.

- 2. (twcк twcкн twcкL)/2 is maximum in the case of high speed operation.

(Segment Mode 2) (Vss = Vs = 0 V, VDD = +3.0 to +4.5 V, V0 = +15.0 to +42.0 V, TopR = -25 10+85 °C)

| PARAMETER                                 | SYMBOL           | CONDITIONS | MIN. | TYP.     | MAX. | UNIT | NOTE |

|-------------------------------------------|------------------|------------|------|----------|------|------|------|

| Shift clock period                        | twck             | tr,tr≤10ns | 66   | 9        |      | ns   | 1    |

| Shift clock "H" pulse width               | twckh            |            | 23   |          |      | ns   |      |

| Shift clock "L" pulse width               | twckL            |            | 23   |          |      | ns   |      |

| Data setup time                           | tos              |            | 15   | 31       |      | ns   |      |

| Data hold time                            | tон              |            | 23   | g.       |      | ns   |      |

| Latch pulse "H" pulse width               | twlph            |            | 30   |          |      | ns   |      |

| Shift clock rise to latch pulse rise time | tuo              |            | 0    |          |      | ns   |      |

| Shift clock fall to latch pulse fall time | tsL              |            | 50   | 31       |      | ns   |      |

| Latch pulse rise to shift clock rise time | tus              |            | 30   | g.       |      | ns   |      |

| Latch pulse fall to shift clock fall time | tьн              |            | 30   |          |      | ns   |      |

| Enable setup time                         | ts               |            | 15   |          |      | ns   | 100  |

| Input signal rise time                    | tr               |            |      | 31<br>31 | 50   | ns   | 2    |

| Input signal fall time                    | tr               |            |      | g.       | 50   | ns   | 2    |

| DISPOFF removal time                      | tsp              |            | 100  |          |      | ns   |      |

| DISPOFF "L" pulse width                   | twoL             | 1          | 1.2  |          | i i  | μs   |      |

| Output delay time (1)                     | to               | CL = 15 pF | 8    | 3        | 41   | ns   |      |

| Output delay time (2)                     | teds, teds       | CL = 15 pF | 4    | g.       | 1.2  | μs   |      |

| Output delay time (3)                     | t <sub>PD3</sub> | CL = 15 pF |      |          | 1.2  | μs   |      |

#### NOTES:

- 1. Takes the cascade connection into consideration.

- 2. (twcк twcкн twcкL)/2 is maximum in the case of high speed operation.

| (Segment Mode 3) | $(V_{SS} = V_5 = 0 V,$ | $V_{DD} = +2.5 \text{ to } +3.0 \text{ V}, \text{ V}_0 =$ | + 15.0 to +42.0 V, Topr = -25 10+ | 85 °C) |

|------------------|------------------------|-----------------------------------------------------------|-----------------------------------|--------|

|------------------|------------------------|-----------------------------------------------------------|-----------------------------------|--------|

| PARAMETER                                 | SYMBOL     | CONDITIONS | MIN. | TYP. | MAX. | UNIT | NOTE |

|-------------------------------------------|------------|------------|------|------|------|------|------|

| Shift clock period                        | twck       | tr,tr≤10ns | 82   |      |      | ns   | 1    |

| Shift clock "H" pulse width               | twokh      |            | 28   |      |      | ns   |      |

| Shift clock "L" pulse width               | twckL      |            | 28   |      |      | ns   |      |

| Data setup time                           | tos        |            | 20   |      |      | ns   |      |

| Data hold time                            | tон        |            | 23   |      |      | ns   |      |

| Latch pulse "H" pulse width               | twlph      |            | 30   |      |      | ns   |      |

| Shift clock rise to latch pulse rise time | tLD        |            | 0    | ĺ    |      | ns   |      |

| Shift clock fall to latch pulse fall time | tsı        |            | 65   |      |      | ns   |      |

| Latch pulse rise to shift clock rise time | tus        |            | 30   |      |      | ns   |      |

| Latch pulse fall to shift clock fall time | tьн        |            | 30   |      |      | ns   |      |

| Enable setup time                         | ts         |            | 15   |      |      | ns   |      |

| Input signal rise time                    | tr         |            |      |      | 50   | ns   | 2    |

| Input signal fall time                    | tr         |            |      |      | 50   | ns   | 2    |

| DISPOFF removal time                      | tsp        |            | 100  |      |      | ns   |      |

| DISPOFF "L" pulse width                   | twoL       |            | 1.2  |      |      | μs   |      |

| Output delay time (1)                     | to         | CL = 15 pF |      |      | 57   | ns   |      |

| Output delay time (2)                     | tpd1, tpd2 | CL = 15 pF | 1-   |      | 1.2  | μs   |      |

| Output delay time (3)                     | tроз       | CL = 15 pF |      |      | 1.2  | μs   |      |

#### NOTES:

- 1. Takes the cascade connection into consideration.

- 2. (twck twckh twckl)/2 is maximum in the case of high speed operation.

Fig. 8 Timing Characteristics (3)

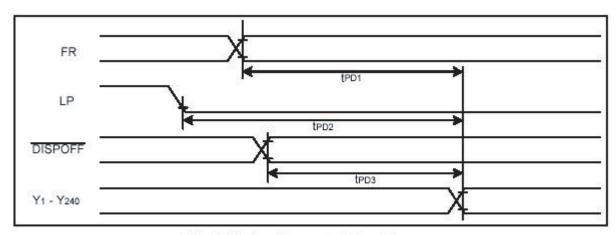

#### Common

(Common Mode) (Vss = 0 V,  $V_{DD}$  = +2.5 to +5.5 V,  $V_0$  = +15.0 to +30.0 V,  $T_{OPR}$  = -25 to +85° C)

| PARAMETER                   | SYMBOL      | CONDITIONS            | MIN. | TYP. | MAX. | UNIT |

|-----------------------------|-------------|-----------------------|------|------|------|------|

| Shift clock period          | twlp        | tr,tr ≤ 20ns          | 250  |      |      | ns   |

| Shift clock "H" pulse width | twlph       | $VDD = +5.0 \pm 0.5V$ | 15   |      |      | ns   |

|                             |             | VDD = +2.5 + 4.5V     | 30   |      |      | ns   |

| Data setup time             | tsu         |                       | 30   |      |      | ns   |

| Data hold time              | tн          |                       | 50   |      |      | ns   |

| Input signal rise time      | tr          |                       |      |      | 50   | ns   |

| Input signal fall time      | tr          |                       |      |      | 50   | ns   |

| DISPOFF removal time        | tso         |                       | 100  |      |      | ns   |

| DISPOFF "L" pulse width     | twoL        |                       | 1.2  |      |      | μs   |

| Output delay time (1)       | tou         | CL = 15 pF            |      |      | 200  | ns   |

| Output delay time (2)       | tpp1, t pp2 | CL = 15 pF            |      |      | 1.2  | μs   |

| Output delay time (3)       | t PD3       | CL = 15 pF            |      |      | 1.2  | μs   |