[AK2048]

# AKM

# AK2048D 2M CMI Transceiver

#### FEATURES

- 2.048Mbps CMI Interface

- CLOCK & DATA Recovery function

- Loss of Lock Detection

- Loss of Signal Detection

- Transmitter Pulse Shape

- Single 5.0V $\pm$ 5% Operation

- Low Power Consumption: 400mW (TYP)

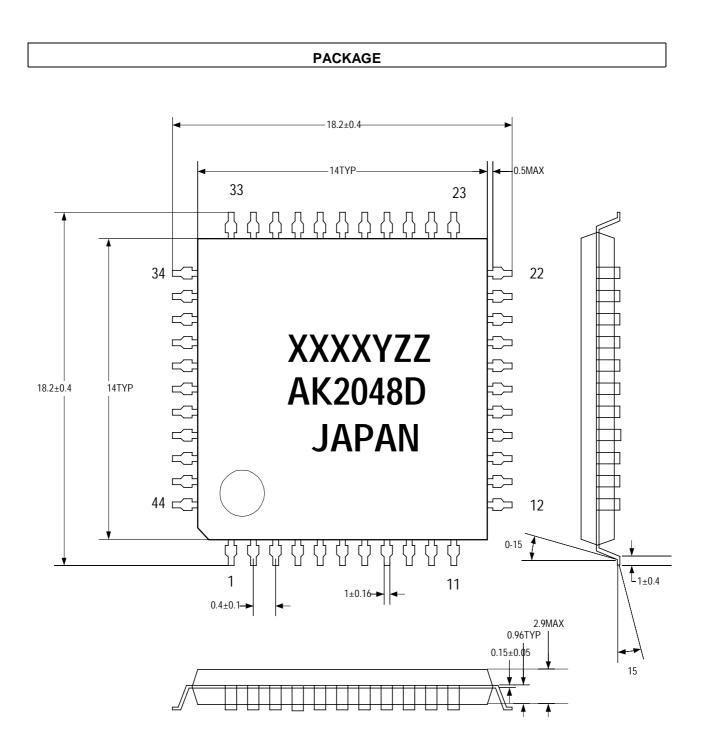

- Package: 44pin QFP

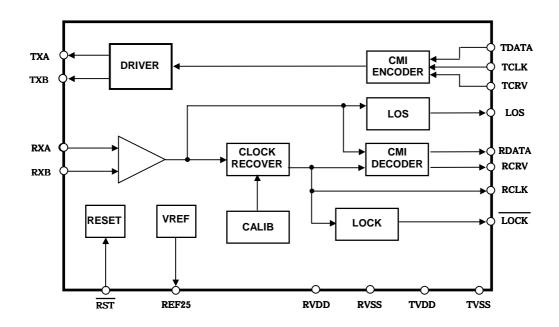

#### **BLOCK DIAGRAM**

2M CMI Transceiver Block Diagram

#### **GENERAL DESCRIPTIONS**

AK2048D is the 2.048Mbps CMI interface CMOS LSI for CMI interface card. It includes Clock and Data Recovery, Line Driver, LOS Detector, etc.

Build in PLL clock recovery circuit eliminates the correlation of the frequency deviation due to the uneven quality of the devices and a secular change.

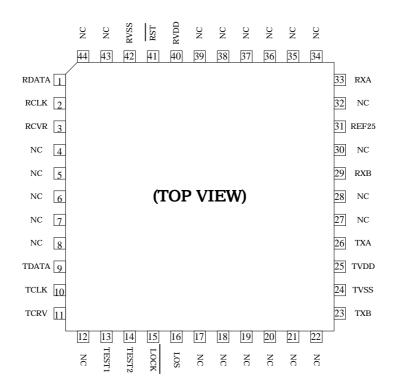

# **PIN ASSIGNMENTS**

44pin QFP

#### PIN ASSIGNMENTS

| Pin No. | Pin Name | I/O | Туре   | AC Load<br>(MAX) | DC Load<br>(MIN) | Comment                                                   |

|---------|----------|-----|--------|------------------|------------------|-----------------------------------------------------------|

| 1       | RDATA    | 0   | TTL    | ≤15pF            | ≥4kΩ             |                                                           |

| 2       | RCLK     | 0   | TTL    | ≤15pF            | ≥4kΩ             |                                                           |

| 3       | RCRV     | 0   | TTL    | ≤15pF            | ≥4kΩ             |                                                           |

| 9       | TDATA    | I   | TTL    |                  |                  |                                                           |

| 10      | TCLK     | I   | TTL    |                  |                  |                                                           |

| 11      | TCRV     | I   | TTL    |                  |                  |                                                           |

| 13      | TEST1    | -   |        |                  |                  | *2)                                                       |

| 14      | TEST2    | -   |        |                  |                  | *2)                                                       |

| 15      | LOCK     | 0   | TTL    | ≤15pF            | ≥4kΩ             |                                                           |

| 16      | LOS      | 0   | TTL    | ≤15pF            | ≥4kΩ             |                                                           |

| 23      | ТХВ      | 0   | Analog | ≤15pF            |                  | *1)                                                       |

| 24      | TVSS     | -   |        |                  |                  |                                                           |

| 25      | TVDD     | -   |        |                  |                  |                                                           |

| 26      | TXA      | 0   | Analog | ≤15pF            |                  | *1)                                                       |

| 29      | RXB      | I   | Analog |                  |                  |                                                           |

| 31      | REF25    | 0   | Analog | 1μF(typ)         |                  |                                                           |

| 33      | RXA      | I   | Analog |                  |                  |                                                           |

| 40      | RVDD     | -   |        |                  |                  |                                                           |

| 41      | RST      | I   | TTL    |                  |                  | Pulled up to VDD<br>by the internal<br>register (50KΩmin) |

| 42      | RVSS     | -   |        |                  |                  |                                                           |

The other pins (4-8,12,17-22,27,28,30,32,34-39,43,44) are NC pins.

NC pins are recommended to connect to VSS to avoid noise problem.

\*1) TXA, TXB can drive  $110\Omega$  connected between these pins.

\*2) Must be open.

#### PIN DESCRIPTIONS

| Pin Name | I/O | Function                                                                                             |

|----------|-----|------------------------------------------------------------------------------------------------------|

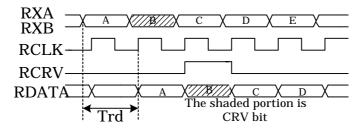

| RDATA    | 0   | Receive Data output recovered from the incoming data. Delay time from the incoming                   |

|          |     | data to the RDATA is about 1.25bit. Output on the rising edge of RCLK.                               |

| RCLK     | 0   | Receive Clock Output recovered from the incoming data.                                               |

| RCRV     | 0   | CRV (Code Rule Violation) output pin.                                                                |

|          |     | When AK2048D detects the CRV of CMI codes from in the coming data, RCRV goes                         |

|          |     | to "high" synchronized with the violation data. CRV is detected for both "0" data and                |

|          |     | "1" data. Refer to Fig.6, 11                                                                         |

| TDATA    | Ι   | Transmit Data Input pin.                                                                             |

|          |     | Input on the falling edge of TCLK.                                                                   |

| TCLK     | Ι   | Transmit Clock Input pin.                                                                            |

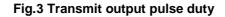

| TCRV     | Ι   | If this input is "high", AK2048D generates CRV in the transmit data.                                 |

|          |     | CRV is generated for both "0"data and "1"data. "High" input TCRV is accepted until 5                 |

|          |     | clocks duration. If the duration of "High" input is longer than 6 clocks, TCRV input                 |

|          |     | after 6th clock is ignored. Refer to Fig.4, 11                                                       |

| TEST1    | NC  | Test pin. Should be floated.                                                                         |

| TEST2    | NC  | Test pin. Should be floated.                                                                         |

| LOCK     | 0   | $\overline{\text{LOCK}}$ indicates the PLL status whether PLL is in the LOCK status or PLL is in the |

|          |     | UNLOCK status.                                                                                       |

|          |     | LOCK status                                                                                          |

|          |     | LOCK becomes "Low" when the sampled RCLK are all "Low" during the consecutive                        |

|          |     | 32 RXA-RXB sample clock duration.                                                                    |

|          |     | UN LOCK status                                                                                       |

|          |     | LOCK becomes "High" when the following both conditions are satisfied.                                |

|          |     | - The sampled RCLK are "High" more than 5 clocks in the frame of the consecutive                     |

|          |     | 256 RXA-RXB clock duration.                                                                          |

|          |     | - And the above happens in the 5 consecutive frames.                                                 |

|          |     | In another condition, LOCK keeps the current output status without change.                           |

|          |     | The output timing of this signal is asynchronous with RCLK.                                          |

|          |     | When RST is "Low", LOCK is fixed to "High".                                                          |

| Pin Name | I/O | Function                                                                                        |

|----------|-----|-------------------------------------------------------------------------------------------------|

| LOS      | 0   | LOS goes High within 12usec after AK2048D detects that the amplitude of the RXB                 |

|          |     | input signal is lower than 135mVpp(typ). Output on the rising edge of RCLK.                     |

| TXB      | 0   | Transmit CMI signal output. TXA is to CMI+, and TXB is corresponds to CMI                       |

|          |     | Delay time from TDATA to TXB is about 1bit.                                                     |

| TVSS     | -   | Negative power supply 0V                                                                        |

| TVDD     | -   | Positive power supply 5V                                                                        |

| TXA      | 0   | Transmit CMI signal output. TXA is to CMI+, and TXB is corresponds to CMI                       |

|          |     | Delay time from TDATA to TXA is about 1bit.                                                     |

| RXB      | Ι   | Receive CMI signal input. RXA is to CMI+, and RXB is corresponds to CMI                         |

| REF25    | 0   | Output reference voltage (about 2.5V) in order to decide middle point of input signal           |

|          |     | (RXA-RXB). Connected to middle point of the external equalizer.                                 |

| RXA      | Ι   | Receive CMI signal input. RXA is to CMI+, and RXB is corresponds to CMI                         |

| RVDD     | -   | Positive power supply. 5V                                                                       |

| RST      | 0   | "Low" input reset the calibration circuit and forces $\overline{\text{LOCK}}$ output "High" and |

|          |     | TXA-TXB output "High-Z". When this input rise, PLL calibration restarts.                        |

|          |     | Please set open or connect to VDD when not using.                                               |

| RVSS     | -   | Negative power supply 0V                                                                        |

#### ABSOLUTE MAXIMUM RATINGS

| Parameter            | Symbol | Min      | Тур | Max      | Units | Conditions |

|----------------------|--------|----------|-----|----------|-------|------------|

| DC Supply            | DVDD   | -0.3     |     | 6.0      | V     |            |

|                      | TVDD   |          |     |          |       |            |

| Input Voltage        | VIN    | RVSS-0.3 |     | RVDD+0.3 | V     |            |

| Input Current 1      | I IN1  |          |     | 10       | mA    | *1)        |

| Input Current 2      | I in2  |          |     | 200      | mA    |            |

| (TXA, TXB, RXA, RXB) |        |          |     |          |       |            |

| Storage Temperature  | Tstg   | -65      |     | 150      | °C    |            |

\*1) Except for TXA, TXB, RXA, RXB

### **RECOMMENDED OPERATING CONDITIONS**

| Parameter         | Symbol    | min  | typ | max  | Unit | Conditions                           |

|-------------------|-----------|------|-----|------|------|--------------------------------------|

| DC Supply         | RVDD      | 4.75 | 5.0 | 5.25 | v    | TVDD <rvdd+0.3v< td=""></rvdd+0.3v<> |

|                   | TVDD      |      |     |      |      |                                      |

| Ambient Operating | Та        | 0    | 25  | +80  | °C   |                                      |

| Temperature       |           |      |     |      |      |                                      |

|                   | PD1(RVDD) |      | 150 | 300  | mW   |                                      |

| Power Consumption | PD2(TVDD) |      | 250 | 300  | mW   | 110Ω LOAD                            |

#### ELECTRICAL CHARACTERISTICS

# DC CHARACTERISTICS

| Parameter                         | Symbol | min | typ | max | Unit | Conditions         |

|-----------------------------------|--------|-----|-----|-----|------|--------------------|

| Digital High-level input voltage  | Vih    | 2.4 |     |     | V    |                    |

| Digital Low-level input voltage   | VIL    |     |     | 0.8 | V    |                    |

| Digital High-Level output voltage | Vон    | 2.4 |     |     | V    | Iout=-40µA *1)     |

| Digital Low-level output voltage  | Vol    |     |     | 0.5 | V    | Iout=1.6mA *1)     |

| Input leak current 1              |        |     |     | 10  | μA   | Without RST, TEST1 |

| Input leak current 2              |        |     |     | 100 | μA   | RST, TEST1         |

\*1) When CMOS load is connected, output CMOS logic level.

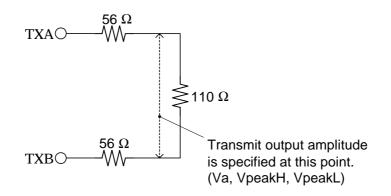

#### TRANSMITTER

| Parameter                         | Symbol | min  | typ | max  | Unit | Comments                   |

|-----------------------------------|--------|------|-----|------|------|----------------------------|

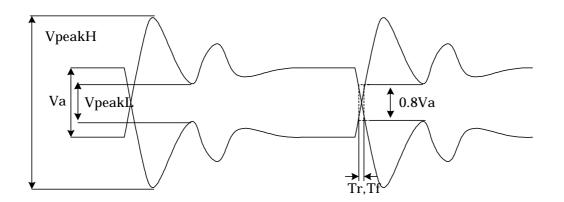

|                                   | Va     | 2.55 | 3.3 | 3.90 |      | Refer to Fig.1, 2          |

| Output signal level               | VpeakH |      |     | 4.05 | Vp-p |                            |

|                                   | VpeakL | 2.55 |     |      |      |                            |

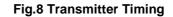

| Rise/Fall Time                    | Tr, Tf |      | 20  | 50   | ns   | Refer to Fig.1, 2          |

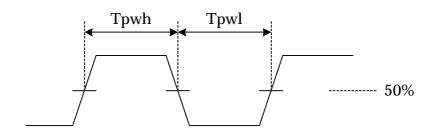

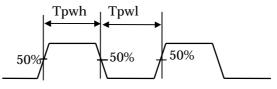

| Pulse duty of transmit output     |        | 43   | 50  | 57   | %    | *1), *2)<br>Refer to Fig.3 |

| Delay time from TDATA to TXA, TXB | Ttd    |      | 1   |      | Bit  | *3)Refer to Fig.4          |

\*1) The duty cycle of TCLK 50%±4%.

\*2) Duty cycle = Tpwh / (Tpwh + Tpwl)  $\times$  100%

\*3) Signal output delay = (1bit logical delay) + (internal propagation delay)

Fig.2 Rise and fall times

Fig.4 Data input to signal output delay time

#### RECEIVER

| Parameter                   | Symbol | min | typ  | max  | Unit  | Comments                       |

|-----------------------------|--------|-----|------|------|-------|--------------------------------|

| REF25 output                | VREF   | 2.0 | 2.5  | 3.0  | V     | Iout <iua *1)<="" td=""></iua> |

| Signal loss threshold level | Vth    | 85  | 135  | 185  | mVp-p | RXB terminal                   |

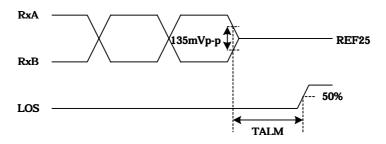

| Signal loss detection time  | TALM   |     | 10   | 12   | usec  | Fig.5                          |

| Sensitivity                 |        | 0.2 |      | 4.0  | Vp-p  |                                |

| Input jitter tolerance      |        |     |      | 0.15 | UIp-p | Jitter frequency               |

|                             |        |     |      |      |       | 20KHz~100KHz                   |

| PSRR (Line Length 400m)     |        |     |      | 400  | mVp-p | *2)                            |

| S/X tolerance               |        |     |      |      |       | *2)                            |

| Line Length 400m            |        | 2   |      |      | dB    | frequency 1.9MHz               |

| 0m                          |        | 12  |      |      | dB    |                                |

| Signal input to Data output | Trd    |     | 1.25 |      | bit   | Fig.6                          |

| delay time                  |        |     |      |      |       | *3)                            |

| RCLK Output Jitter          |        |     | 3    |      | nsp-p | *4)                            |

\*1) Reference output of fixed equalizer.

\*2) The amplitude of input data is 3.0 $\pm$ 0.75Vp-p and the data pattern is 2<sup>15</sup>-1.

\*3) Data output delay = (1.25bit logical delay) + (internal propagation delay)

\*4) Data pattern is "all space" with CRV every 8kHz cycle.

Fig.5 LOS output signal

Fig.6 Delay time from RXA,RXB to RDATA

# AC CHARACTERISTICS

| Parameter                                         | Pin<br>Name           | Symbol | min | typ   | max | Unit | Conditions                                         |

|---------------------------------------------------|-----------------------|--------|-----|-------|-----|------|----------------------------------------------------|

| Input Clock<br>Frequency                          | TCLK                  | fin    |     | 2.048 |     | MHz  |                                                    |

| Duty Cycle                                        | TCLK                  |        | 46  | 50    | 54  | %    | *1) Refer to Fig.7                                 |

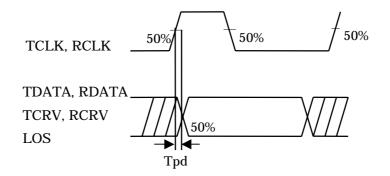

| Delay time from<br>TCLK rising to<br>TDATA, TCRV. | TDATA<br>TCRV         | Tpd    | -58 |       | 58  | ns   | Refer to Fig.8                                     |

| Output Clock<br>Frequency                         | RCLK                  | fout   |     | 2.048 |     | MHz  | The bit rate of<br>received signal is<br>2.048Mbps |

| Output Clock Duty                                 | RCLK                  |        | 43  | 50    | 57  | %    | *1) Refer to Fig.7                                 |

| Delay time from<br>RCLK rising to<br>RDATA, RCRV. | RDATA<br>RCRV         | Tpd    | -48 |       | 48  | ns   | Refer to Fig.8                                     |

|                                                   | LOS<br>LOCK           |        |     | 15    | 30  | ns   |                                                    |

| Rise/Fall Time                                    | RDATA<br>RCLK<br>RCRV | Tr, Tf |     |       | 15  | ns   | Refer to Fig.9                                     |

| Delay time from<br>RCLK rising to LOS             | LOS                   | Tpd    | -48 |       | 48  | ns   | Refer to Fig.8                                     |

\*1) Duty: Tpwh/(Tpwh+Tpwl)  $\times$  100%

Fig.7 Clock timing

Fig.9 Rise and fall times and a condition of measurement.

# FUNCTIONAL DESCRIPTION

#### **PLL** calibration function

The calibration of PLL is caused in case of the following 3cases.

- (1) Power on

- (2)  $\overline{\text{RST}}$  rising

- (3)  $\overline{\text{LOCK}}$  rising

### (1) Power on

After the power is on, the calibration is complete and  $\overline{\text{LOCK}}$  goes to "Low" in less than 63ms from whichever the later happens, the input of signal (RXA-RXB) or the rising edge of  $\overline{\text{RST}}$ .

# (2) $\overline{\text{RST}}$ rising

The calibration is complete and  $\overline{LOCK}$  goes to "Low" in less than 38ms from whichever the later happens, the input of signal (RXA-RXB) or the rising edge of RST.

### (3) **LOCK** rising

When the device falls into unlock by some reasons and  $\overline{\text{LOCK}}$  goes to "high", calibration restarts. The calibration is complete and  $\overline{\text{LOCK}}$  goes to "Low" in less than 38ms from the rising edge of  $\overline{\text{LOCK}}$ .

### PLL pull in time after loss of signal

When LOS goes to "high" by loss of signal after the calibration, the pull in of the PLL restarts by signal input. If the device can pull in without calibration, pull-in completes less than 200us. In other case, LOCK goes to "high" and calibration restarts less than 2ms.

### LOS signal

LOS goes to "high", when the amplitude of RXB is less than 135mVpp(typ) during 16 bits (about 8us). LOS signal goes to "Low", when amplitude of RXB is more than 135mVpp(typ).

When the signal is lost during the calibration, LOS signal goes to "high" and the calibration circuit is reset. The calibration restarts after LOS signal goes to "Low".

#### **CRV (Code Rule Violation)**

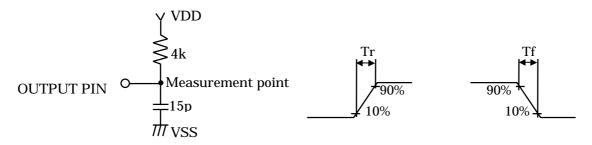

CMI code with violation is called as MD (Modified Dipulse) code. MD is refer to Fig.10. Generally speaking, CRV (Code Rule Violation) is generated at code "1". But AK2048D generates the violation for not only code "1", but also code "0". Violation of code "0" is refer to Fig.11.

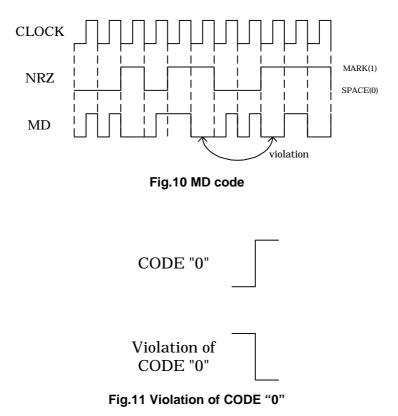

# **RECOMMENDED EXTERNAL CIRCUITS**

Fig.12 The example of the external circuits

It is recommended that Shott key diode in Fig 12 is connected for protection of latch-up.

#### **IMPORTANT NOTICE**

- These products and their specifications are subject to change without notice. Before considering any use or application, consult the Asahi Kasei Microsystems Co., Ltd. (AKM) sales office or authorized distributor concerning their current status.

- AKM assumes no liability for infringement of any patent, intellectual property, or other right in the application or use of any information contained herein.

- Any export of these products, or devices or systems containing them, may require an export license or other official approval under the law and regulations of the country of export pertaining to customs and tariffs, currency exchange, or strategic materials.

- AKM products are neither intended nor authorized for use as critical components in any safety, life support, or other hazard related device or system, and AKM assumes no responsibility relating to any such use, except with the express written consent of the Representative Director of AKM. As used here:

- (a) A hazard related device or system is one designed or intended for life support or maintenance of safety or for applications in medicine, aerospace, nuclear energy, or other fields, in which its failure to function or perform may reasonably be expected to result in loss of life or in significant injury or damage to person or property.

- (b) A critical component is one whose failure to function or perform may reasonably be expected to result, whether directly or indirectly, in the loss of the safety or effectiveness of the device or system containing it, and which must therefore meet very high standards of performance and reliability.

- It is the responsibility of the buyer or distributor of an AKM product who distributes, disposes of, or otherwise places the product with a third party to notify that party in advance of the above content and conditions, and the buyer or distributor agrees to assume any and all responsibility and liability for and hold AKM harmless from any and all claims arising from the use of said product in the absence of such notification.