# HI-8425, HI-8426

October 2013

8-Channel, Ground /Open, or Supply / Open Sensor 4-channel 200 mA Ground / Open Driver

### GENERAL DESCRIPTION

The HI-8425 is a combined 8-channel discrete-to-digital sensor and quad low side driver fabricated with Silicon-on-Insulator (SOI) technology for robust latch-up free operation. Sense detection can either be GND/Open or Supply/Open as configured by the SNSE\_SEL pin. Supply/Open sensing is also referred to as 28V/Open sensing. The sensing circuit window comparator thresholds can be fixed at the internal programmed values or can be set externally at the HI\_SET and LO\_SET pins, as selected by the THS\_SEL pin. The digital SENSE outputs can be tristated by taking the  $\overline{OE}$  pin high.

All sense inputs are internally lightning protected to DO160G, Section 22, Cat AZ, BZ and ZZ without external components.

The HI-8425 also offers four low side switches each capable of sinking 200 mA of current. Each switch transistor is controlled by its own digital input pin and is fully fault protected. Over-current conditions, such as a short circuit, are detected and inhibited while signaling the fault condition at the corresponding logic output. These four FAULT outputs are also available in a combined OR output. The outputs are fully protected from transients when driving relays.

The HI-8426 puts all of the features of the HI-8425 except the individual Fault Detection Outputs, Tri-state pin selection and fixed internal thresholds into a 32-pin Chip Scale Package (QFN) which measures only 5mm x 5mm.

Interface to the digital subsystem is simple CMOS logic inputs and outputs. The logic pins are compatible with 5V or 3.3V logic allowing direct connection to a wide range of microcontrollers or FPGAs.

## **FEATURES**

- Robust CMOS Silicon-on-Insulator (SOI) technology

- 8-channel Selectable Sense Operation, GND/Open or Supply/Open

- Selectable Thresholds and Hysteresis

- Sense Detection Range 3V to 22V

- Logic Operation from 3.0V to 5.5V

- Lightning Protected Sense Inputs

- Airbus ABD0100H compliant

- 4 Low-Side 200 mA drivers

- 4.5 Ohm On Resistance

- Over-Current Fault Detection Signaled by Logic Output

- Max Power Dissipation Automatically Limited by Fault Protection

- Diode Clamps for Discharging Inductive Loads

## APPLICATIONS

- Avionics Discrete to Digital Sensing

- Relay Driver

- · Lamp driver

- Discrete Signaling

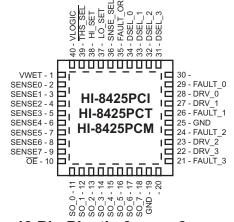

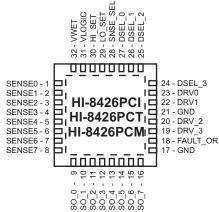

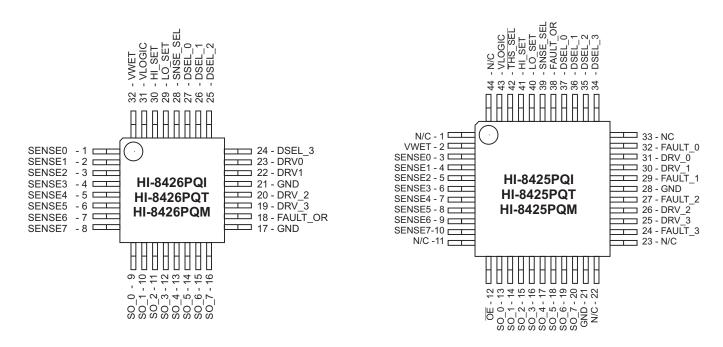

## PIN CONFIGURATIONS

## 40 Pin Plastic 6mm x 6mm Chip-scale package (QFN)

## 32 Pin Plastic 5mm x 5mm Chip-scale package (QFN)

(See page 15 for leaded QFP package options)

HOLT INTEGRATED CIRCUITS www.holtic.com

# **BLOCK DIAGRAM**

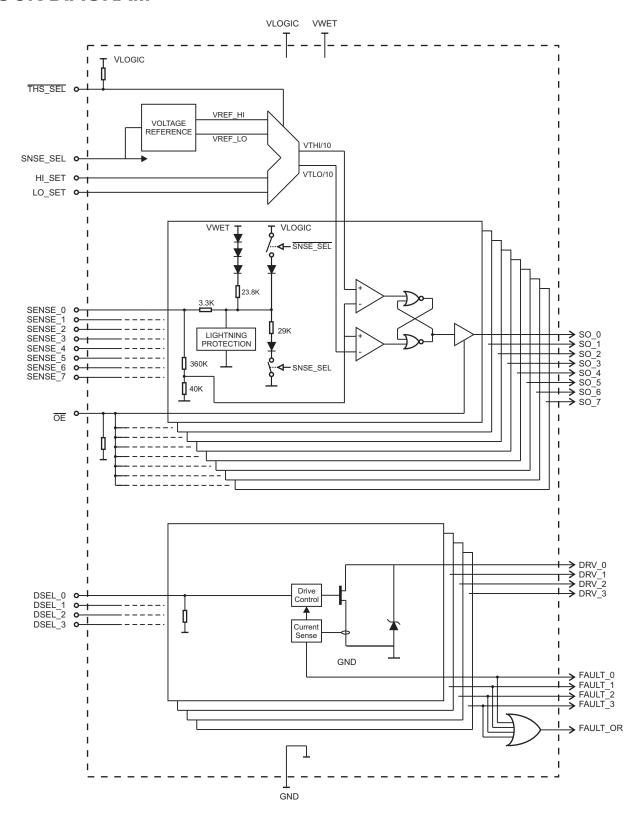

Figure 2

# **PIN DESCRIPTIONS**

| VWET     | Supply         | Optional input to supply relay wetting current to sense lines in GND/Open operation 50KΩ to GND                                                               |

|----------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SENSE0   | Discrete Input | Discrete input 0. If SNSE_SEL = 0 pin senses GND/Open. If SNSE_SEL = 1, senses SUPPLY/Open                                                                    |

| SENSE1   | Discrete Input | Discrete input 1. If SNSE_SEL = 0 pin senses GND/Open. If SNSE_SEL = 1, senses SUPPLY/Open                                                                    |

| SENSE2   | Discrete Input | Discrete input 2. If SNSE_SEL = 0 pin senses GND/Open. If SNSE_SEL = 1, senses SUPPLY/Open                                                                    |

| SENSE3   | Discrete Input | Discrete input 3. If SNSE_SEL = 0 pin senses GND/Open. If SNSE_SEL = 1, senses SUPPLY/Open                                                                    |

| SENSE4   | Discrete Input | Discrete input 4. If SNSE_SEL = 0 pin senses GND/Open. If SNSE_SEL = 1, senses SUPPLY/Open                                                                    |

| SENSE5   | Discrete Input | Discrete input 5. If SNSE_SEL = 0 pin senses GND/Open. If SNSE_SEL = 1, senses SUPPLY/Open                                                                    |

| SENSE6   | Discrete Input | Discrete input 6. If SNSE_SEL = 0 pin senses GND/Open. If SNSE_SEL = 1, senses SUPPLY/Open                                                                    |

| SENSE7   | Discrete Input | Discrete input 7. If SNSE_SEL = 0 pin senses GND/Open. If SNSE_SEL = 1, senses SUPPLY/Open                                                                    |

| ŌĒ       | Digital Input  | If High, SO_n and fault outputs are high-impedance. $\overline{\text{OE}}$ has internal 30K $\Omega$ pull-down resistor                                       |

| SO_0     | Digital output | High if SNSE_SEL=0 and SENSE0 < VLo, or Low if SNSE_SEL=1 and SENSE0 > Vні                                                                                    |

| SO_1     | Digital output | High if SNSE_SEL=0 and SENSE1 < VLo, or Low if SNSE_SEL=1 and SENSE1 > VHI                                                                                    |

| SO_2     | Digital output | High if SNSE_SEL=0 and SENSE2 < VLo, or Low if SNSE_SEL=1 and SENSE2 > VHI                                                                                    |

| SO_3     | Digital output | High if SNSE_SEL=0 and SENSE3 < VLo, or Low if SNSE_SEL=1 and SENSE3 > VHI                                                                                    |

| SO_4     | Digital output | High if SNSE_SEL=0 and SENSE4 < VLo, or Low if SNSE_SEL=1 and SENSE4 > VHI                                                                                    |

| SO_5     | Digital output | High if SNSE_SEL=0 and SENSE5 < VLo, or Low if SNSE_SEL=1 and SENSE5 > VHI                                                                                    |

| SO_6     | Digital output | High if SNSE_SEL=0 and SENSE6 < VLo, or Low if SNSE_SEL=1 and SENSE6 > VHI                                                                                    |

| SO_7     | Digital output | High if SNSE_SEL=0 and SENSE7 < VLo, or Low if SNSE_SEL=1 and SENSE7 > VHI                                                                                    |

| FAULT_3  | Digital output | High if Driver 3 is attempting to sink excess current                                                                                                         |

| DRV_3    | Switch Output  | Drain node of Ground switch driver 3                                                                                                                          |

| GND      | Supply         | Ground for logic and Analog Ground return for DRV0-3. GND pin and the isolated backside pad should be grounded for optimum performance and power dissipation. |

| DRV_2    | Switch Output  | Drain node of Ground switch driver 2                                                                                                                          |

| FAULT_2  | Digital output | High if Driver 2 is attempting to sink excess current                                                                                                         |

| FAULT_1  | Digital output | High if Driver 1 is attempting to sink excess current                                                                                                         |

| DRV_1    | Switch Output  | Drain node of Ground switch driver 1                                                                                                                          |

| DRV_0    | Switch Output  | Drain node of Ground switch driver 0                                                                                                                          |

| FAULT_0  | Digital output | High if Driver 0 is attempting to sink excess current                                                                                                         |

| DSEL 3   | Digital Input  | When high, turns on Driver 3. DSEL 3 has an internal 30KΩ pull-down resistor                                                                                  |

| DSEL_2   | Digital Input  | When high, turns on Driver 2. DSEL_2 has an internal 30KΩ pull-down resistor                                                                                  |

| DSEL_1   | Digital Input  | When high, turns on Driver 1. DSEL_1 has an internal 30KΩ pull-down resistor                                                                                  |

| DSEL_0   | Digital Input  | When high, turns on Driver 0. DSEL_0 has an internal 30KΩ pull-down resistor                                                                                  |

| FAULT_OR | Digital Output | High if any Driver is attempting to sink excess current                                                                                                       |

| SNSE_SEL | Digital Input  | If Low, SENSE pins are sensing Open/Gnd. If High, SENSE pins sense SUPPLY/Open                                                                                |

| LO_SET   | Analog input   | If THS_SEL is High, this pin sets the lower window comparator threshold                                                                                       |

| HI_SET   | Analog input   | If THS_SEL is High, this pin sets the upper window comparator threshold                                                                                       |

| THS_SEL  | Digital Input  | If THS_SEL is Low, comparator thresholds are set internally. THS_SEL has an internal 30KΩ pull-up                                                             |

| VLOGIC   | Supply         | Logic supply. (3.0V - 5.5V)                                                                                                                                   |

### **FUNCTIONAL DESCRIPTION**

#### **SENSING**

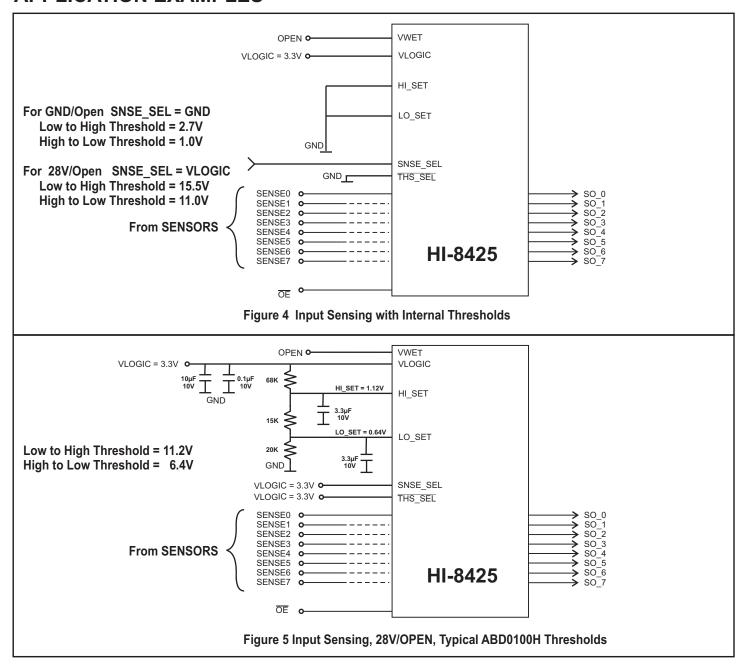

The 8 Sense Channels can be configured to meet the requirements of a variety of conditions and applications. Table 1 summarizes basic function selection and Table 2 gives more details on possible threshold values.

#### **GND/OPEN SENSING**

For GND/Open sensing, the SNS\_SEL pin is connected to GND. Referring to the Block Diagram, Figure 2, this selection will connect a  $3.3 \mathrm{K}\Omega$  pull-up resistor through a diode to VLOGIC and a  $23.8 \mathrm{K}\Omega$  resistor through 3 diodes to VWET. These resistors give extra noise immunity for detecting the open state while providing relay wetting current. Configuring THS\_SEL, HI\_SET/LO\_SEL and VWET as described below sets the window comparator thresholds, VTHI and VTLO, the open input voltage when open, and the input current.

#### HI-8425 (40 pin version) - THRESHOLD SELECT

The HI-8425 offers a choice between internally fixed thresholds or external thresholds provided by the user. With THS\_SEL set to GND, the window comparator thresholds are fixed based on an internal reference. The high threshold, VTHI, and the low threshold, VTHLO levels may be found in Table 2. When the internal references are used the HI\_SET and LO\_SET pins should be connected to GND. For applications with either large GND offsets or thresholds higher than VLOGIC - 0.75V, THS\_SEL is set high and the thresholds are set externally, for example by a simple resistor divider off the VLOGIC supply. In this case VTHI is equal to 10X the voltage on the HI\_SET pin. VTLO is equal to 10X the voltage on the LO\_SET pin. This mode allows the user complete flexibility to define the thresholds and hysteresis levels.

#### HI-8426 (32 pin version) THRESHOLD SELECT

For applications that can take advantage of the very small 32 pin chip scale package of the HI-8426, THS\_SEL is not available and an internal pull-up makes it mandatory to supply HI SET and LO SET externally.

#### **OPEN INPUT VOLTAGE**

For correct operation, the Vsense\_n when open, must be higher than VTHI so SO\_n will be low. This condition requires VWET to be set greater than (VTHI/0.9 + 2.25V). Various ARINC standards such as ARINC 763 define the standard "Open" signal as characterized by a resistance of  $100 \mathrm{K}\Omega$  or more with respect to signal common. The user should consider this  $100 \mathrm{K}\Omega$  to ground case when setting the thresholds.

#### WETTING CURRENT

For GND/Open applications with VWET open, the wetting current with the input voltage at GND is simply (VLOGIC - 0.75)/3.3K. When applying a higher voltage at the VWET pin the wetting current is (VLOGIC - 0.75)/3.3K + (VWET - 4.2)/127K. Additional wetting current can be achieved by placing an external resistor and a diode between VWET and the individual sense inputs.

#### SUPPLY/OPEN SENSING

The 8 Sense Channels can be configured to sense Supply/Open by connecting the SNSE\_SEL pin to VLOGIC. Refering to Figure 2, a  $32 \mathrm{K}\Omega$  resistor is switched in series to provide a pull down in addition to the  $400 \mathrm{K}\Omega$  of the comparator input divider to GND. Similar to the GND/Open case configuring THS\_SEL, HI\_SET/LO\_SEL and VWET as described below sets the window comparator thresholds, the open input voltage when open and the wetting current.

#### THRESHOLD SELECT

The threshold selections are handled in the same way as stated above for the GND/OPEN case.

For THS\_SEL set low, the internal reference nominally sets the window comparator. See table 2 for the VTHI and VTHLO threshold levels.

For THS\_SEL set high, the final thresholds are 10X the voltage set on the HI\_SET and LO\_SET pins. The VWET pin must be left open in the Supply/Open sensing case.

#### **WETTING CURRENT**

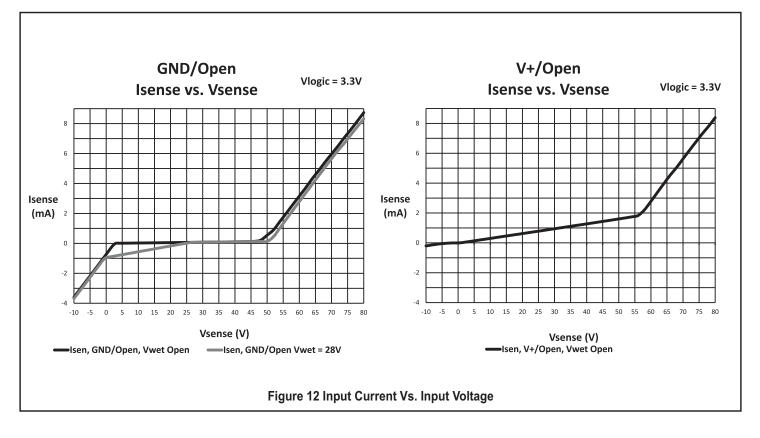

For the Supply/Open case the wetting current into the sense input is the current sunk by the effective  $28K\Omega$  to GND. For VSENSE n = 28V, IWET is 1ma. See Figure 12.

**Table 1. Function Table**

| SENSE_n        | SNSE_SEL     | ŌĒ | SO_n |

|----------------|--------------|----|------|

| Open or > VTHI | L (GND/OPEN) | L  | L    |

| < VTLO         | L (GND/OPEN) | L  | Н    |

| Х              | L (GND/OPEN) | Н  | Z    |

| Open or < VTLO | H (V+/OPEN)  | L  | Н    |

| > VTHI         | H (V+/OPEN)  | L  | L    |

| Х              | H (V+/OPEN)  | Н  | Z    |

H = VLOGIC, L = GND, Z = Hi-Z, X = Don't Care, V+ = Vsupply See Table 2 for values of VTHI/VTLO

### **FUNCTIONAL DESCRIPTION**

Table 2. Configuration options and allowed threshold values -55C to 125C.

| VLOGIC       | VWET<br>Pin | SNSE_<br>SEL | THS_<br>SEL | Operation | Threshold<br>Selected | Maximum HI_SET (VTHI = HI_SETx10) | Minimum<br>LO_SET<br>(VTLO =<br>LO_SETx10) | Guaranteed<br>High<br>Threshold | Guaranteed<br>Low<br>Threshold |

|--------------|-------------|--------------|-------------|-----------|-----------------------|-----------------------------------|--------------------------------------------|---------------------------------|--------------------------------|

| 3.0V         | OPEN        | L            | L           | GND/OPEN  | Internal              | -                                 | -                                          | 2.5V                            | 1.0V                           |

| 3.6V         | OPEN        | L            | L           | GND/OPEN  | Internal              | -                                 | -                                          | 2.7V                            | 1.0V                           |

| 3.3V         | 28V         | L            | L           | GND/OPEN  | Internal              | -                                 | -                                          | 2.55V                           | 1.0V                           |

| 3.0V         | 7V          | L            | Н           | GND/OPEN  | External              | 0.4V (4.0V)                       | 0.3V (3.0V)                                | VTHI + 0.5V                     | VTLO - 0.5V                    |

| 3.6V         | 7V          | L            | Н           | GND/OPEN  | External              | 0.4V (4.0V)                       | 0.3V (3.0V)                                | VTHI + 0.5V                     | VTLO - 0.5V                    |

| 3.0V to 3.6V | 28V         | L            | Н           | GND/OPEN  | External              | 2.2V (22V)                        | 0.3V (3.0V)                                | VTHI + 0.5V                     | VTLO - 0.5V                    |

| 3.0V to 3.6V | OPEN        | Н            | L           | V+/OPEN   | Internal              | -                                 | -                                          | 15.5V                           | 11.0V                          |

| 3.0V to 3.6V | OPEN        | Н            | Н           | V+/OPEN   | Exernal               | 2.2V (22V)                        | 0.3V (3.0V)                                | VTHI + 0.5V                     | VTLO - 0.5V                    |

| 4.5V         | OPEN        | L            | L           | GND/OPEN  | Internal              | -                                 | -                                          | 3.25V                           | 1.0V                           |

| 5.5V         | OPEN        | L            | L           | GND/OPEN  | Internal              | -                                 | -                                          | 3.75V                           | 1.0V                           |

| 5.0V         | 28V         | L            | L           | GND/OPEN  | Internal              | -                                 | -                                          | 3.5V                            | 1.0V                           |

| 4.5V         | 7V          | L            | Н           | GND/OPEN  | External              | 0.4V (4.0V)                       | 0.3V (3.0V)                                | VTHI + 0.5V                     | VTLO - 0.5V                    |

| 5.5V         | 7V          | L            | Н           | GND/OPEN  | External              | 0.4V (4.0V)                       | 0.3V (3.0V)                                | VTHI + 0.5V                     | VTLO - 0.5V                    |

| 4.5V to 5.5V | 28V         | L            | Н           | GND/OPEN  | External              | 2.2V (22V)                        | 0.3V (3.0V)                                | VTHI + 0.5V                     | VTLO - 0.5V                    |

| 4.5V to 5.5V | OPEN        | Н            | L           | V+/OPEN   | Internal              | -                                 | -                                          | 15.5V                           | 11.0V                          |

| 4.5V to 5.5V | OPEN        | Н            | Н           | V+/OPEN   | External              | 2.2V (22V)                        | 0.3V (3.0V)                                | VTHI + 0.5V                     | VTLO - 0.5V                    |

NOTE: VTHI = Sense pin high threshold (HI\_SET x 10), VTLO = Sense pin low threshold (LO\_SET x 10)

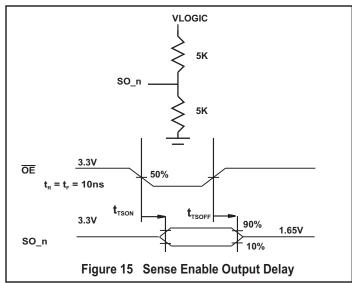

#### **OUTPUT ENABLE**

The output enable pin,  $\overline{\text{OE}}$ , available on the HI-8425, tristates all Sense Outputs and Low Side Driver Fault Outputs to allow connecting the tri-state outputs in parallel with other tri-stated chips. The  $\overline{\text{OE}}$  pin has a pull-down and when left open will cause these digital outputs to be driven to their logic levels. If the  $\overline{\text{OE}}$  pin is High, these digital outputs are high impedance.

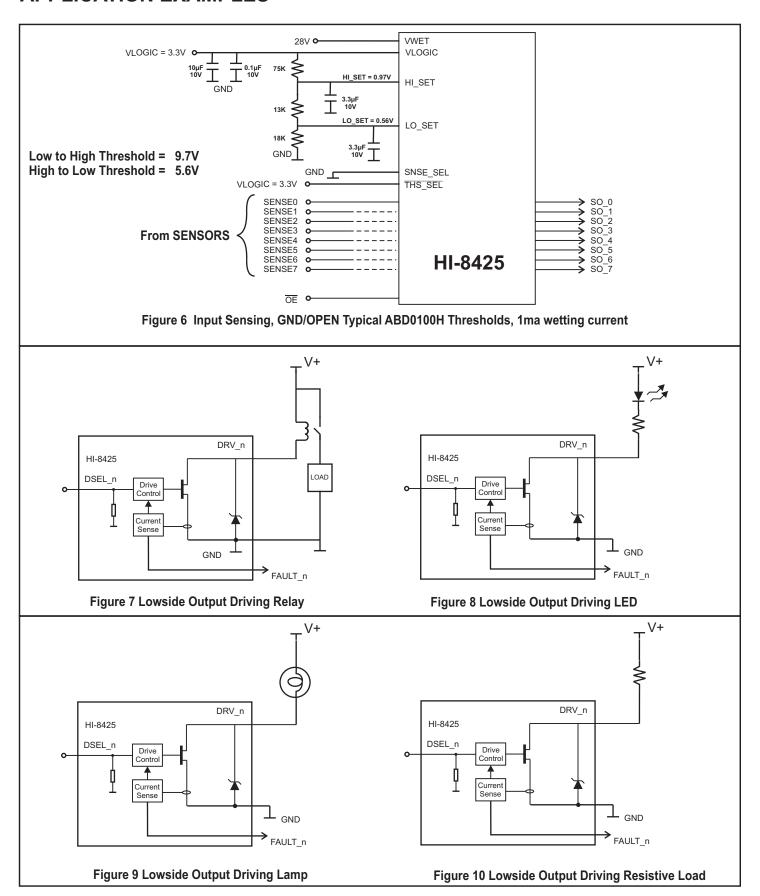

#### **OUTPUT DRIVERS**

#### **LOW SIDE DRIVERS**

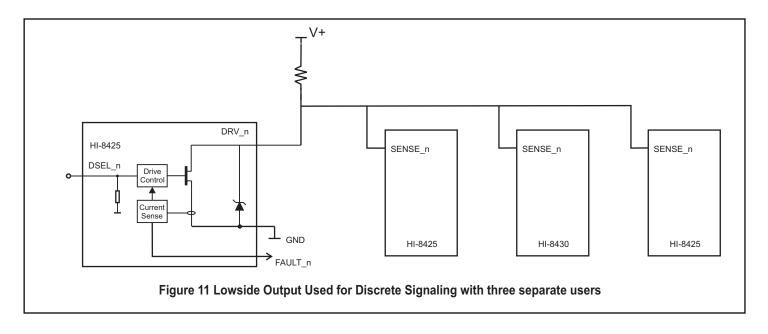

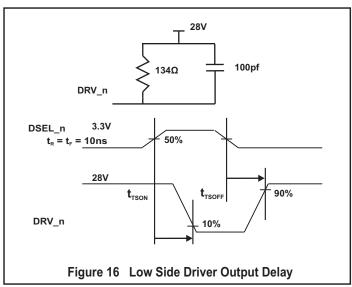

Both product versions offer four Low Side Drivers. Each driver (NMOS switch) is capable of sinking a minimum of 200mA while exhibiting a  $R_{\mbox{\tiny on}}$  of  $4.5\Omega$  typical. Each output has diode clamps for protection during inductive kick-back for relay applications. Off-state leakage is typically less than 10nA at room temperature. The inputs, DSEL0 through DSEL3, have internal pull-downs which hold off the drivers until logic highs are presented.

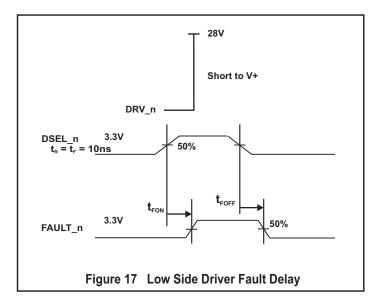

#### **OVER-CURRENT SHUTDOWN**

Maximum DC power dissipation per driver is approximately 0.5W at room temperature. Conditions that would cause the power to exceed this amount will result in a shut down of the driver. Over-current shutdown is initiated when the driver pin voltage is more than approximately 1.5V from GND. However there is a delay of approximately 11µsec before the shutdown actually occurs giving the driver an opportunity to charge capacitive loads and thereby avoid shutdown. Similarly, if the driver is on and a high load is suddenly switched on, the over-current shutdown will be delayed in activation. Note that even when the over-current fault condition is present, the driver pin is still sourcing a few milliamps. This low current condition continues until the input is taken low or the load is removed.

#### **FAULT CONDITIONS**

Each driver has a converter that translates an over-current detection into a logic high output at its FAULT output. The FAULT\_OR output goes high if one or more FAULT outputs are high. These outputs can be tri-stated by setting  $\overline{\text{OE}}$  high.

## **FUNCTIONAL DESCRIPTION**

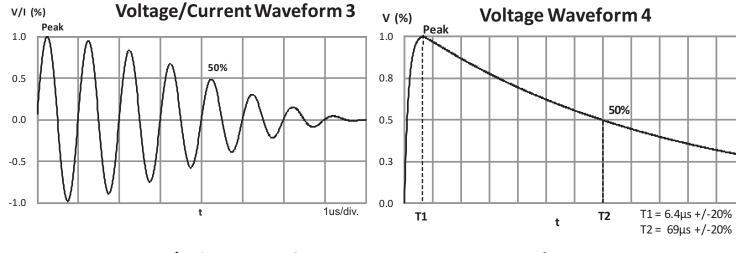

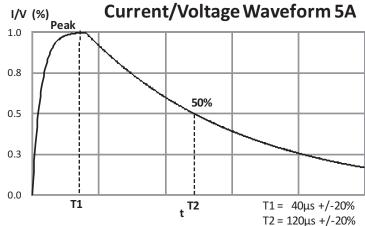

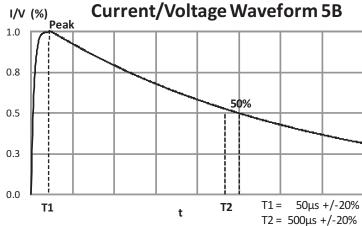

#### LIGHTNING PROTECTION

All SENSE\_n inputs are protected to RTCA/DO-160G, Section 22, Categories AZ and BZ, Waveforms 3, 4, 5A, with no external components. In addition, all inputs are also protected to ZZ, Waveforms 3 and 5B, to provide more robustness in composite airframe applications. Table 3 and Figure 3 give values and waveforms. See Application Note AN-305 for recommendations on lightning protection of Holt's family of Discrete-to-Digital devices.

|       | Waveforms         |                   |                   |                   |  |  |  |

|-------|-------------------|-------------------|-------------------|-------------------|--|--|--|

| Level | 3/3               | 4/1               | 5A/5A             | 5B/5B             |  |  |  |

|       | Voc (V) / Isc (A) |  |  |  |

| 2     | 250/10            | 125/25            | 125/125           | 125/125           |  |  |  |

| Z     | 500/20            | 300/60            | 300/300           | 300/300           |  |  |  |

| 3     | 600/24            | 300/60            | 300/300           | 300/300           |  |  |  |

Table 3. Waveform Peak Amplitudes

Figure 3. Lightning Waveforms

## **APPLICATION EXAMPLES**

## **APPLICATION EXAMPLES**

## **APPLICATION EXAMPLES**

## **ABSOLUTE MAXIMUM RATINGS**

| Voltages referenced to Ground                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------|

| Supply Voltage (VLOGIC) -0.3V to +7V                                                                                      |

| DRV_n55V                                                                                                                  |

| VWET -0.3V to +55V                                                                                                        |

| DC Driver Current per pin                                                                                                 |

| Logic Input Voltage Range0.3V to VLOGIC+0.3V                                                                              |

| Discrete Input Voltage Range80V to +80V                                                                                   |

| Continuous Power Dissipation (TA=+70°C)  QFN (derate 21.3mW/°C above +70°C) 1.7W  QFP (derate 10.0mW/°C above +70°C) 1.5W |

| Solder Temperature (reflow)                                                                                               |

| Junction Temperature175°C                                                                                                 |

| Storage Temperature65°C to -150°C                                                                                         |

# RECOMMENDED OPERATING CONDITIONS

| Supply Voltage |                                                               |

|----------------|---------------------------------------------------------------|

| VLOGIC         | 3.0V to 5.5V                                                  |

| VWET           | 7.0V to 36V                                                   |

|                | ature Range<br>creening40°C to +85°C<br>reening55°C to +125°C |

NOTE: Stresses above absolute maximum ratings or outside recommended operating conditions may cause permanent damage to the device. These are stress ratings only. Operation at the limits is not recommended.

## D.C. ELECTRICAL CHARACTERISTICS

VDD = 3.3V or 5V, GND = 0V, TA = Operating Temperature Range (unless otherwise specified).

| PARAMETER                        | SYMBOL | CONDITION                          | MIN       | TYP  | MAX       | UNITS |

|----------------------------------|--------|------------------------------------|-----------|------|-----------|-------|

| DISCRETE INPUTS                  |        |                                    |           |      |           |       |

| SENSE V+/OPEN                    |        | SEN_SEL = High, VWET floating      |           |      |           |       |

| Resistance to Ground             | Rin    |                                    |           | 30   |           | ΚΩ    |

| Case 1: THS_SEL = GND            |        | Internal Threshold Mode            |           |      |           |       |

| Open State Input Voltage         | Vos    | Input voltage to give High output  |           |      | 11.0      | V     |

| V+ State Input Voltage           | Vv+    | Input voltage to give Low output   | 15.5      |      |           | V     |

| Input Current at 28V             | lin28  | VIN = 28V                          |           | 0.95 |           | mA    |

| Hysteresis                       | VHY    |                                    | 1.5       |      |           | V     |

| Case 2: THS_SEL = Open or VLOGIC |        | HI_SET/LO_SET pin set Thresholds   |           |      |           |       |

| HI_SET Threshold Range           | VHR    | HI Threshold is set to HI_SET X 10 | 0.4       |      | 2.2       | V     |

| LO_SET Threshold Range           | Vlr    | LO Threshold is set to LO_SET X 10 | 0.3       |      | 2.1       | ٧     |

| Min Threshold Window             | VTHW   | HI_SET > LO_SET                    | 0.1       |      |           | V     |

| 10:1 Division Accuracy           |        | As measured by Sense Output Change | VLR - 0.5 |      | VHR + 0.5 | V     |

# D.C. ELECTRICAL CHARACTERISTICS (cont) VDD = 3.3V or 5V, GND = 0V, TA = Operating Temperature Range (unless otherwise specified).

| PARAMETER                                 | SYMBOL | CONDITION                                                            | MIN         | TYP            | MAX       | UNITS    |

|-------------------------------------------|--------|----------------------------------------------------------------------|-------------|----------------|-----------|----------|

| DISCRETE INPUTS                           |        |                                                                      |             |                |           |          |

| SENSE GND/OPEN                            |        |                                                                      |             |                |           |          |

| Resistance in series with diode to VLOGIC | Rin    |                                                                      |             | 3.3            |           | ΚΩ       |

| Resistance in series with diode to VWET   | Rw     |                                                                      |             | 23.8           |           | ΚΩ       |

| Case 1: THS_SEL = GND                     |        | Internal Threshold Mode                                              |             |                |           |          |

| Ground State Input Voltage                | Vgs    | Input voltage to give High output                                    |             |                | 1.0       | V        |

| Open State Input Voltage                  | Vos    | Input voltage to give Low output VDD = 5.5V VDD = 3.0V               | 3.75<br>2.5 |                |           | V        |

| Input Current at 0V                       | lin28  | V <sub>IN</sub> = 0V, VDD = 3.0V<br>V <sub>IN</sub> = 0V, VDD = 5.5V |             | -0.65<br>-1.65 |           | mA<br>mA |

| Hysteresis                                | VHY    |                                                                      | 0.15        |                |           | V        |

| Case 2: THS_SEL = Open or VLOGIC          |        | HI_SET/LO_SET pins set Thresholds                                    |             |                |           |          |

| HI_SET Threshold Range                    | VHR    | HI Threshold is set to HI_SET X 10                                   | 0.4         |                | 2.2       | V        |

| LO_SET Threshold Range                    | VLR    | LO Threshold is set to LO_SET X 10                                   | 0.3         |                | 2.1       | V        |

| Min Threshold Window                      | VTHW   | HI_SET > LO_SET                                                      | 0.1         |                |           | V        |

| 10:1 Division Accuracy                    |        | As measured by Sense Output Change                                   | VLR - 0.5   |                | VHR + 0.5 | V        |

| LOGIC INPUTS              |         |                              |     |     |     |        |

|---------------------------|---------|------------------------------|-----|-----|-----|--------|

| Input Voltage             | ViH     | Input Voltage HI             | 80% |     |     | VLOGIC |

|                           | VIL     | Input Votage LO              |     |     | 20% | VLOGIC |

| Input Current, OE, DSEL_n | Isink   | VIN = VLOGIC, 30KΩ pull down |     | 125 |     | μA     |

|                           | Isource | VIN = GND                    |     |     | 0.1 | μA     |

| Input Current, THS_SEL    | Isink   | VIN = VLOGIC                 | 0.1 |     |     | μA     |

|                           | Isource | Vin = GND , 30KΩ pull up     |     | 125 |     | μA     |

| Input Current, SNSE_SEL   | Isink   | VIN = VLOGIC                 | 0.1 |     |     | μA     |

|                           | Isource | VIN = GND,                   | 0.1 |     |     | μA     |

# **D.C. ELECTRICAL CHARACTERISTICS (cont)**

VDD = 3.3V, GND = 0V, TA = Operating Temperature Range (unless otherwise specified).

| LOGIC OUTPUTS             |      |                                 |      |    |      |        |

|---------------------------|------|---------------------------------|------|----|------|--------|

| Output Voltage            | Vон  | Іон = -100µА                    | 90%  |    |      | VLOGIC |

|                           | Vol  | IoL = 100μA                     |      |    | 10%  | VLOGIC |

| Output Current            | loL  | Vout= 0.4V                      | 1.6  |    |      | mA     |

|                           | Іон  | Vout = VLogic - 0.4V            |      |    | -1.0 | mA     |

| Tri-State Leakage Current | ITSL | VLOGIC > V <sub>out</sub> > GND | -1.0 |    | 1.0  | μΑ     |

| Output Capacitance        | Со   |                                 |      | 15 |      | pF     |

| PARAMETER                     | SYMBOL | CONDITION                                                         | MIN  | TYP | MAX | UNITS |

|-------------------------------|--------|-------------------------------------------------------------------|------|-----|-----|-------|

| ANALOG INPUTS                 |        |                                                                   |      |     |     |       |

| HI_SET/LO_SET Leakage Current | IL     | Max leakage for VLOGIC > V <sub>input</sub> > GND                 | -0.1 |     | 1.0 | μA    |

| LOW SIDE DRIVERS              |        |                                                                   |      |     |     |       |

| On Resistance                 | Ron    | I <sub>SOURCE</sub> = 200mA See Figure 16                         |      | 4.5 | 8   | Ω     |

| Over Current Threshold        | VDCMAX | Maximum V <sub>DS</sub> before current limiting.<br>See Figure 17 | 1.5  |     |     | ٧     |

| Over Current Delay            | Toc    | Period that Driver sinks max current.<br>See Figure 17            | 5    | 11  |     | μs    |

| SUPPLY                 |        |                                   |     |     |    |

|------------------------|--------|-----------------------------------|-----|-----|----|

| Operating VLOGIC range | VLOGIC |                                   | 3.0 | 5.5 | V  |

| Operation VWET range   | VWET   |                                   | 0   | 28  | V  |

| VLOGIC Current         | IDD1   | All Sense Pins Open               |     | 10  | mA |

| VWET Current           | IVWET  | All Sense Inputs = 0V, VWET = 28V |     | 20  | mA |

## **AC ELECTRICAL CHARACTERISTICS**

$\mbox{VDD} = 3.3 \mbox{V or 5V}, \ \mbox{GND} = \mbox{OV}, \ \mbox{TA} = \mbox{Operating Temperature Range} \ \ \mbox{(unless otherwise specified)}.$

| PARAMETER                | SYMBOL | CONDITION                          | MIN | TYP | MAX | UNITS |

|--------------------------|--------|------------------------------------|-----|-----|-----|-------|

| SENSE V+/OPEN            |        |                                    |     |     |     |       |

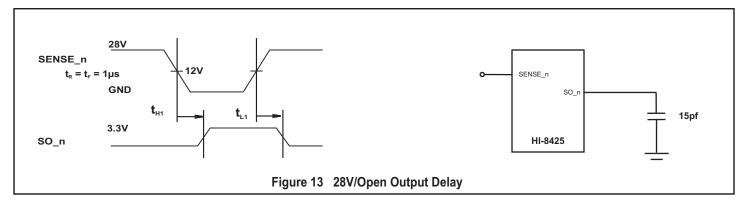

| Delay, Output going High | tH1    | See Figure 13, THS_SEL = GND, 25°C |     | 1.0 |     | μs    |

| Delay, Output going Low  | tL1    | See Figure 13, THS_SEL = GND, 25°C |     | 1.0 |     | μs    |

| SENSE GND/OPEN           |        |                                    |     |     |     |       |

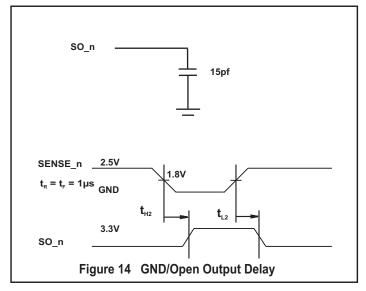

| Delay, Output going High | tH2    | See Figure 14, THS_SEL = GND, 25°C |     | 1.0 |     | μs    |

| Delay, Output going Low  | tL2    | See Figure 14, THS_SEL = GND, 25°C |     | 1.0 |     | μs    |

| TRI-STATE DELAY          |        |                                    |     |     |     |       |

| Tri-state Delay, On      | trson  | See Figure 15, THS_SEL = GND, 25°C |     |     | 40  | ns    |

| Tri-state Delay, Off     | trsoff | See Figure 15, THS_SEL = GND, 25°C |     |     | 40  | ns    |

| HIGH SIDE DRIVERS        |        |                                    |     |     |     |       |

| Turn On Delay, DSEL_N    | tson   | See Figure 16, VLOGIC = 3.3V, 25°C | 400 |     |     | ns    |

| Turn Off Delay, DSEL_N   | tsoff  | See Figure 16, VLOGIC = 3.3V, 25°C |     |     | 900 | ns    |

| Fault Output Delay, On   | tFON   | See Figure 17, VLOGIC = 3.3V, 25°C |     |     | 15  | μs    |

| Fault Output Delay, Off  | troff  | See Figure 17, VLOGIC = 3.3V, 25°C |     |     | 15  | μs    |

## **TEST CIRCUIT AND TIMING DIAGRAMS**

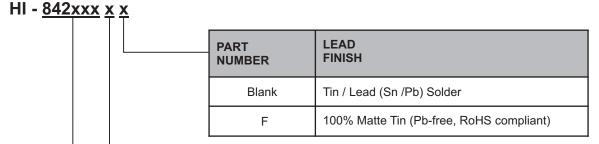

#### ORDERING INFORMATION

| PART<br>NUMBER |   | TEMPERATURE<br>RANGE | FLOW | BURN<br>IN |  |

|----------------|---|----------------------|------|------------|--|

|                | Ι | -40°C TO +85°C       | I    | NO         |  |

|                | Т | -55°C TO +125°C      | Т    | NO         |  |

|                | М | -55°C TO +125°C      | М    | YES        |  |

| PART<br>NUMBER | PACKAGE<br>DESCRIPTION                 |

|----------------|----------------------------------------|

| 8425PC         | 40 PIN PLASTIC CHIP SCALE (40PCS)      |

| 8425PQ         | 44 PIN PLASTIC QUAD FLAT PACK (44PMQS) |

| 8426PC         | 32 PIN PLASTIC CHIP SCALE (32PCS)      |

| 8426PQ         | 32 PIN PLASTIC QUAD FLAT PACK (32PQS)  |

32 - Pin Plastic Quad Flat Pack (PTQFP) 7mm x 7mm body

44 - Pin Plastic Quad Flat Pack (PQFP) 10mm x 10mm body

# **REVISION HISTORY**

| P/N    | Rev | Date     | Description of Change                                                                                |

|--------|-----|----------|------------------------------------------------------------------------------------------------------|

| DS8425 | NEW | 12/03/12 | Initial Release                                                                                      |

|        | Α   | 03/11/13 | Correct reference to pull-up resistor on inputs from 3.5K to 3.3K.                                   |

|        |     |          | Update VWET estimation formulas.                                                                     |

|        |     |          | Clarify VWET value for GND/Open and V+/Open sense options in DC Characteristics table.               |

|        |     |          | Update Figure 12 Input Current vs. Input Voltage charts.                                             |

|        |     |          | Delete Sensing Application Table. Add more detailed Table 2 instead.                                 |

|        |     |          | Updated Electrical Characteristics                                                                   |

|        | В   | 03/25/13 | Corrected typos in internal threshold limits for V+/Open with VWET open. Was 11.5V. Should be 11.0V. |

|        | С   | 08/20/13 | Updated Discrete Input Voltage Range from +/-60V to +/-80V.                                          |

|        | D   | 10/23/13 | Add "M-Grade" to PQFP and QFN package options. Reference AN-305 for lightning protection.            |

|        |     |          |                                                                                                      |

|        |     |          |                                                                                                      |

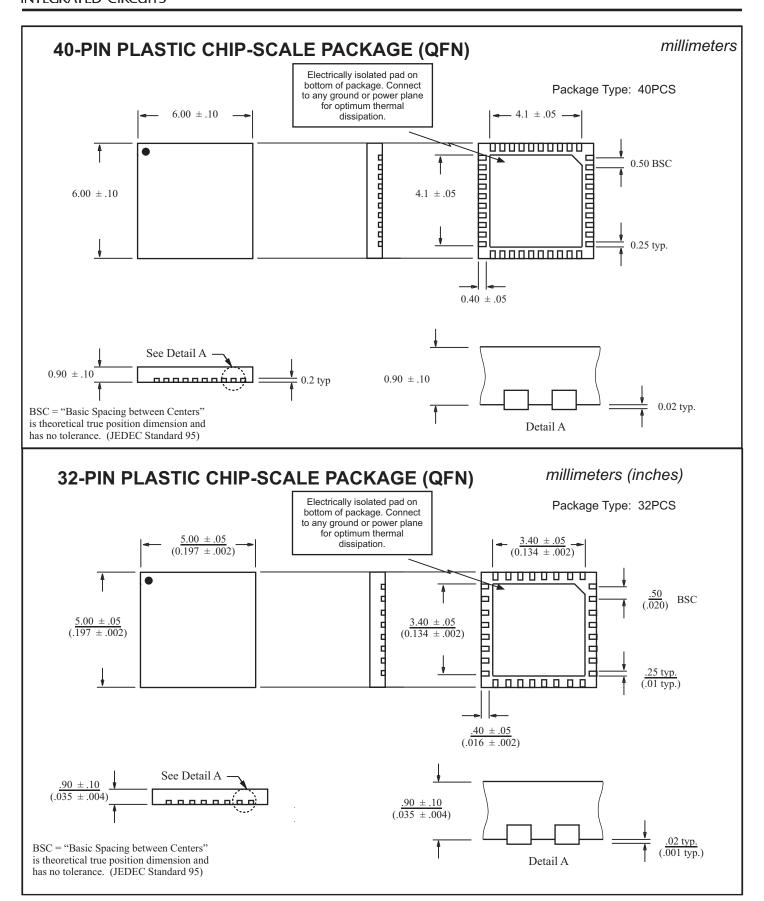

## **PACKAGE DIMENSIONS**

## **PACKAGE DIMENSIONS**

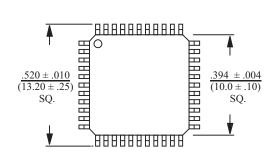

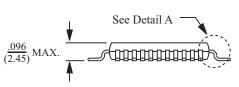

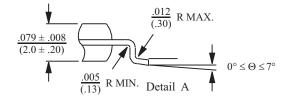

## 44-PIN PLASTIC QUAD FLAT PACK (PQFP)

## inches (millimeters)

Package Type: 44PMQS

BSC = "Basic Spacing between Centers" is theoretical true position dimension and has no tolerance. (JEDEC Standard 95)

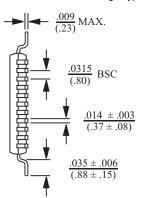

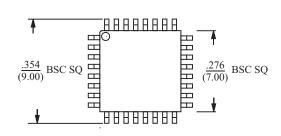

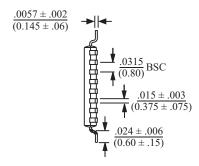

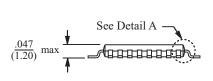

## 32 PIN PLASTIC QUAD FLAT PACK (PQFP)

## inches (millimeters)

Package Type: 32PQS

$\frac{.039 \pm .002}{(1.0 \pm .05)}$   $\frac{.006 \pm .002}{(0.14 \pm .06)} R$   $\frac{.004 \pm .002}{(0.10 \pm .05)}$   $\frac{.003}{(0.08)} R \min$   $0^{\circ} \le \Theta \le 7^{\circ}$ Detail A

BSC = "Basic Spacing between Centers" is theoretical true position dimension and has no tolerance. (JEDEC Standard 95)