#### **PRODUCTION DATASHEET**

### **DESCRIPTION**

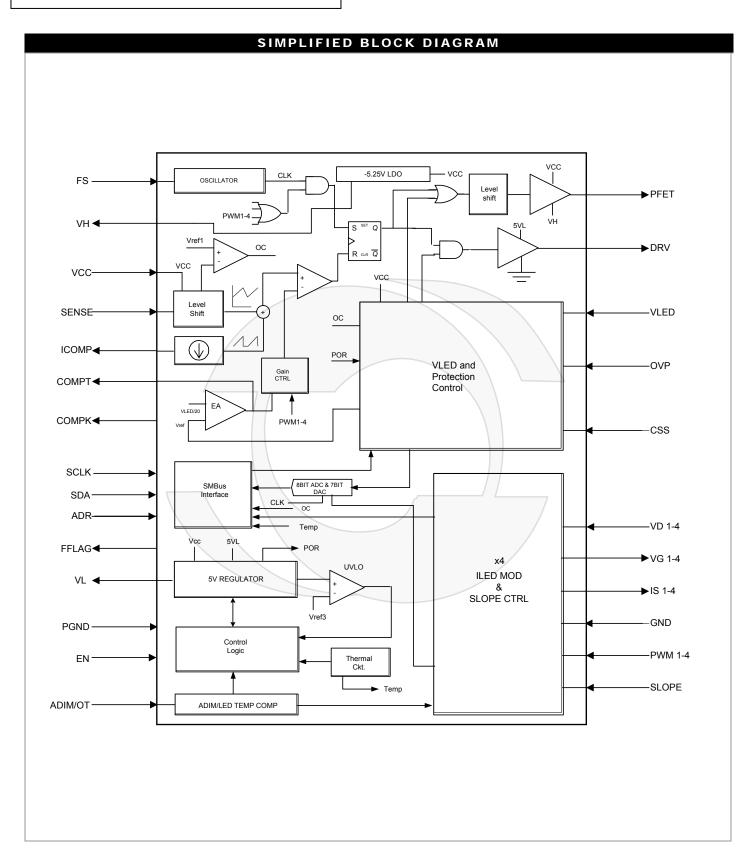

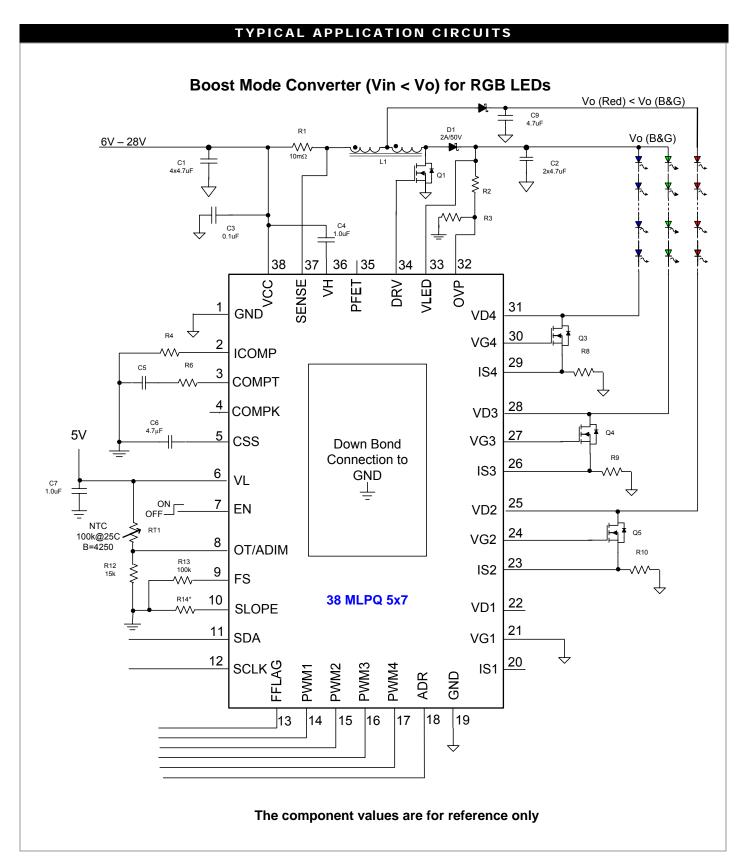

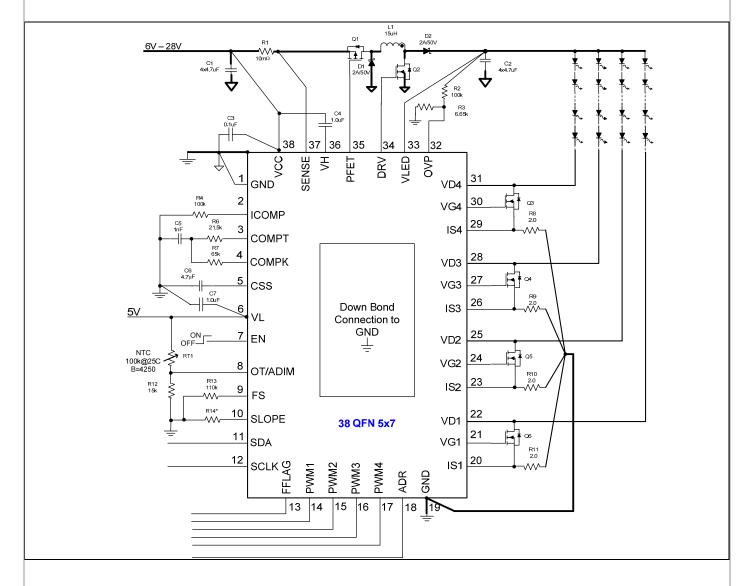

The LX2260 is a high brightness multichannel LED driver, designed for automotive automatically display illumination. It offers the designer a according to the instantaneous input and high degree of flexibility to accommodate output voltage requirements to operate in a different LED configurations (white or RGB), drive currents, input and output voltages while providing a high degree of control, protection thus and fault management of the system.

The LX2260 is very well suited for applications where high brightness LED a digital 2 wires serial bus interface (I2C backlighting is combined with a wide dimming range and high reliability such as in Automotive Infotainment, Marine or Cockpit indicators as well as information about the applications.

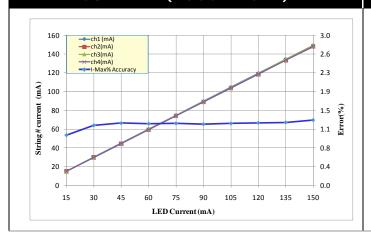

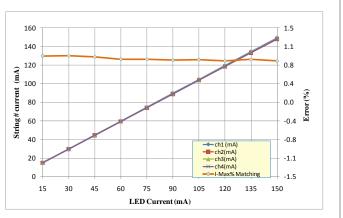

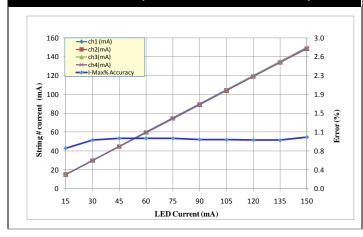

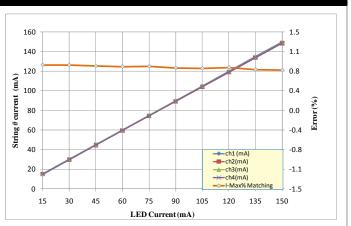

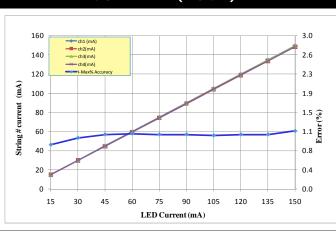

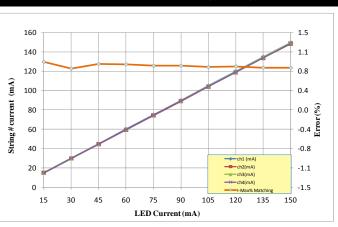

The LX2260 driver supports up to 4 independent LED strings and can be integrated in systems supporting up to 40W. The drive current of each string can be EMI. programmed up to 500mA, with a typical channel-to-channel matching accuracy within ±1.5 percent. The FETs of the boost converter and each LED current sink are external to provide the flexibility and scalability to accommodate a variety of LED configurations as well as to provide optimal thermal management of the system.

Dimming inputs providing either independent control of several white LED strings or color mixing capability for optimal a given LED temperature profile. light temperature control. PWM frequency of up to 25kHz is supported to avoid audible noise.

Rev. 1.0 12/4/2012

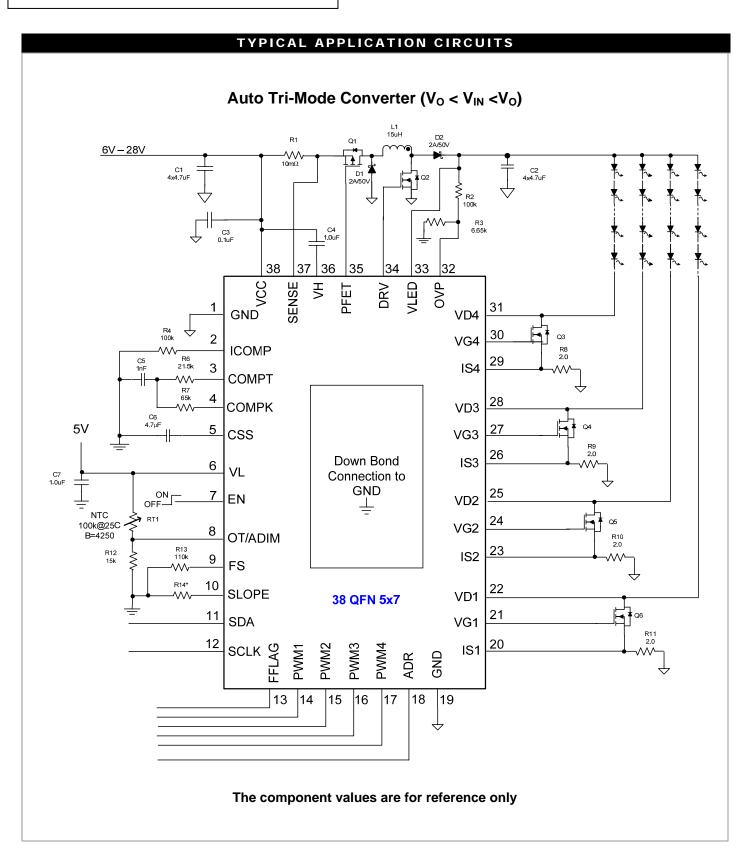

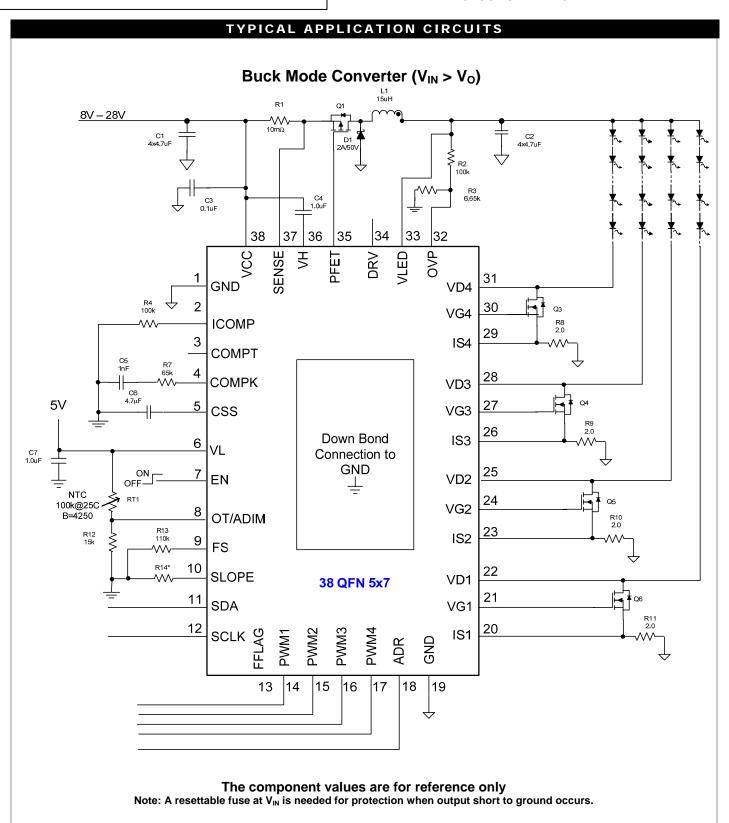

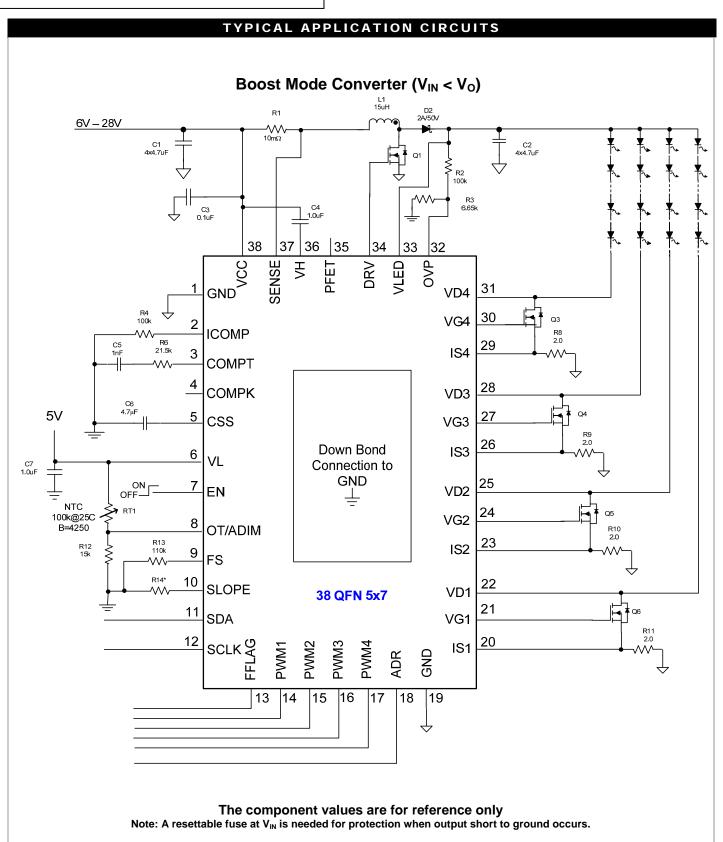

The LX2260 has the unique capability to adjust its boost, buck-boost, or buck converter mode (this is not a traditional buck/boost circuit) automatically maintaining optimally chosen LED current regulation.

Fault conditions can be reported through and SMBus compatible) and include LED short, LED open, and IC over temperature LED string voltage.

The IC also provides externally programmable LED current rise and fall time that can be used to optimize system

The LX2260 is designed to provide protection as well as continued operation in case of several fault conditions (StayLIT<sup>TM</sup>). Among the protection features we offer output short circuit protection, over-voltage protection, and over-temperature shutdown. In addition, with the use of an external thermistor to sense the LED temperature, the LED current can be compensated to stay within

#### **KEY FEATURES**

- Four LED Channels with **Independent PWM Control**

- Up to 500mA LED Current per Channel with External Power Components for Optimal Design and Thermal Management

- ±3% Current Setting Accuracy

- 1.5% Channel to Channel Current Matching

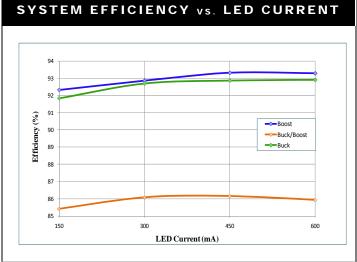

- Minimum +90% efficiency

- Programmable LED Current Amplitude via SMBus or I2C

- Unique Auto Buck, Boost, and **Buck-Boost Mode Transition**

- Analog Dimming via Light Sensor (Ambient or RGB Light) or Thermistor

- Wide Digital Dimming Range (up to 3000:1)

- SMBus and I2C Compatible Digital Diagnostic Reporting

- LED Fault Status

- String Voltage Monitoring

- LED Over Temperature Warning & Protection

- Multiple Protection including Short Circuit, Over Voltage and Over Temperature Protection

- Programmable LED Current Rise/Fall Time for EMI Control

- Automotive Grade

- AEC-Q100 Qualification

- 40V Load Dump Resistance

- -40°C to +85°C Ambient Temperature Range

### **APPLICATIONS**

- Automobile display illumination (cluster instruments, monitors, rearseat entertainment systems)

- Displays for Consumer electronics

- White or RGB LED Displays

IMPORTANT: For the most current data, consult MICROSEMI's website: http://www.microsemi.com,

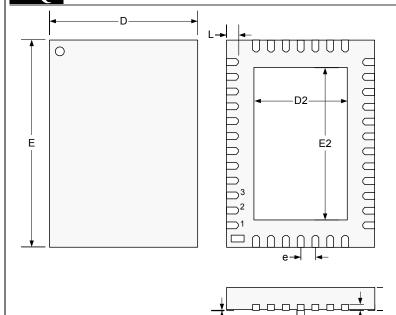

|                     | PACKAGE ORDER INFO                                                                      | THERMAL DATA                                                                                                                                       |  |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| T <sub>A</sub> (°C) | Plastic 5 x 7 mm <sup>2</sup> QFN 38-pin                                                | θ <sub>JA</sub> = 19.3 °C/W                                                                                                                        |  |  |  |  |

| - A ( •)            | RoHS Compliant / Pb-free                                                                | THERMAL RESISTANCE-JUNCTION TO AMBIENT                                                                                                             |  |  |  |  |

| -40°C to<br>85°C    | LX2260ILQ                                                                               | Junction Temperature Calculation: $TJ = TA + (PD \times \theta jA)$ .<br>The $\theta JA$ numbers are guidelines for the thermal performance of the |  |  |  |  |

| Note: Av            | ailable in Tape & Reel. Append the letters "TR" to the part number. (i.e. LX2260ILQ-TR) | device/pc-board system. All of the above assume no ambient airflow.                                                                                |  |  |  |  |

#### **PRODUCTION DATASHEET**

### **ABSOLUTE MAXIMUM RATINGS**

| Supply Input Voltage VCC, Sense, PFET, VH, VD1-4, EN, VLED            | 0.3V to 44V  |

|-----------------------------------------------------------------------|--------------|

| VH to VCC                                                             | 6V           |

| VL to GND                                                             | 0.3V to 6V   |

| SDA, SCLK, PWM1-4, FFLAG                                              | 0.3V to 6V   |

| All other pins0.3V                                                    | / to VL+0.3V |

| Maximum Junction Temperature                                          | 150°C        |

| Storage Temperature Range6                                            | 5°C to 150°C |

| Peak Package Solder Reflow Temperature (40 seconds maximum exposure). |              |

Notes: Exceeding these ratings could cause damage to the device. All voltages are with respect to GND.

Currents are positive into, negative out of specified terminal. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" are not implied. Exposure to "Absolute Maximum Ratings" for extended periods may affect device reliability.

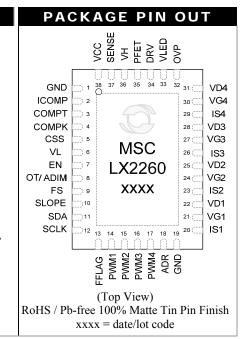

|             | FUNCTIONAL PIN DESCRIPTION |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

|-------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Pin<br>Name | Pin #                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| GND         | 1                          | GND pin: The external NFET for DC-DC converter should return to this GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| ICOMP       | 2                          | Power converters current slope compensation. Connect a resistor from this pin to GND to compensate current slope. See "slope compensation section" for detail.                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| COMPT       | 3                          | Boost Mode Compensation: Connect a resistor from this pin and the junction of the COMPK resistor and capacitor for auto tri-mode design.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| СОМРК       | 4                          | Buck and Buck-Boost mode Compensation. Connect a capacitor in series with a resistor across this pin and GND. If needed, another capacitor connected from this pin to GND for type II compensation                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| CSS         | 5                          | Feedback Soft-start: Connect a capacitor 4.7µF typical from this pin and GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| VL          | 6                          | 5V power supply output – Power Pin – Provides a regulated 5V typical to the internal and external 5V circuits. Typical 2mA current source for external use.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| EN          | 7                          | Enable Input. Pull low to put the system into sleep mode. If not used must tie to VCC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

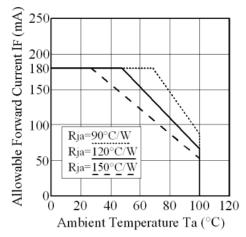

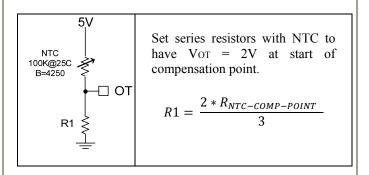

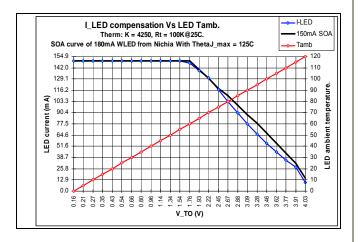

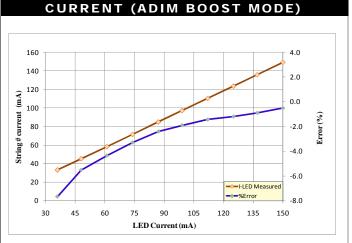

| OT/ADIM     | 8                          | LED Temperature Compensation/Analog Dimming: This input is used for LED temperature compensation. The LED current amplitude will reduce proportional with LED ambient temperature. The start of compensation is programmable with an external resistor and a thermistor. Connect pin to GND to force 100% output current when thermal compensation is not used.  By setting 1 on REG08<7>, this pin becomes analog dimming input (ADIM) which has 0V to 2V control range. Connect ADIM to GND to force 100% output current when analog dimming is not used. |  |  |  |  |  |  |  |  |

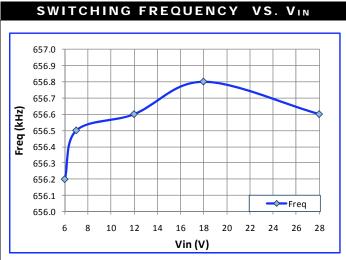

| FS          | 9                          | Oscillator Frequency Setting pin. Connect a resistor $R_{FS}$ between FS to GND to set the buck/boost frequency using the following formula:<br>Freq [kHz] = $66000/R_{FS}$ where R is in k $\Omega$ .                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|             |                 | FUNCTIONAL PIN DESCRIPTION                                                                                                                                                                                                          |

|-------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>Name | Pin #           | Description                                                                                                                                                                                                                         |

| SLOPE       | 10              | LED current rise/fall time programmable pin. Connect a resistor from this pin to GND to program LED current rise/fall time for EMI purpose. If not used, tie this pin to 5V.                                                        |

| SDA         | 11              | Serial Data In/Output. Read data for fault conditions, LED string status via drain voltage, VLED voltage. SDA also can be used to set the LED peak current amplitude by writing to register 08h. Connect to GND if SDA is not used. |

| SCLK        | 12              | Serial Clock Input. Maximum clock is 100kHz. Connect to GND if not used.                                                                                                                                                            |

| FFLAG       | 13              | Fault signal output. Open drain output. This pin goes low when a fault condition is detected.                                                                                                                                       |

| PWM1-4      | 14-17           | Pulse Width Modulated dimming signal – Signal input. PWM input can be tied together for a common PWM signal or use for individual PWM control.                                                                                      |

| ADR         | 18              | Address Setting: connect to VL, GND or leave it open for three different address choices. Refer to the address table below.                                                                                                         |

| GND         | 19              | GND pin                                                                                                                                                                                                                             |

| IS1-4       | 20,23,<br>26,29 | LED current setting. – Program this pin with an external resistor to set the LED current with 300mV internal reference voltage. I-LED = 300mV/R <sub>is</sub>                                                                       |

| VG1-4       | 21,24,<br>27,30 | Gate Drive – CMOS Output Pin: Connect to the gate of the external NMOSFET current sink. Any unused pins must be tied to ground to distinguish between intentionally unused and LED failed open.                                     |

| VD1-4       | 22,25,<br>28,31 | Drain – Signal Pin – This connects to Drain pin of the external N-MOSFET switch. The boost output voltage regulates based on the lowest VD, and the lowest voltage is kept at 0.9V (typical). Any unused pins can be left open.     |

| OVP         | 32              | Over Voltage Protection – Signal input: An external voltage divider sets the maximum LED voltage. System will stop switching when OVP limit hits, and resume when it goes lower than the limit.                                     |

| VLED        | 33              | LED voltage. Connect this pin directly to common anode strings voltage.                                                                                                                                                             |

| DRV         | 34              | Low-side NFET gate drive: Connect to the gate of the N-channel MOSFET                                                                                                                                                               |

| PFET        | 35              | High-side PMOS gate drive: Connect to gate of a PFET. When the boost output short detected or EN signal low, PFET will open. Otherwise, PFET is a converter switch in buck or buck-boost mode.                                      |

| VH          | 36              | High side power rail. Connect a 1μF 10V capacitor from this pin to VCC.                                                                                                                                                             |

| SENSE       | 37              | Converters current sense negative pin. The differential input voltage across $R_{\text{SENSE}}$ resistor used to set the peak inductor current. Use Kelvin connection directly to the $R_{\text{SENSE}}$ output side                |

| VCC         | 38              | Power supply input – Provides power to the IC. Must be closely decoupled to ground with ceramic capacitors.                                                                                                                         |

### **PRODUCTION DATASHEET**

### **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified, the following specifications apply over the operating ambient temperature of -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C and the following test conditions: VCC = 12V; V<sub>OT</sub> = 0V, EN = 3V, R<sub>FS</sub> = 100k $\Omega$ , R<sub>SLOPE</sub> = 82.5k $\Omega$ , Typical values are at T<sub>A</sub> = +25°C

| Parameter                            | Symbol               | Test Conditions / Comment                                                                               | Min    | Тур   | Max | Units    |

|--------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------|--------|-------|-----|----------|

| Input Power Supply                   | •                    |                                                                                                         |        |       |     |          |

| Input Voltage                        | VCC                  | Withstand voltage VCC = 40V                                                                             | 6      |       | 28  | V        |

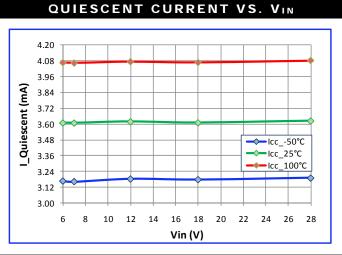

| Quiescent current                    | ICC <sub>ON</sub>    | EN > 2V, No PFET & NFET connected                                                                       |        |       | 10  | mA       |

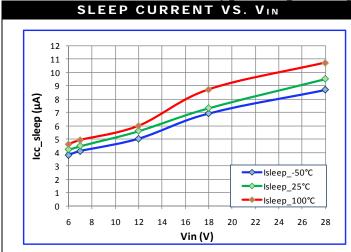

| Sleep current                        | ICC <sub>SLEEP</sub> | EN < 0.8V , VCC = 28V                                                                                   |        |       | 25  | μA       |

| Control and Logic                    |                      |                                                                                                         | '      |       | '   | <u>'</u> |

| EN Logic High                        | V <sub>ENH</sub>     |                                                                                                         | 2      |       |     | V        |

| EN Logic Low                         | V <sub>ENL</sub>     |                                                                                                         |        |       | 0.8 | V        |

| EN Current High                      | I <sub>ENH</sub>     | EN = 3.3V                                                                                               |        |       | 5   | μA       |

| EN Current Low                       | I <sub>EN-L</sub>    | EN < 0.8V                                                                                               |        |       | 5   | μA       |

| Address High Input                   | V <sub>ADRH</sub>    |                                                                                                         | VL-0.8 |       |     | V        |

| Address Low Input                    | V <sub>ADRL</sub>    |                                                                                                         |        |       | 0.8 | V        |

| Address Open                         | V <sub>ADRO</sub>    |                                                                                                         |        | VL/2  |     | V        |

| Address Input Low Current            | I <sub>ADRH</sub>    |                                                                                                         | -20    | -7    |     | μA       |

| Address Input High Current           | I <sub>ADRL</sub>    |                                                                                                         |        | 7     | 20  | μA       |

| FFLAG Output Low Voltage             | V <sub>FFLAGH</sub>  | I <sub>LOAD</sub> = 3mA                                                                                 |        |       | 0.4 | V        |

| FFLAG Output High Leakage<br>Current | V <sub>FFLAGL</sub>  | V <sub>FFLAG</sub> = 5.5V                                                                               |        |       | 10  | μA       |

| DC/DC PWM Error Amplifier            |                      |                                                                                                         | '      |       |     |          |

| Peak Output Current                  | I <sub>OUT</sub>     |                                                                                                         |        | +/-40 |     | μA       |

| Output Resistance                    | R <sub>OUT</sub>     |                                                                                                         |        | 4000  |     | kΩ       |

| Forward Transconductance             | gm                   | At EA inputs (I <sub>OUT</sub> /(V <sub>LED</sub> /20-V <sub>CSS</sub> )                                |        | 120   |     | μmho     |

| COMP Switch On Resistance            |                      | V <sub>COMPT</sub> = V <sub>COMPK</sub> = 1.6V                                                          |        | 0.5   |     | kΩ       |

| Soft Start/Drain Voltage Sens        | se Error Am          | plifier                                                                                                 | ·      |       |     |          |

|                                      |                      | Lowest VD > 700mV                                                                                       |        | +/-20 |     |          |

| CSS Source Sink Peak Current         | I <sub>CSS</sub>     | Lowest VD < 700mV                                                                                       |        | 120   | μА  |          |

| Forward Transconductance             | gm                   |                                                                                                         |        | 80    |     | μmho     |

| Output Resistance                    |                      |                                                                                                         |        | 5000  |     | kΩ       |

| Valid Output Voltage Range           | V <sub>CSS</sub>     | 1/20 of V <sub>LED</sub>                                                                                | 0.5    |       | 2   | V        |

| Start Up Time                        | T <sub>SU</sub>      | $C_{CSS}$ = 2.2 $\mu$ F, $R_{ISx}$ = 2 $\Omega$ , $V_{IS}$ setting 300mV, 100% PWM, at IS voltage > 90% |        | 5     | 20  | mS       |

| Pulse Width Modulation Inpu          | t                    |                                                                                                         |        |       |     |          |

| PWM Input Low Voltage                | V <sub>PWM L</sub>   |                                                                                                         |        |       | 0.8 | V        |

Page 6

### Four Channel High Brightness LED Driver

### **PRODUCTION DATASHEET**

### **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified, the following specifications apply over the operating ambient temperature of -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C and the following test conditions: VCC = 12V; V<sub>OT</sub> = 0V, EN = 3V, R<sub>FS</sub> = 100k $\Omega$ , R<sub>SLOPE</sub> = 82.5k $\Omega$ , Typical values are at T<sub>A</sub> = +25°C

| Parameter                                        | Symbol                  | Test Conditions / Comment                                                                                                           | Min   | Тур                                                                                                                           | Max   | Units             |

|--------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------|-------|-------------------|

| PWM Input High Voltage                           | V <sub>PWM_H</sub>      |                                                                                                                                     | 2     |                                                                                                                               |       | V                 |

| PWM Input Frequency                              | F <sub>PWM</sub>        |                                                                                                                                     | 0.1   |                                                                                                                               | 25    | kHz               |

|                                                  |                         | Digital Dimming; SLOPE = VL                                                                                                         | 2     |                                                                                                                               |       | μs                |

| Minimum PWM Pulse Width                          | PWM <sub>MIN</sub>      | Adjustable Slope Option to set t <sub>R</sub> and t <sub>F</sub>                                                                    | 2.5   |                                                                                                                               |       | +2 t <sub>R</sub> |

| PWM Input Pull-down Resistor                     | PWM <sub>R</sub>        |                                                                                                                                     |       | 100                                                                                                                           |       | kΩ                |

| PWM Input to Output Delay                        |                         | SLOPE = VL (minimum $t_R$ , $t_F$ )                                                                                                 |       | 6.5                                                                                                                           |       | μs                |

| (V <sub>IS</sub> = High)                         |                         | $R_{SLOPE} = 82.5k\Omega (t_R, t_F \sim 4\mu S)$                                                                                    |       | 9                                                                                                                             |       | μs                |

| Device Protection                                |                         |                                                                                                                                     |       |                                                                                                                               |       |                   |

| OVP Threshold Voltage                            | V <sub>TH OVP</sub>     |                                                                                                                                     | 1.87  | 1.97                                                                                                                          | 2.07  | V                 |

| Over Temperature Shutdown                        | T <sub>OVT-SHDN</sub>   | Rising temperature hysteresis, T <sub>HYS</sub> = 20°C, at junction                                                                 |       | 150                                                                                                                           |       | °C                |

| Shut Down Recovery                               | T <sub>RECOVERY</sub>   | At junction                                                                                                                         |       | 130                                                                                                                           |       | °C                |

| Over Temperature Warning                         | T <sub>OVT-WARN</sub>   | Rising temperature hysteresis, T <sub>HYS</sub> = 15°C, at junction                                                                 |       | 120                                                                                                                           |       | °C                |

| Clear Warning                                    |                         | At junction                                                                                                                         |       | 105                                                                                                                           |       | °C                |

| Load Dump Protection                             | V <sub>ISET</sub>       | V <sub>IS</sub> setting at 100%, buck-boost transition. V <sub>IN</sub> : 10V⇔40V, dV/dt = 30V/msec For Design Reference Only       |       |                                                                                                                               | 360   | mV                |

| LED Current Output                               |                         |                                                                                                                                     |       |                                                                                                                               |       |                   |

| Sink Current Overshoot                           | V <sub>ISET OVERS</sub> | V <sub>IS</sub> setting at 100% , PWM Dimming For Design Reference Only                                                             |       |                                                                                                                               | 5     | %                 |

| Sink Current Over/Under shoot in transition mode | V <sub>ISET</sub>       | V <sub>IS</sub> setting at 100% , buck-boost transition.<br>V <sub>IN</sub> : 10V⇔32V, dV/dt = 1V/msec<br>For Design Reference Only |       |                                                                                                                               | 10    | %                 |

| V-source Pk-Pk Matching Among                    | V <sub>ISET 150</sub>   | $R_{\text{sense}} = 2\Omega$ , $0.8V \le VD \le 3V$ (note 1)<br>$T_{\text{AMB}} = 25^{\circ}\text{C}$ , PWM = 100% duty cycle       |       |                                                                                                                               | 1.5   | %                 |

| Strings                                          | VISEI 150               | F <sub>PWM</sub> = 200Hz, PWM = 25% duty cycle                                                                                      |       | 100<br>6.5<br>9<br>7 1.97 2.07<br>150<br>130<br>120<br>105<br>360<br>5<br>10<br>1.5<br>3<br>1 309<br>6 313.6<br>0 1000<br>300 | %     |                   |

| Maximum IS valtaga                               | V <sub>ISx</sub>        | $R_{\text{sense}} = 2\Omega$ , Average of the four outputs                                                                          | 291   |                                                                                                                               | 309   | mV                |

| Maximum IS voltage                               | VISX                    | $R_{\text{sense}} = 2\Omega$ , Each outputs                                                                                         | 286.6 |                                                                                                                               | 313.6 | mV                |

| Minimum VD regulation                            | V <sub>Dx</sub>         | At the lowest VD pin, I <sub>DS</sub> = 150mA                                                                                       | 800   |                                                                                                                               | 1000  | mV                |

| IS Input Bias Current                            | I <sub>IS</sub>         | V <sub>IS</sub> = 300mV                                                                                                             |       |                                                                                                                               | 300   | nA                |

| DC Gain                                          | A <sub>OL</sub>         |                                                                                                                                     |       | 80                                                                                                                            |       | dB                |

| Current Source Driver Opamp                      | <b>.</b>                |                                                                                                                                     |       |                                                                                                                               |       |                   |

| On State VG Voltage Range                        | VG <sub>RANGE</sub>     | VG voltage that maintains DC accuracy                                                                                               | 1.5   |                                                                                                                               | 4     | V                 |

| Off State VG Voltage                             | VG <sub>OFF</sub>       |                                                                                                                                     |       |                                                                                                                               | 0.1   | V                 |

| VG Sink Current                                  | VG <sub>SNK</sub>       | V <sub>VG</sub> = 2.5V, V <sub>IS</sub> = 0.4V, PWM = HIGH                                                                          |       | -7                                                                                                                            |       | mA                |

| VG Source Current                                | VG <sub>SRC</sub>       | V <sub>VG</sub> = 2.5V, V <sub>IS</sub> = 0.2V, PWM = HIGH                                                                          |       | 7                                                                                                                             |       | mA                |

Copyright © 2011 Microsemi

Rev. 1.0 12/4/2012

### **PRODUCTION DATASHEET**

### **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified, the following specifications apply over the operating ambient temperature of -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C and the following test conditions: VCC = 12V; V<sub>OT</sub> = 0V, EN = 3V, R<sub>FS</sub> = 100k $\Omega$ , R<sub>SLOPE</sub> = 82.5k $\Omega$ , Typical values are at T<sub>A</sub> = +25°C

| Parameter                            | Symbol                  | Test Conditions / Comment                                                                         | Min  | Тур  | Max      | Units            |

|--------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------|------|------|----------|------------------|

| VG Load Capacitance                  | C <sub>LG</sub>         |                                                                                                   |      |      | 1500     | pF               |

| LED Current On/Off slope             |                         |                                                                                                   |      |      |          |                  |

| SLOPE Reference Voltage              | V <sub>SLOPE</sub>      |                                                                                                   |      | 2    |          | V                |

| I-LED Rise Time                      | T <sub>I-LED RISE</sub> | SLOPE = 5VL                                                                                       | 1    | 1.5  | 2.5      | μs               |

| I-LED Fall Time                      | T <sub>I-LED FALL</sub> | $F_{PWM}$ = 200Hz, PWM = 50% duty cycle $C_{LG}$ < 500pF                                          | 1    | 1.5  | 2.5      | μs               |

| I-LED Rise Time                      | T <sub>I-LED</sub> RISE | $R_{SLOPE}$ = 82.5kΩ, $T_{RISE}/T_{FALL}$ = 10% to 90% $F_{PWM}$ = 200 Fz, PWM = 50% duty cycle   |      | 4.2  | 5.5      | μs               |

| I-LED Fall Time                      | T <sub>I-LED FALL</sub> | $C_{LG}$ < 500pF                                                                                  |      | 4.2  | 5.5      | μs               |

| LED Temperature Compensa             | tion (LED C             | urrent Profile)                                                                                   |      | '    | <u>'</u> |                  |

| OT Start Threshold Voltage           | V <sub>оттн</sub>       | I-LED starts compensation at I-LED = 95% current setting. Register 08h = 011111111; PWM1-4 = High | 1.8  | 2.0  | 2.2      | V                |

| OT Max_Voltage Compensation          | V <sub>от</sub>         | At stop point, I-LED = 15% current setting. Register 08h = 011111111; PWM1-4 = High               | 3.3  | 3.5  | 3.8      | V                |

| or max_voltage compensation          | *01                     | And goes down to 6.7% when VTH OT >4.5V. PWM1-4 = High; Register 08h= 011111111                   |      | 3.7  | 3.95     | V                |

| OT Input Bias Current                | I <sub>OTIIB</sub>      |                                                                                                   |      |      | 1        | μA               |

| Analog Dimming (Analog di            | mming can               | be set via SMBus or Fuse)                                                                         |      |      |          |                  |

| AD Voltage                           | V <sub>AD</sub>         | I-LED = 95%; PWM1-4 = HIGH;<br>Register 08h = 01111111                                            | 1.8  | 1.9  | 2.0      | V                |

| 7.D Voltage                          | ▼ AD                    | I-LED = 6.7%; PWM1-4 = HIGH;<br>Register 08h = 01111111                                           | 0.05 | 0.2  | 0.34     |                  |

| AD Input Bias Current                | AD <sub>IIB</sub>       |                                                                                                   | -1   |      | 1        | μA               |

| Analog Control Output Range          | V <sub>IS</sub>         | Register 08h = 011111111, PWM1-4 = High                                                           | 5    |      | 100      | %                |

| SMBus LED Peak Current Ad            | justment                |                                                                                                   |      |      |          |                  |

| Adjustment Range                     | I <sub>PADJ</sub>       | V <sub>IS</sub> = 300mV represents maximum current setting                                        | 15.4 |      | 100      | %V <sub>IS</sub> |

| Resolution                           | I <sub>RES</sub>        | 2 mV translates out to be 7 bits DAC                                                              |      | 2    |          | mV               |

| LED short/open protection            |                         |                                                                                                   |      |      |          |                  |

| LED Short Threshold Voltage (note 1) | VDx <sub>SHORT</sub>    | F <sub>PWM</sub> = 25kHz,<br>Duty cycle > 7µsec                                                   | 6.7  | 7.2  | 7.7      | V                |

| Derated IS Voltage                   |                         | VD > 7.75                                                                                         |      | 10   |          | %                |

| LED Open Threshold Voltage           | VDx <sub>OPEN</sub>     | F <sub>PWM</sub> = 25kHz, PWM = 10% duty cycle                                                    |      | 0.24 |          | V                |

| Inductor Over Current protect        | tion                    |                                                                                                   |      |      |          |                  |

| Maximum Short Circuit Current        | I <sub>LSHORT</sub>     | With 10mΩ current sense resistor For Design Reference Only                                        |      | 10   |          | А                |

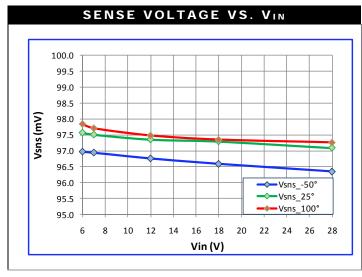

| Over Current Threshold Voltage       | V <sub>oc</sub>         | At current sense inputs                                                                           |      | 90   |          | mV               |

Copyright © 2011 Microsemi Page 7

### **PRODUCTION DATASHEET**

### **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified, the following specifications apply over the operating ambient temperature of -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C and the following test conditions: VCC = 12V; V<sub>OT</sub> = 0V, EN = 3V, R<sub>FS</sub> = 100k $\Omega$ , R<sub>SLOPE</sub> = 82.5k $\Omega$ , Typical values are at T<sub>A</sub> = +25°C

| Parameter Symb                     |                       | Test Conditions / Comment                                                                     | Min   | Тур   | Max      | Units |

|------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------|-------|-------|----------|-------|

| SENSE Input                        |                       |                                                                                               |       |       |          |       |

| Sense Input Voltage Range          | V <sub>SENSE</sub>    |                                                                                               |       |       | 100      | mV    |

| Sense Input Bias Current           | I <sub>SENSE</sub>    |                                                                                               |       | 0.3   |          | μA    |

| VL Regulator (5.0V)                |                       |                                                                                               |       |       | <u>'</u> |       |

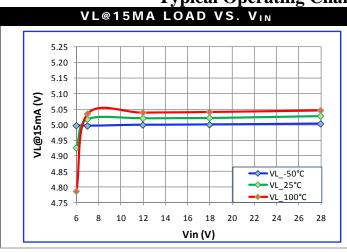

| VL Output                          | 5V                    | 6V ≤ VCC ≤ 28V; no external load                                                              | 4.75  | 5.00  | 5.25     | V     |

| VL Source Current                  | 5V <sub>CURRENT</sub> | External load current, VCC = 6V,<br>VL drop by ≤ 5%                                           |       | 2     |          | mA    |

| UVLO                               | VL <sub>UVLO</sub>    | VL rising, VHYS = 0.50V                                                                       | 3.75  | 4.25  | 4.65     | V     |

| VH (VCC-5.25V) Regulator           | <u>'</u>              |                                                                                               | ·     |       | •        |       |

| VH Output Voltage                  | VH                    | 6V ≤ VCC ≤ 28V; 0mA ≤ IVH ≤ 15mA<br>Reference to VCC                                          | -4.75 | -5.25 | -5.5     | V     |

| UVLO                               | VH <sub>UVLO</sub>    | 'H falling, VHYS = 0.50V. Internal POR ctivates on VH falling UVLO threshold, eference to VCC |       | -4.25 |          | V     |

| Oscillator                         |                       |                                                                                               | ·     |       |          |       |

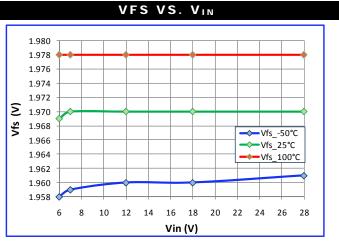

| FS Reference Voltage               | V <sub>FS</sub>       |                                                                                               |       | 2     |          | V     |

| Oscillator Frequency               | F <sub>SW</sub>       | RFS = 100kΩ                                                                                   | 600   | 670   | 740      | kHz   |

| Oscillator Frequency Setting Range | F <sub>RANGE</sub>    |                                                                                               | 400   |       | 800      | kHz   |

| DC/DC Switching NFET Drive         | er                    |                                                                                               | ·     |       |          |       |

| DRV Voltage High                   | V <sub>DRVH</sub>     |                                                                                               |       | 5     |          | V     |

| DRV Rise Time                      | T <sub>RISE</sub>     | CL = 1000pF                                                                                   |       | 26    |          | ns    |

| DRV Fall Time                      | T <sub>FALL</sub>     | CL = 1000pF                                                                                   |       | 15    |          | ns    |

| Off Voltage                        | V <sub>DRVOFF</sub>   | EN = 0V                                                                                       |       | 0     |          | V     |

| DC/DC Switching PFET Drive         | er                    |                                                                                               | ·     |       |          |       |

| PFET High Voltage                  | V <sub>PFETH</sub>    | EN = 0V, refer to VCC                                                                         |       | 0     |          | V     |

| PFET Low Voltage                   | V <sub>PPFETL</sub>   | Refer to VCC                                                                                  |       | -5.25 |          | V     |

| PFET Rise Time                     | T <sub>RISE</sub>     | CL = 1000pF                                                                                   |       | 14    |          | ns    |

| PFET Fall Time                     | T <sub>FALL</sub>     | CL = 1000pF                                                                                   |       | 25    |          | ns    |

| Converter mode condition           |                       |                                                                                               | ·     |       |          |       |

| Boost to Buck-Boost Transition     | BS-BB                 | At VLED. VLED falling                                                                         |       | 13.76 |          | V     |

| Buck-Boost to Boost Transition     | BB-BS                 | At VLED. VLED rising                                                                          |       | 14.65 |          | V     |

| Buck to Buck-Boost Transition      | BK-B                  | At VLED. VLED rising                                                                          |       | 9.21  |          | V     |

| Buck-Boost to Buck Transition      | BB-BK                 | At VLED. VLED falling                                                                         |       | 8.41  |          | V     |

#### **PRODUCTION DATASHEET**

### **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified, the following specifications apply over the operating ambient temperature of -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C and the following test conditions: VCC = 12V; V<sub>OT</sub> = 0V, EN = 3V, R<sub>FS</sub> = 100k $\Omega$ , R<sub>SLOPE</sub> = 82.5k $\Omega$ , Typical values are at T<sub>A</sub> = +25°C

| Parameter                                                         | Symbol              | Test Conditions / Comment                                                                               | Min | Тур | Max | Units |  |

|-------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|--|

| Overall System Efficacy                                           | η                   | VIN = 12V& 26V, VS setting at 100%,<br>PWM = 100% (Boost mode & Buck Mode)<br>For Design Reference Only | 90  |     |     | %     |  |

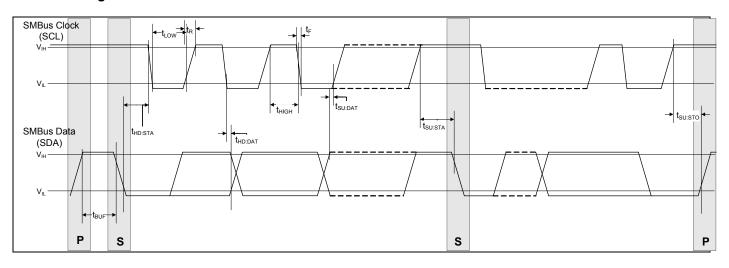

| SMBus                                                             |                     |                                                                                                         |     |     |     |       |  |

| SDA, SCLK Input Low Voltage                                       | I <sub>LV</sub>     |                                                                                                         |     |     | 0.7 | V     |  |

| SDA, SCLK Input High Voltage                                      | I <sub>HV</sub>     |                                                                                                         | 2   |     |     | V     |  |

| SDA, SCLK Input Hysteresis                                        | IH <sub>YS</sub>    |                                                                                                         |     | 100 |     | mV    |  |

| SDA,SCLK Input Bias Current                                       | I <sub>IB</sub>     |                                                                                                         | -5  |     | +5  | μA    |  |

| SDA Output Low Sink Current                                       | Osnk                | V <sub>SDA</sub> = 0.4V                                                                                 | 4   |     |     | mA    |  |

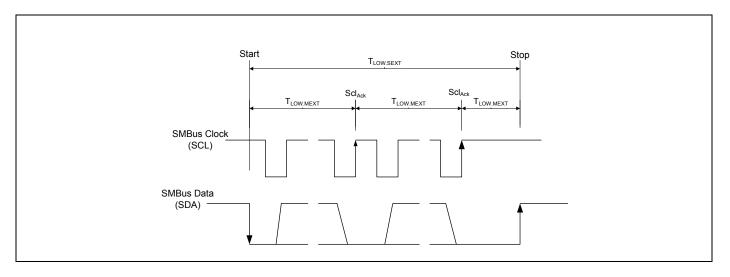

| SMBus Frequency                                                   | F <sub>SMBUS</sub>  |                                                                                                         | 10  |     | 100 | kHz   |  |

| SMBus Free time                                                   | T <sub>BUF</sub>    |                                                                                                         | 4.7 |     |     | μs    |  |

| SCLK Serial Clock High Period                                     | T <sub>HIGH</sub>   |                                                                                                         | 4   |     |     | μs    |  |

| SCLK Serial Clock Low Period                                      | T <sub>LOW</sub>    |                                                                                                         | 4.7 |     |     | μs    |  |

| Start Condition Set-up Time                                       | T <sub>SU:STA</sub> |                                                                                                         | 4.7 |     |     | μs    |  |

| Start Condition Hold-up Time                                      | T <sub>HD:STA</sub> |                                                                                                         | 4   |     |     | μs    |  |

| Stop Condition Set-up Time from SCLK                              | T <sub>SU:STO</sub> |                                                                                                         | 4   |     |     | μs    |  |

| SDA Valid to SCLK Rising Edge<br>Set-up Time, Slave Clocking Data | T <sub>SU:DAT</sub> |                                                                                                         | 250 |     |     | ns    |  |

| SCLK Falling Edge to SDA<br>Transition                            | T <sub>HD:DAT</sub> |                                                                                                         | 0   |     |     | ns    |  |

| SCLK Falling Edge to SDA Valid,<br>Reading Out Data               | T <sub>DV</sub>     |                                                                                                         | 200 |     |     | ns    |  |

**Note:** 1. When the different  $V_{DRAIN}$  voltages are more than 2V, then a single LED short may shut off the string that has a highest  $V_{DRAIN}$  (VD hits the limit). However  $V_{SOURCE}$  pk-pk matching will not be effected in this circumstance.

#### **PRODUCTION DATASHEET**

### SERIAL INTERFACE

#### **SMBus Interface**

LX2260 is a nine-register device which uses SMBus or I<sup>2</sup>C protocols to communicate with the host system. All registers are defined as full byte wide. Some registers contain reserved (undefined) bits with a default value of "0", or are read only bits that are status indicators. Two of the nine registers are capable of both read and write, and seven registers are read only. See the LX2260 Register Definitions section for details.

The LX2260 communicates over the SMBus and operates in a "slave" mode receiving commands and sending / receiving data to / from the host or "master". Only standard two-wire SMBus and  $I^2C$  compatible serial bus and protocols may be used for this device. The LX2260 can be configured for one of the three addresses by connecting the ADR input pin to ground,  $V_{DD}$ , or simply leaving it OPEN.

### **Address Strapping Codes**

| Option # | ADR         | Address   |

|----------|-------------|-----------|

| 1        | GND         | 0101 100b |

| 2        | OPEN        | 0101 110b |

| 3        | $V_{ m DD}$ | 0101 111b |

In this document, the SMBUs address occupies high seven bits of an eight bit field on the bus, the low bit is always the R/W bit.

#### Address = 0101100xb

| 1 | 7             | 1  | 1 | 8         | 1 | 1 |

|---|---------------|----|---|-----------|---|---|

| s | Slave Address | Wr | Α | Data Byte | Α | Р |

|   | 0101100       | 0  |   |           |   |   |

### Address = 0101110xb

| 1 | 7             | 1  | 1 | 8         | 1 | 1 |

|---|---------------|----|---|-----------|---|---|

| s | Slave Address | Wr | A | Data Byte | Α | Р |

|   | 0101110       | 0  |   |           |   |   |

### Address = 0101111xb

| 1 | 7             | 1  | 1 | 8         | 1 | 1 |

|---|---------------|----|---|-----------|---|---|

| S | Slave Address | Wr | Α | Data Byte | Α | Р |

|   | 0101111       | 0  |   |           |   |   |

#### SMBus PROTOCOL

The only required command protocols are SMBus Send Byte, Receive Byte, Read Byte / Word, and the Write Byte / Word protocols.

Writes to registers can be performed by either the SMBus Write Byte / Word protocols and / or by internal IC logic, depending on the register type.

Read can be performed on all registers by issuing the Read Byte / Word protocol. Read Only registers can be written only by internal logics. Their contents will not be affected by SMBus write commands.

When LX2260 is initially powered, it will first test the address selection pin input to determine its own address and then look for its unique address each time it detects a "Start Condition". If the address does not match, the LX2260 ignores all bus activity until it encounters another "Start Condition".

### **SMBus Packet Protocol Diagram Element Key**

| s | Slave Address | Wr | Α | Data Byte | Α | Р |

|---|---------------|----|---|-----------|---|---|

|   |               |    | Х |           | Х |   |

S Start Condition

**Rd** Read (bit value of 1)

**Wr** Write (bit value of 0)

A Acknowledge ('0' for an ACK, or '1' for a NACK)

P Stop Condition

Command Code Register Address

☐ Master-to-Slave ☐ Slave-to-Master

Protocols used to communicate with LX2260 must be per standard SMBus specification version 2.0 or higher.

#### **PRODUCTION DATASHEET**

### SERIAL INTERFACE

### **SMBus Timing Measurement**

### **Register Definitions**

The LX2260 includes a registers to monitor the fault status. The slave address is set by the ADR signal inputs as follows:

**VD Register:** Address is 00h to 03h. This register has 8 bits that allows monitoring the drain voltage (VD). This voltage will reveal the string status, i.e., LED short/open. It is suggested that the input PWM duty cycle be reduced when a LED short is detected to avoid LED current sink NFET overheating.

VLED Register: Address is 04h. This register has 8 bits that allow monitoring the Boost output voltage (VLED).

String 1 & 2 Status Register: Address is 05h. This register has 8 status bits that allows monitoring the string 1 & 2 status.

String 3 & 4 Status Register: Address is 06h. This register has 8 status bits that allows monitoring the string 3 & 4 status.

**Fault/Status Register:** Address is 07h. This register has 8 status bits that allows monitoring the backlight controller's operating state.

| REGISTER 00h | VD1 (drain voltage monitoring)                |

|--------------|-----------------------------------------------|

| REGISTER 01h | VD2 (drain voltage monitoring)                |

| REGISTER 02h | VD3 (drain voltage monitoring)                |

| REGISTER 03h | VD4 (drain voltage monitoring)                |

| REGISTER 04h | VLED (LED Anode voltage monitoring)           |

| REGISTER 05h | String 1 & 2 status                           |

| REGISTER 06h | String 3 & 4 status                           |

| REGISTER 07h | Faults                                        |

| REGISTER 08h | LED Peak Current Reference Voltage Adjustment |

| REGISTER 00h to 03h |           |           | Drain voltage | monitoring | DEFA      | 00        |           |

|---------------------|-----------|-----------|---------------|------------|-----------|-----------|-----------|

|                     |           |           |               |            |           |           |           |

| VD                  | VD        | VD        | VD            | VD         | VD        | VD        | VD        |

| Bit 7 (R)           | Bit 6 (R) | Bit 5 (R) | Bit 4 (R)     | Bit 3 (R)  | Bit 2 (R) | Bit 1 (R) | Bit 0 (R) |

| BIT FIELD   | DEFINITION    | DESCRIPTION                                                      |

|-------------|---------------|------------------------------------------------------------------|

| Bit 0-7 (R) | Drain voltage | 8-bit drain voltage monitoring. 256 steps for 8V. (bit 7 is MSB) |

### **PRODUCTION DATASHEET**

### SERIAL INTERFACE

| R         | REGISTER 04h |           | LED voltage m | onitoring | DEFAULT VALUE 0x00 |           |           |

|-----------|--------------|-----------|---------------|-----------|--------------------|-----------|-----------|

|           |              |           |               |           |                    |           |           |

| VLED      | VLED         | VLED      | VLED          | VLED      | VLED               | VLED      | VLED      |

| Bit 7 (R) | Bit 6 (R)    | Bit 5 (R) | Bit 4 (R)     | Bit 3 (R) | Bit 2 (R)          | Bit 1 (R) | Bit 0 (R) |

|   | BIT FIELD   | DEFINITION  | DESCRIPTION                                                       |

|---|-------------|-------------|-------------------------------------------------------------------|

| Ī | Bit 0-7 (R) | LED voltage | 8-bit LED voltage monitoring. 256 steps for 67.9V. (bit 7 is MSB) |

| REG           | REGISTER 05h: Stri |           | g 1&2 Status | Register  | DEFA      | x00       |           |

|---------------|--------------------|-----------|--------------|-----------|-----------|-----------|-----------|

|               |                    |           |              |           |           |           |           |

| String #2 not | String #1 not      | S1_OV     | S1_OPEN      | S1_NOTUSE | S2_OV     | S2_OPEN   | S2_NOTUSE |

| Used          | Used               |           |              |           |           |           |           |

| Bit 7 (W)     | Bit 6 (W)          | Bit 5 (R) | Bit 4 (R)    | Bit 3 (R) | Bit 2 (R) | Bit 1 (R) | Bit 0 (R) |

| BIT FIELD | DEFINITION            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 7     | String #1 not<br>Used | Set 1 when string #1 is not used to mask string faults on the string.  Bit 6 and 7 are written to register 05h by the systems via SMBus to let the LX2260 know the unused string so the LX2260 can remove it from the fault detection/reporting.  At power up system must disregard fault reporting and FFLAG (software timer) until the systems has finished setting string not used bit (set bit 6 and or 7 to high) and have received acknowledge from LX2260. LX2260 sends an acknowledgement after masking string fault. |

| Bit 6     | String #2 not<br>Used | Set 1 when string #2 in not used to mask string faults on the string.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Bit 5     | S1_OV                 | String 1 Over Voltage $(1 = VD > 6.75V)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Bit 4     | S1_OPEN               | String 1 Open (1 = string open)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Bit 3     | S1_NOTUSE             | String 1 status (1 = string is not used)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Bit 2     | S2_OV                 | String 2 Over Voltage $(1 = VD > 6.75V)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Bit 1     | S2_OPEN               | String 2 Open (1 = string open)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Bit 0     | S2_NOTUSE             | String 2 status (1 = string is not used)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BIT FIELD             | DEFINITION            |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DESCR               | IPTION             |           |            |

|-----------------------|-----------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------|-----------|------------|

| RI                    | EGISTER 06h           | String 3&4 Status Register                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     | DEFAULT VALUE 0x00 |           |            |

| String #4 not<br>Used | String #3 not<br>Used | S3_OV                                                                                   | S3_OPEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | S3_NOTUSE           | S4_OV              | S4_OPEN   | S4_ NOTUSE |

| Bit 7 (W)             | Bit 6 (W)             | Bit 5 (R)                                                                               | Bit 4 (R)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Bit 3 (R)           | Bit 2 (R)          | Bit 1 (R) | Bit 0 (R)  |

| Bit 7                 | String #3 not<br>Used | register 06h by<br>LX2260 can re<br>At power up sy<br>systems has fin<br>acknowledge fi | Set 1 when string #3 in not used to mask string faults on the string. Bit 6 and 7 are written to register 06h by the systems via SMBus to let the LX2260 know the unused string so the LX2260 can remove it from the fault detection/reporting.  At power up system must disregard fault reporting and FFLAG (software timer) until the systems has finished setting string not used bit (set bit 6 and or 7 to high) and have received acknowledge from LX2260. LX2260 send acknowledge after masking string fault |                     |                    |           |            |

| Bit 6                 | String #4 not<br>Used | Set 1 when stri                                                                         | ng #4 in not us                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ed to mask sting fa | ults on the st     | ring.     |            |

| Bit 5                 | S3_OV                 | String 3 Over V                                                                         | Voltage $(1 = VI)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | O > 6.75V)          |                    |           |            |

| Bit 4                 | S3_OPEN               | String 3 Open                                                                           | String 3 Open (1 = string open)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     |                    |           |            |

| Bit 3                 | S3_NOTUSE             | String 3 status (1 = string is not used)                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     |                    |           |            |

| Bit 2                 | S4_OV                 | String 4 Over Voltage $(1 = VD > 6.75V)$                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     |                    |           |            |

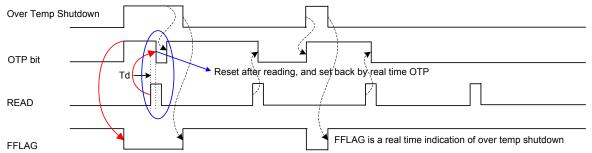

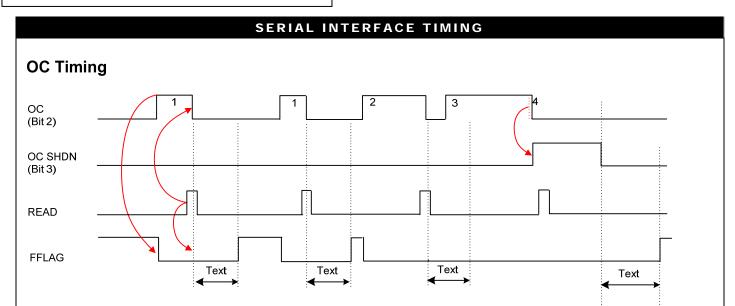

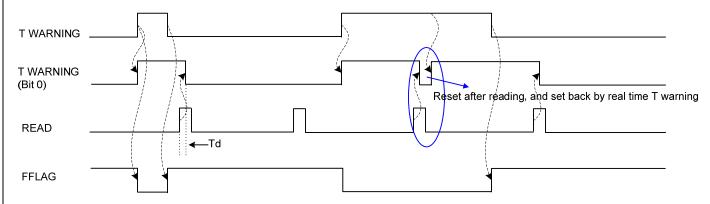

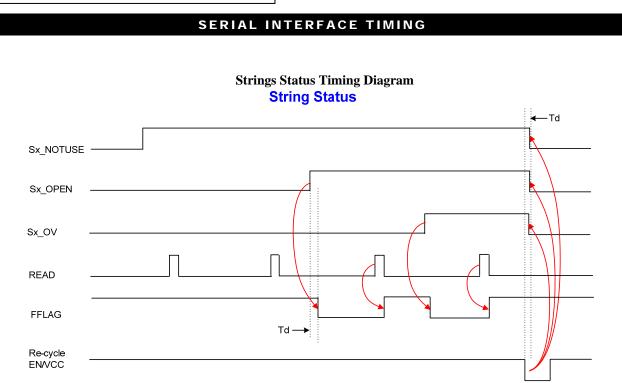

| Bit 1                 | S4_OPEN               | String 4 Open                                                                           | (1 = string oper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1)                  |                    |           |            |