# Dual N-Channel PowerTrench<sup>®</sup> MOSFETs 30 V, 22 m $\Omega$ , 10 m $\Omega$

### Features

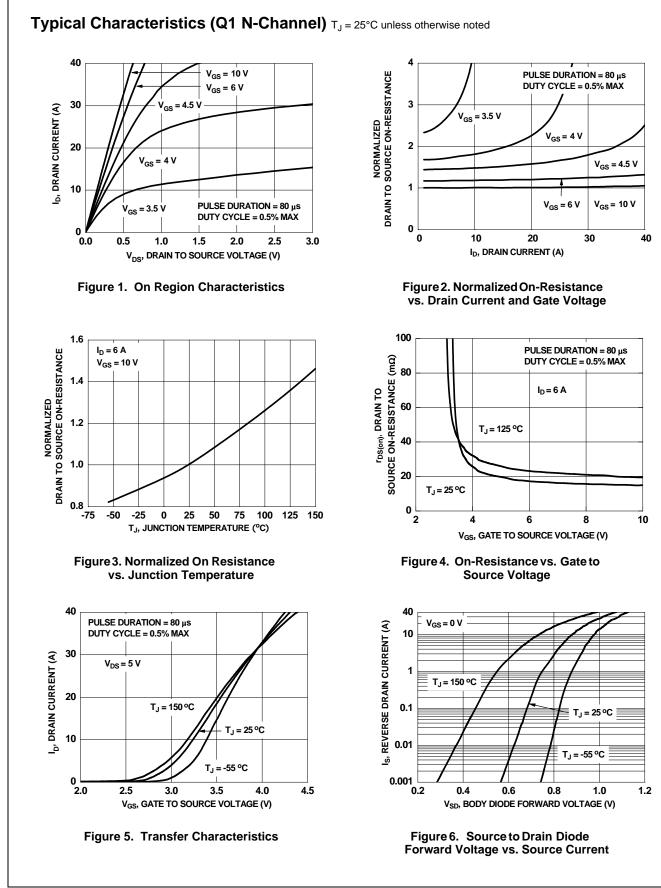

- Q1: N-Channel

- Max  $r_{DS(on)}$  = 22 m $\Omega$  at  $V_{GS}$  = 10 V,  $I_D$  = 6 A

- Max  $r_{DS(on)}$  = 34 m $\Omega$  at V<sub>GS</sub> = 4.5 V, I<sub>D</sub> = 5 A

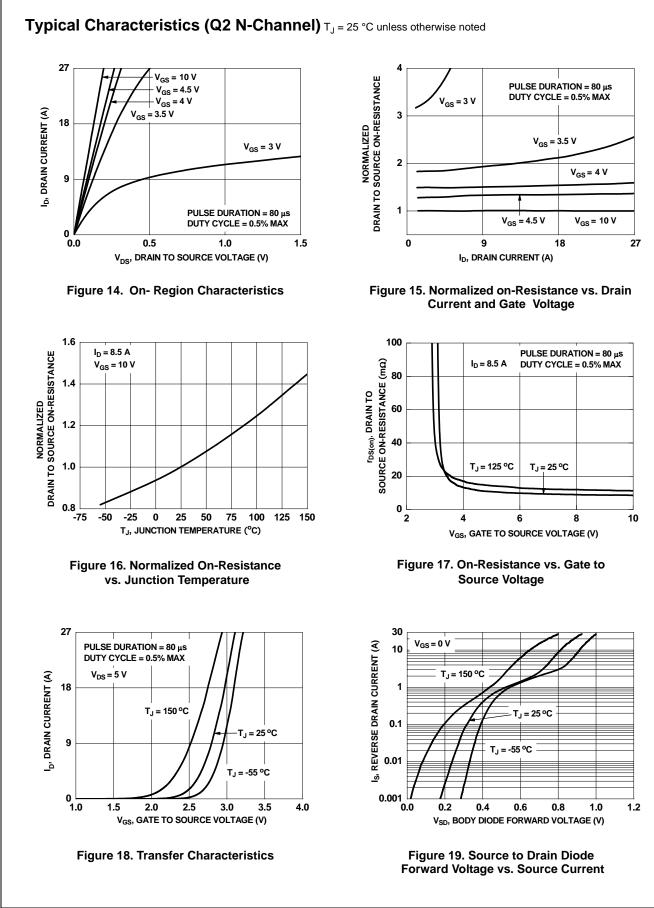

#### Q2: N-Channel

- Max  $r_{DS(on)}$  = 10 m $\Omega$  at V<sub>GS</sub> = 10 V, I<sub>D</sub> = 8.5 A

- Max  $r_{DS(on)}$  = 13.5 m $\Omega$  at V<sub>GS</sub> = 4.5 V, I<sub>D</sub> = 7.2 A

- RoHS Compliant

## **General Description**

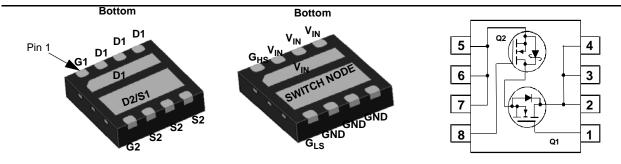

This device includes two specialized N-Channel MOSFETs in a dual power33 (3mm X 3mm MLP) package. The switch node has been internally connected to enable easy placement and routing of synchronous buck converters. The control MOSFET (Q1) and synchronous MOSFET (Q2) have been designed to provide optimal power efficiency.

## Applications

- Mobile Computing

- Mobile Internet Devices

- General Purpose Point of Load

Power33

### **MOSFET Maximum Ratings** $T_C = 25^{\circ}C$ unless otherwise noted

| Symbol                            | Parameter                                                  |                                                         |          | Q1                | Q2                | Units    |

|-----------------------------------|------------------------------------------------------------|---------------------------------------------------------|----------|-------------------|-------------------|----------|

| V <sub>DS</sub>                   | Drain to Source Voltage                                    |                                                         |          | 30                | 30                | V        |

| V <sub>GS</sub>                   | Gate to Source Voltage                                     |                                                         | (Note 4) | ±20               | ±20               | V        |

|                                   | Drain Current -Continuous (Package limited)                | T <sub>C</sub> = 25 °C                                  |          | 18                | 13                |          |

|                                   | -Continuous (Silicon limited)                              | T <sub>C</sub> = 25 °C                                  |          | 23                | 46                | <u>,</u> |

| D                                 | -Continuous                                                | T <sub>A</sub> = 25 °C                                  |          | 7 <sup>1a</sup>   | 13 <sup>1b</sup>  | A        |

|                                   | -Pulsed                                                    | -Pulsed                                                 |          |                   |                   |          |

| E <sub>AS</sub>                   | Single Pulse Avalanche Energy                              |                                                         | (Note 3) | 12                | 32                |          |

| P <sub>D</sub>                    | Power Dissipation for Single Operation                     | T <sub>A</sub> = 25°C                                   |          | 1.9 <sup>1a</sup> | 2.5 <sup>1b</sup> | 14/      |

|                                   | Power Dissipation for Single Operation $T_A = 25^{\circ}C$ |                                                         |          | 0.7 <sup>1c</sup> | 1.0 <sup>1d</sup> | W        |

| T <sub>J</sub> , T <sub>STG</sub> | Operating and Storage Junction Temperature F               | ting and Storage Junction Temperature Range -55 to +150 |          |                   | +150              | °C       |

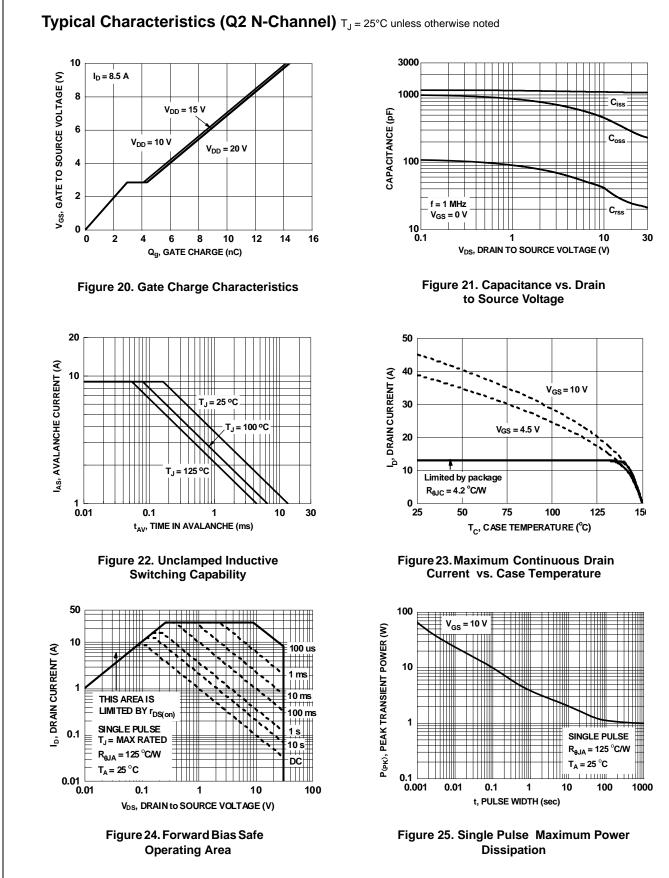

#### **Thermal Characteristics**

| $R_{\thetaJA}$  | Thermal Resistance, Junction to Ambient |                   | 50 <sup>1b</sup>  |      |

|-----------------|-----------------------------------------|-------------------|-------------------|------|

| $R_{\thetaJA}$  | Thermal Resistance, Junction to Ambient | 180 <sup>1c</sup> | 125 <sup>1d</sup> | °C/W |

| $R_{\theta,JC}$ | Thermal Resistance, Junction to Case    | 7.5               | 4.2               | ]    |

#### Package Marking and Ordering Information

| Device Marking | Device    | Package  | Reel Size | Tape Width | Quantity   |

|----------------|-----------|----------|-----------|------------|------------|

| FDMC7200S      | FDMC7200S | Power 33 | 13"       | 12 mm      | 3000 units |

June 2014

| Ū       |

|---------|

| Ξ       |

| ō       |

|         |

| N       |

| B       |

| õ       |

|         |

| ž       |

| a       |

| =       |

| Ż       |

| ò       |

| ÷       |

| an      |

| 2       |

| ٦<br>C  |

| Ψ.      |

| Τ       |

| Q       |

| Ňe      |

| Ð       |

| Ĥ       |

| 2       |

| Ĕ       |

| ิด      |

| 7       |

| B       |

| Ζ       |

| ō       |

| MOSFETs |

| Ť       |

| Π.      |

| Ä       |

| 0,      |

|         |

| Symbol                                 | Parameter                                                   | Test Conditions                                                                                                                       | Туре     | Min        | Тур                 | Max                  | Units    |  |

|----------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------|------------|---------------------|----------------------|----------|--|

| Off Chara                              | acteristics                                                 |                                                                                                                                       |          |            |                     |                      |          |  |

| BV <sub>DSS</sub>                      | Drain to Source Breakdown Voltage                           | $I_D = 250 \ \mu A, V_{GS} = 0 \ V$<br>$I_D = 1mA, V_{GS} = 0 \ V$                                                                    | Q1<br>Q2 | 30<br>30   |                     |                      | V        |  |

| $\frac{\Delta BV_{DSS}}{\Delta T_{J}}$ | Breakdown Voltage Temperature<br>Coefficient                | $I_D = 250 \ \mu$ A, referenced to 25°C<br>$I_D = 1$ mA, referenced to 25°C                                                           | Q1<br>Q2 |            | 14<br>13            |                      | mV/°C    |  |

| I <sub>DSS</sub>                       | Zero Gate Voltage Drain Current                             | $V_{DS} = 24$ V, $V_{GS} = 0$ V                                                                                                       | Q1<br>Q2 |            |                     | 1<br>500             | μA       |  |

| I <sub>GSS</sub>                       | Gate to Source Leakage Current                              | $V_{GS} = \pm 20$ V, $V_{DS} = 0$ V                                                                                                   | Q1<br>Q2 |            |                     | 100<br>100           | nA<br>nA |  |

| On Chara                               | octeristics                                                 |                                                                                                                                       |          |            |                     |                      |          |  |

| V <sub>GS(th)</sub>                    | Gate to Source Threshold Voltage                            | $V_{GS} = V_{DS}$ , $I_D = 250 \ \mu A$<br>$V_{GS} = V_{DS}$ , $I_D = 1mA$                                                            | Q1<br>Q2 | 1.0<br>1.0 | 2.3<br>2.0          | 3.0<br>3.0           | V        |  |

| $\frac{\Delta V_{GS(th)}}{\Delta T_J}$ | Gate to Source Threshold Voltage<br>Temperature Coefficient | $I_D = 250 \ \mu$ A, referenced to 25°C<br>$I_D = 1$ mA, referenced to 25°C                                                           | Q1<br>Q2 |            | -5<br>-6            |                      | mV/°C    |  |

|                                        | Citatia Dasia ta Caura Ora Dasiatana                        |                                                                                                                                       | Q1       |            | 17<br>25<br>23      | 22<br>34<br>30       | — mΩ     |  |

| r <sub>DS(on)</sub>                    | Static Drain to Source On Resistance                        |                                                                                                                                       | Q2       |            | 7.8<br>10.3<br>11.4 | 10.0<br>13.5<br>13.1 | 11152    |  |

| 9 <sub>FS</sub>                        | Forward Transconductance                                    | $V_{DD} = 5 V, I_D = 6 A$<br>$V_{DD} = 5 V, I_D = 8.5 A$                                                                              | Q1<br>Q2 |            | 29<br>43            |                      | S        |  |

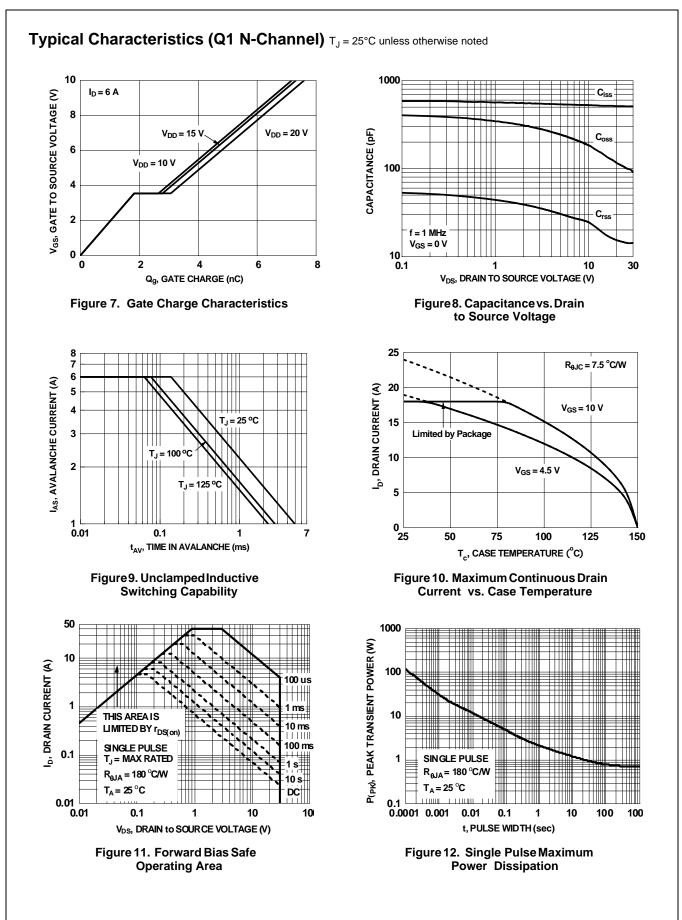

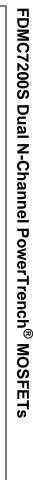

| Dynamic                                | Characteristics                                             |                                                                                                                                       |          |            |                     |                      |          |  |

| C <sub>iss</sub>                       | Input Capacitance                                           |                                                                                                                                       | Q1<br>Q2 |            | 495<br>1080         | 660<br>1436          | pF       |  |

| C <sub>oss</sub>                       | Output Capacitance                                          | V <sub>DS</sub> = 15 V, V <sub>GS</sub> = 0 V, f = 1 MHZ                                                                              | Q1<br>Q2 |            | 145<br>373          | 195<br>495           | pF       |  |

| C <sub>rss</sub>                       | Reverse Transfer Capacitance                                |                                                                                                                                       | Q1<br>Q2 |            | 20<br>35            | 30<br>52             | pF       |  |

| R <sub>g</sub>                         | Gate Resistance                                             |                                                                                                                                       | Q1<br>Q2 | 0.2<br>0.2 | 1.4<br>1.2          | 4.2<br>3.6           | Ω        |  |

| Switching                              | g Characteristics                                           |                                                                                                                                       |          |            |                     |                      |          |  |

| t <sub>d(on)</sub>                     | Turn-On Delay Time                                          | Q1                                                                                                                                    | Q1<br>Q2 |            | 11<br>7.6           | 20<br>15             | ns       |  |

| t <sub>r</sub>                         | Rise Time                                                   | $V_{\text{DD}} = 15 \text{ V}, \text{ I}_{\text{D}} = 1 \text{ A},$ $V_{\text{GS}} = 10 \text{ V}, \text{ R}_{\text{GEN}} = 6 \Omega$ | Q1<br>Q2 |            | 3.1<br>1.8          | 10<br>10             | ns       |  |

| t <sub>d(off)</sub>                    | Turn-Off Delay Time                                         |                                                                                                                                       | Q1<br>Q2 |            | 35<br>21            | 56<br>34             | ns       |  |

| t <sub>f</sub>                         | Fall Time                                                   | $V_{GS} = 10$ V, $R_{GEN} = 6$ $\Omega$                                                                                               | Q1<br>Q2 |            | 1.3<br>8.5          | 10<br>17             | ns       |  |

| Q <sub>g(TOT)</sub>                    | Total Gate Charge                                           | $V_{GS} = 0 V \text{ to } 10 V$ Q1                                                                                                    | Q1<br>Q2 |            | 7.3<br>15.7         | 10<br>22             | nC       |  |

| Q <sub>g(TOT)</sub>                    | Total Gate Charge                                           | $V_{GS} = 0 V \text{ to } 4.5 V$ $I_D = 6 A$                                                                                          | Q1<br>Q2 |            | 3.1<br>7.2          | 4.3<br>10            | nC       |  |

|                                        |                                                             |                                                                                                                                       |          |            | 1                   |                      | T        |  |

©2011 Fairchild Semiconductor Corporation FDMC7200S Rev.C4

Gate to Source Charge

Gate to Drain "Miller" Charge

$\mathsf{Q}_\mathsf{gs}$

$\mathsf{Q}_{\mathsf{gd}}$

2

Q2

$V_{DD} = 15 V$  $I_{D} = 8.5 A$

Q1

Q2

Q1

Q2

1.8

3

1

1.9

nC

nC

| Symbol                             | Parameter                          | Test Conditions                                        |          | Туре | Min | Тур | Max | Units |

|------------------------------------|------------------------------------|--------------------------------------------------------|----------|------|-----|-----|-----|-------|

| Drain-Source Diode Characteristics |                                    |                                                        |          |      |     |     |     |       |

| V <sub>SD</sub> Source             |                                    | $V_{GS} = 0 V, I_{S} = 6 A$                            | (Note 2) | Q1   |     | 0.8 | 1.2 | V     |

|                                    | Source-Drain Diode Forward Voltage | $V_{GS} = 0 V, I_{S} = 8.5 A$                          | (Note 2) | Q2   |     | 0.8 | 1.2 |       |

|                                    |                                    | $V_{GS} = 0 V, I_{S} = 1.3 A$                          | (Note 2) | Q2   |     | 0.6 | 0.8 |       |

|                                    | Reverse Recovery Time              | Q1                                                     |          | Q1   |     | 13  | 24  | ns    |

| rr                                 |                                    | I <sub>F</sub> = 6 A, di/dt = 100 A/s                  |          | Q2   |     | 20  | 32  |       |

| Q <sub>rr</sub> Reverse Rec        | Davana Daarvan Channa              | Q2                                                     |          | Q1   |     | 2.3 | 10  |       |

|                                    | Reverse Recovery Charge            | $I_F = 8.5 \text{ A}, \text{ di/dt} = 300 \text{ A/s}$ |          | Q2   |     | 15  | 24  | nC    |

200

c. 180 °C/W when mounted on a minimum pad of 2 oz copper

ođ

b.50 °C/W when mounted on a 1 in<sup>2</sup> pad of 2 oz copper

d. 125 °C/W when mounted on a minimum pad of 2 oz copper

a.65 °C/W when mounted on a 1 in<sup>2</sup> pad of 2 oz copper

2. Pulse Test: Pulse Width < 300  $\ \mu s,$  Duty cycle < 2.0%.

3. Starting Q1: T = 25 °C, L = 1 mH, I = 5 A, Vgs = 10V, Vdd = 27V, 100% test at L = 3 mH, I = 4 A; Q2: T =  $25^{\circ}$ C, L = 1 mH, I = 8 A, Vgs = 10V, Vdd = 27V, 100% test at L = 3 mH, I = 3.2 A.

4. As an N-ch device, the negative Vgs rating is for low duty cycle pulse ocurrence only. No continuous rating is implied.

©2011 Fairchild Semiconductor Corporation FDMC7200S Rev.C4

FDMC7200S Dual N-Channel PowerTrench<sup>®</sup> MOSFETs

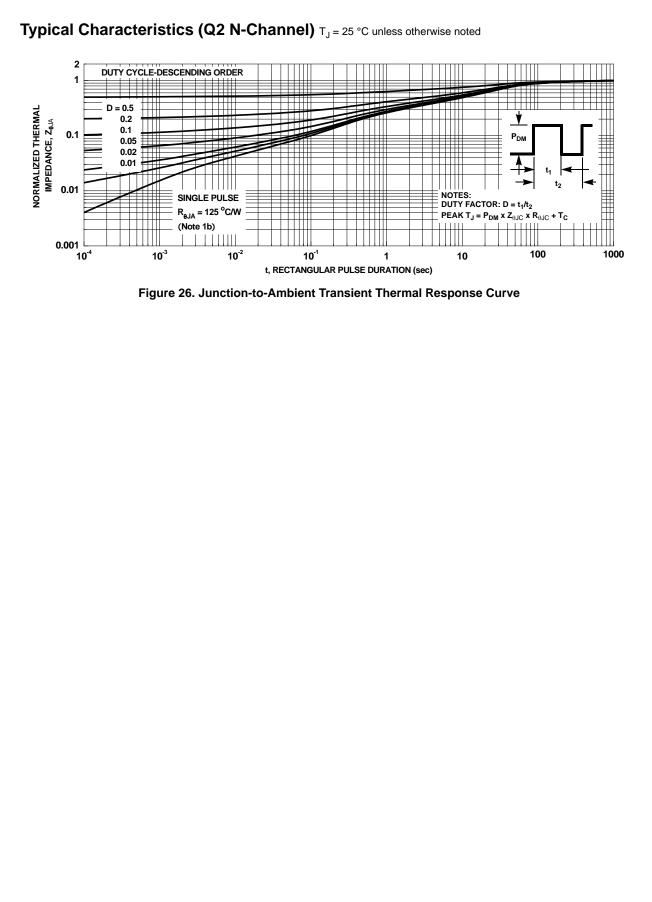

## Typical Characteristics (continued)

## SyncFET<sup>™</sup> Schottky body diode Characteristics

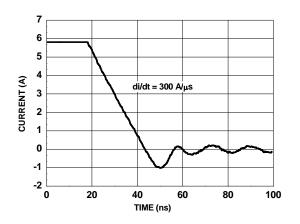

Fairchild's SyncFET<sup>TM</sup> process embeds a Schottky diode in parallel with PowerTrench<sup>®</sup> MOSFET. This diode exhibits similar characteristics to a discrete external Schottky diode in parallel with a MOSFET. Figure 27 shows the reverse recovery characteristic of the FDMC7200S.

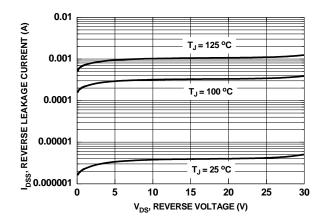

Schottky barrier diodes exhibit significant leakage at high temperature and high reverse voltage. This will increase the power in the device.

Figure 27. FDMC7200S SyncFET<sup>TM</sup> Body Diode Reverse Recovery Characteristic

Figure 28. SyncFET<sup>™</sup> Body Diode Reverse Leakage vs. Drain-source Voltage

Not In Production

Obsolete

Datasheet contains specifications on a product that is discontinued by Fairchild

Semiconductor. The datasheet is for reference information only.

Rev. 168 www.fairchildsemi.com

## **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Fairchild Semiconductor: